Thermische Oxidation von Silizium

Die thermische Oxidation von Silizium ist ein Verfahren zur Änderung der Oberflächeneigenschaften, bei dem an der Oberfläche eines Siliziumsubstrats (beispielsweise einem Silizium-Wafer) oder einer Teilstruktur aus Silizium eine dünne Schicht aus amorphem Siliziumdioxid erzeugt wird. Das Verfahren wird in der Halbleitertechnik unter anderem bei der Herstellung von mikroelektronischen Schaltungen eingesetzt. Der Prozess basiert auf der Eindiffusion von Sauerstoff und dessen chemischer Reaktion mit Silizium bei Temperaturen über 1100 °C. Bei sehr kurzen Prozesszeiten nennt man das Verfahren auch „Rapid Thermal Oxidation“ (RTO, deutsch: schnelle thermische Oxidation), das zur Erzeugung von sehr dünnen Siliziumoxidschichten (< 2 nm) dient. Ein ähnliches Verfahren ist die Erzeugung einer thermischen Siliziumnitrid-Schicht auf einem Siliziumsubstrat bei hohen Temperaturen.

Prozessbeschreibung

Die Oxidation von Silizium zu Siliziumdioxid ist eine diffusionsabhängige Festkörperreaktion. Sie läuft bereits bei Raumtemperatur unter Laborbedingungen (Wasser wird benötigt) ab, die Reaktionsgeschwindigkeit liegt jedoch weit unterhalb der Anforderungen für technische/industrielle Prozesse. Außerdem bildet sich durch die Diffusionsbegrenzung meist nur eine circa zwei Nanometer natürliche Oxidschicht.

.svg.png.webp)

Für die Oxidation von Silizium unterscheidet man im Wesentlichen zwei Verfahren: die trockene und die nasse Oxidation. Zusätzlich gibt es noch eine kleinere Zahl von ähnlichen Varianten, wie beispielsweise die H2-O2-Verbrennung. Der Oxidationsprozess aller Varianten kann zu drei Schritten zusammengefasst werden: (i) Transport der gasförmigen Ausgangsstoffe (z. B. Sauerstoff oder Wasser) zur Oberfläche des Substrat, (ii) Diffusion durch die bestehende Oxidschicht und (iii) die Oxidationsreaktion selbst. Bei der Reaktion wird Sauerstoff in das Siliziumsubstrat eingebaut, das heißt, bei diesem Prozess wird keine Schicht im eigentlichen Sinn auf ein Substrat aufgebracht, sondern das Substrat wird an der Oberfläche umgewandelt. Im Unterschied zu einer Beschichtung liegt ein Teil der späteren Schicht im Bereich des vorherigen Siliziumsubstrats. Das Silizium wird sozusagen „verbraucht“. Die entstehende Oxidschicht liegt beim thermischen Oxid zu ca. 46 % unterhalb und zu 54 % oberhalb des Ausgangssubstrates aus Silizium.

Bei den Wachstumsraten und Schichteigenschaften (Dichte, Durchschlagsfestigkeit usw.) unterscheiden sich die beiden Hauptverfahren zum Teil stark. Gemeinsam ist beiden Verfahren, dass erstens Dotierungskonzentrationen über 10−6 (entspricht 1018 Atome auf ca. 6 × 1023 Siliziumatomen, vgl. Avogadro-Konstante) die Oxidation fördern, und zweitens, dass die Oxidation von der Kristallorientierung abhängt, wobei die Oxidation von {111}-Siliziumoberflächen um 30–100 % schneller abläuft als die von {100}-Siliziumoberflächen (die Angaben {111} bzw. {100} bezeichnen dabei bestimmte Kristallflächen bzw. Flächen der Einheitszelle, vgl. Millersche Indizes und Diamantstruktur).[1]

Vor der Oxidation erfolgt, wie bei jedem Hochtemperaturprozess in der Halbleitertechnik, eine Waferreinigung. Dies dient sowohl der Verbesserung des Prozesses selbst als auch der Verhinderung einer Rohrkontamination. Mit der Reinigung sollen vor allem metallische Verunreinigungen reduziert werden, diese würden ansonsten die elektrischen Eigenschaften der Oxidschichten verschlechtern. Ein typischer Reinigungsprozess ist die RCA-2-Reinigung, die Chlorwasserstoff (HCl) zur Bindung von metallischen Verunreinigungen nutzt. HCl wird auch zur Reinigung der Ofenrohre eingesetzt, allerdings werden dazu heutzutage häufiger organische Chlorverbindungen wie 1,2-Dichlorethen (DCE) eingesetzt.[2]

Trockene Oxidation

Die Reaktion lässt sich durch hohe Temperaturen deutlich beschleunigen. Bei den hierfür üblichen Temperaturen zwischen 800 und 1200 °C oxidiert Silizium bereits, wenn man es Sauerstoff aussetzt. Dieser Prozess, bei dem die Oxidation nur durch Sauerstoff verursacht wird, nennt man auch trockene Oxidation. Die erzielte Schichtdicke ist dabei abhängig von der Temperatur und der Oxidationszeit. Mit diesem Verfahren erzeugte Schichten wachsen eher langsam auf, besitzen dafür aber eine hohe Schichtqualität.

Nasse Oxidation

Ein anderes Verfahren nutzt Wasserdampf als Oxidationsmittel, es wird daher nasse Oxidation (auch Feuchtoxidation) genannt. Dazu durchströmt ein Trägergas, häufig Sauerstoff oder ein Sauerstoff-Stickstoff-Gemisch, bevor es in den Oxidationsofen eingelassen wird, einen mit 90–95 °C warmen deionisiertem Wasser gefüllten Behälter (sogenannte bubbler). Die durch das Trägergas transportierten Wassermoleküle reagieren anschließend mit der Siliziumoberfläche:

Die Oxidationsreaktion läuft in der Regel bei Temperaturen zwischen 900 °C und 1100 °C ab. Das Schichtwachstum erfolgt hier schnell, aber mit niedrigerer Qualität als bei der trockenen Oxidation.

Weitere Prozessvarianten

Neben der thermischen Oxidation mit reinem Sauerstoff oder Wasserdampf gibt es noch weitere Verfahren, bei denen die eigentlichen Reaktionspartner für die Oxidation von Silizium erst durch eine Reaktion in der Prozesskammer gebildet werden, beispielsweise von Wasserstoff (H2) und Sauerstoff (O2),[3] Trichloressigsäure (TCA) und Sauerstoff oder Chlorwasserstoff (HCl) und Sauerstoff.[4] Diese werden in der Praxis eher selten angewendet, bieten aber zum Teil bessere Schichteigenschaften.

H2-O2-Verbrennung: Bei der H2-O2-Verbrennung (engl. pyrogenic oxidation) wird Wasser direkt in der Reaktionskammer durch die Reaktion von hochreinem Wasserstoff und Sauerstoff bei ca. 600 °C gebildet. Dazu werden die beiden Ausgangsgase (meistens zusammen mit Stickstoff) über getrennte Zuleitungen in die Prozesskammer geleitet. Hierbei muss besonders auf das Mischungsverhältnis geachtet werden, da Explosionsgefahr durch Knallgasbildung besteht. Der eigentliche Oxidationsvorgang entspricht dem der nassen Oxidation, bei der Silizium mit Wasser zu Siliziumdioxid reagiert. Durch die H2-O2-Verbrennung können Oxidschichten mit hoher Wachstumsrate, aber geringen Verunreinigungen und Defekten hergestellt werden.

Deal-Grove-Modell

Das Deal-Grove-Modell[5] ist eine häufig genutzte Beschreibung für das diffusionsbasierte Schichtwachstum von thermischem Siliziumdioxid auf einer reinen Siliziumoberfläche. Die für den Oxidationsprozess notwendige Zeit t, die notwendig ist, um eine bestimmte Schichtdicke dSiO2 zu erreichen, berechnet sich demnach wie folgt:[6]

wobei B die parabolische und der Faktor B/A die lineare Wachstumsrate bezeichnet.

Für ein Siliziumsubstrat, das bereits eine Oxidschicht besitzt, muss die Gleichung durch einen Term ergänzt werden. bezeichnet dabei die Zeit, die notwendig wäre, um die schon vorhandene Schicht unter den aktuellen Prozessparametern zu erzeugen.

Die Konstante kann auch genutzt werden, um für die Berechnung der Prozessdauer das mit dem Deal-Groove-Modell nicht beschreibbare schnelle Anfangswachstum bei der trockenen Oxidation zu berücksichtigen.

Löst man die quadratische Gleichung für dSiO2, so erhält man:

Für dünne Oxidschichten kleiner 30 nm ist das Deal-Grove-Modell nicht geeignet, da hier das Oxid zunächst schneller als erwartet wächst.[7] Zusätzlich zeigt sich häufig eine Verzögerungszeit bis der Oxidationsprozess startet. Diese Zeit ist länger als die Zeit, die es braucht, um das Gasvolumen im Oxidationsofen auszutauschen.[8]

Für die Modellierung der Wachstumsraten sehr dünner Oxidschichten werden in der Literatur unterschiedliche Ansätze verfolgt. Ein häufig genutzter Ansatz basiert auf der Erweiterung des Deal-Grove-Modells um einen zusätzlichen Term, mit dem sich die Wachstumsrate zu Beginn des Schichtwachstums beschreiben lässt (z. B.[8]).

Ein anderer Ansatz ist die Einführung einer Übergangsschicht zwischen Silizium und Siliziumdioxid. Anders als im Deal-Grove-Modell, das einen abrupten Übergang von Si zu SiO2 annimmt, wird angenommen, dass in dieser Übergangsschicht aus unstöchiometrischem Siliziumoxid (SiO0<x<2) mit einer Dicke von 1,5 nm bis 2 nm die Oxidationsreaktion stattfindet. Das Vorhandensein einer solchen Übergangsschicht konnte in XPS-Messungen experimentell bestätigt werden.[7]

Oxidationstechniken und -anlagen

Am häufigsten wird die thermische Oxidation in den Heizöfen bei Temperaturen zwischen 800 °C und 1200 °C durchgeführt. Ein einzelner Ofen nimmt in der Regel mehrere Wafer (25 bis 200) in einer Horde auf. Es gibt zwei wesentliche Ofenbauweisen, die sich in der Art und Weise, wie die Wafer gelagert werden, unterscheiden: horizontale und vertikale Öfen.[9][10] Die horizontale Bauform wird vor allem bei älteren bzw. bei Anlagen für Wafer mit Durchmessern von 150 mm und kleiner verwendet. Vertikale Öfen werden hingegen häufiger bei neueren Anlagen für Wafer mit einem Durchmesser von 200 mm bzw. 300 mm eingesetzt.

.svg.png.webp)

Bei horizontalen Öfen stehen die Wafer nebeneinander. Herabfallender Staub kann somit zwischen die Wafer gelangen und so prinzipiell jeden Wafer verschmutzen. Horizontale Öfen nutzen typischerweise einen Konvektionsstrom innerhalb des Oxidationsrohrs, daraus resultiert, dass es in der Reaktionskammer unten etwas kälter ist als oben und die Oxidschichten somit an den nach unten zeigenden Seiten der Wafer etwas langsamer wachsen; ungleichförmige Schichtdicken sind das Resultat. Dies ist bei größeren Wafern (Durchmesser größer 150 mm), wie sie heute standardmäßig eingesetzt werden, und den gestiegenen Anforderungen an die Fertigungstoleranzen nicht mehr akzeptabel. Ein Vorteil der horizontalen Öfen ist, dass mehrere Ofenrohre übereinander in einer Anlage angeordnet werden können, was etwas Platz im Reinraum einspart.

In vertikalen Öfen werden die Wafer übereinander liegend gelagert. Durch diese Anordnung kann herabfallender Staub nur auf den höchstplatzierten Wafer fallen; Staubverschmutzungen werden so minimiert bzw. verhindert. Durch die liegende Lagerung wird eine gleichmäßigere Temperaturverteilung und somit gleichförmige Schichtdicken über den einzelnen Wafer erreicht. Durch die unterschiedliche Temperaturverteilung im Ofenrohr weisen die unten gelagerten Wafer eine dünnere Schicht auf als die oberen; auch gibt es minimale Unterschiede zwischen Ober- und Unterseite eines Wafers. Diese Probleme lassen sich reduzieren, in dem man den Gasstrom dem Konvektionsstrom entgegen von oben nach unten führt.

Schichteigenschaften

| Dichte (trocken;nass oxidiert) | 2,27 g/cm3; 2,18 g/cm3 |

| Thermischer Ausdehnungskoeffizient | 5,6·10−7 K−1 |

| Elastizitätsmodul | 6,6·1010 N/m² |

| Poisson-Zahl | 0,17 |

| Wärmeleitfähigkeit | 3,2·10−3 W/(cm·K) |

| Relative Dielektrizitätskonstante | 3,7…3,9 |

| Durchschlagsfestigkeit (trocken;nass oxidiert) | ≈ 10 MV/cm; ≈ 8 MV/cm |

| Bandabstand | 8,9 eV |

Durch trockene oder nasse Oxidation hergestellte Siliziumdioxidschichten sind glasartig und weisen nur eine Nahordnung auf (→ amorph). Ihre Eigenschaften sind nahezu identisch mit denen von Quarzglas, das meist als Material für die Oxidationsrohre verwendet wird. Des Weiteren sind nicht alle Bindungen zwischen Silizium und Sauerstoff vollständig ausgebildet, dies führt zu ungebundenen, geladenen Sauerstoffatomen. Die molekulare Struktur unterscheidet sich somit deutlich von kristallinem Siliziumdioxid (Quarz), unter anderem hinsichtlich ihrer Dichte (≈ 2,2 g·cm−3 statt 2,65 g·cm−3 für Quarz) und ihrem Elastizitätsmodul (87 GPa statt 107 GPa für Quarz).[13]

Die Eigenschaften der durch thermische Oxidation hergestellten Siliziumdioxidschichten variieren in Abhängigkeit von den Prozessbedingungen. Die wichtigsten Einflussgrößen sind hierbei das Oxidationsverfahren (trocken oder nass) und die Prozesstemperatur. In Bezug auf Leistung und Zuverlässigkeit der mikroelektronischen Bauelemente und Schaltungen sind vor allem die elektrische Eigenschaften der thermischen Oxide wichtig, wie die elektrische Leitfähigkeit, Ladungsträgereinfang (engl. carrier trapping) und vorhandene Oxidladungen.

Bei der Herstellung dicker Oxidschichten wird die nasse Oxidation wegen der höheren Wachstumsrate gegenüber der trockenen Oxidation bevorzugt. Nachteilig bei der nassen Oxidation sind die schlechteren Schichteigenschaften (vor allem die elektrischen). Durch die höhere Wachstumsrate werden mehr freie Bindungen (engl. dangling bonds) an der Grenzfläche zum Silizium und auch in der Schicht selbst erzeugt; in diesem Zusammenhang wird auch von einer höheren Defektdichte gesprochen. Diese freien Bindungen wirken als Störstellen bzw. Streuzentren für Elektronen und erlauben unter anderem einen Leckstrom entlang der Grenzfläche und bewirken eine geringere elektrische Durchschlagsfestigkeit.

Im Gegensatz dazu weisen Schichten, die durch trockene Oxidation hergestellt wurden, bessere Schichteigenschaften auf. Allerdings wirkt sich die langsame Wachstumsrate negativ auf die Prozesskosten aus. In der Praxis findet man daher öfter Prozesse, die beide Methoden kombinieren, sogenannte dry-wet-dry-Zyklen. Hierbei wird das schnelle Schichtwachstum der nassen Oxidation genutzt, um die Prozesszeiten gering zu halten. Durch die Erzeugung qualitativ hochwertiger Grenzschichten mit der trockenen Oxidation am Anfang und Ende werden die negativen Eigenschaften der nassen Oxidation weitgehend aufgehoben.

Segregation

Wie bereits erwähnt, wird beim Oxidwachstum Silizium verbraucht. Da Fremdstoffe unterschiedliche Löslichkeiten in Silizium und Siliziumoxid aufweisen, können diese entweder in die Oxidschicht eingebaut werden oder im Silizium bzw. an der Grenzschicht verbleiben. Abhängig von den Löslichkeitskoeffizienten kann es daher zu einer Anreicherung () oder einer Verarmung () von Fremdatomen im Silizium an der Grenzfläche zum Oxid kommen; diese Trennung nennt man auch Segregation.[14] Für die Beurteilung dieses Vorgangs ist der sogenannte Segregationskoeffizient k maßgeblich. Damit kann die anteilige Verteilung der Fremdatome im Oxid bzw. im Silizium bestimmt werden.

Anwendung

Die thermische Oxidation von Silizium ist seit Mitte der 1950er Jahre, als die ersten Transistoren auf Basis von Silizium kommerziell hergestellt wurden, einer der wichtigsten Prozesse bei der Herstellung von mikroelektronischen Schaltungen. Damals setzte sich Silizium gegenüber Germanium als bevorzugtes Material in der Halbleitertechnik durch. Ausschlaggebend für diese Entwicklung waren unter anderem die besseren Materialeigenschaften von Siliziumdioxid im Vergleich zu Germaniumoxid, das schlechtere Haftungseigenschaften aufwies und nicht stabil gegenüber Wasser ist.

Der Prozess der thermischen Oxidation von Silizium wurde in den 1950er Jahren in den Bell Telephone Laboratories in New Jersey, wo 1947 der erste funktionierende Transistor entdeckt wurde, zufällig gefunden – Es waren aber auch andere industrielle Forschungslabore und Universitäten beteiligt. Damals war die Dotierung von Halbleitern durch Diffusion gasförmiger Dotanden (Bor, Phosphor, Arsen, Antimon) bereits bekannt. Die Prozesse wurden bei hohen Temperaturen um die 1000 °C durchgeführt. Aus Versehen mischte 1955 Carl Frosch Wasserstoff und Sauerstoff im Diffusionsrohr. Nachdem die Siliziumproben aus dem Ofen genommen worden waren, zeigten diese eine Verfärbung zu einem hellen Grün. Es stellte sich heraus, dass sich eine stabile dünne Schicht aus thermischem Siliziumdioxid bildete.[15]

Wichtige Bereiche, in denen thermisch hergestelltes Siliziumdioxid eingesetzt wurde und zum Teil immer noch wird, sind die selektive Dotierungsmaskierung, die Oberflächenpassivierung von Silizium und die elektrische Isolierung der Bauelemente in der Planartechnik. Bei der Herstellung moderner ICs wird diese Technik jedoch nur in den ersten Prozessschritten eingesetzt, beispielsweise bei der Herstellung der Grabenisolation oder Gateoxiden, die bei CMOS-Transistoren das Gate vom Silizium trennt, um darunter durch das entstehende elektrische Feld den leitenden Kanal auszubilden. Hauptgrund dafür, dass dieses Verfahren nicht zu einem späteren Zeitpunkt des Herstellungsverfahrens eingesetzt wird, ist die hohe Prozesstemperatur. Diese führen beispielsweise zur Verschiebung von Dotierungsprofilen. Aus diesem und anderen Gründen werden in allen anderen Bereichen und Fertigungsabschnitten (Isolation der Leitbahnen usw.) „Niedrigtemperaturverfahren“ wie der chemische Gasphasenabscheidung (Reaktion mit TEOS bei 600 °C) oder (selten) die Sputterdeposition genutzt. Diese erzeugen zwar ein qualitativ schlechteres Oxid, eignen sich aber auch dafür, Oxidschichten auf anderen Materialien als Silizium herzustellen.

Materialselektive Maskierung für die Diffusionsdotierung

Die Eigenschaft von Siliziumdioxid, eine materialselektive Maskierung für die Diffusion von Dotanden in Silizium zu sein, wurde zuerst 1956 von den Bell-Labs-Mitarbeitern Frosch und Derick vorgestellt.[16][17] Sie entdeckten, dass die Diffusion von n-Dotiermittel (P, As, Sb) in das Silizium bei Temperaturen über 1000 °C in einer oxidierenden Atmosphäre behindert wird. Gleiches gilt auch für das p-Dotiermittel Bor, doch im Gegensatz zu den genannten n-Dotiermitteln kann Bor in Gegenwart von Wasserstoff und Wasserdampf schneller durch das Oxid und in das Silizium diffundieren. Praktische Anwendung fand die Technik der selektiven Maskierung unter anderem bei der Herstellung des double diffused transistor bzw. des sogenannten Mesatransistors, denn er erlaubte es, den Kontakt von Emitter und Basis an einer Oberfläche zu fertigen.

Oberflächenpassivierung

Die Eigenschaften der damaligen Transistoren waren durch ihre ungeschützte Oberfläche unvorhersehbar und nicht stabil. Aus diesem Grund beschäftigte sich in der Zeit zwischen 1955 und 1960 eine Vielzahl von Forschungslaboren mit der Oberflächenpassivierung von Germanium und Silizium.[18] Eine wichtige Arbeitsgruppe forschte bei den Bell Laboratories, Martin M. Atalla und Mitarbeiter fanden heraus, dass eine spezielle Reinigung und eine nachfolgende Herstellung eines dünnen thermischen Oxids (15–30 nm) eine deutliche Reduzierung von Leckströmen bei pn-Übergängen mit sich brachte.[19] Die Ursache lag in der Bindung bzw. Neutralisierung von Oberflächenzuständen. Dies erlaubte es auch später, die Ladungsträgermobilität durch ein externes elektrisches Feld zu steuern (siehe MOSFET). Die Passivierung ermöglichte später weitere wichtige Entwicklung, hervorzuheben sind vor allem der Planarprozess und der Planardiffusionstransitor sowie die darauf basierenden integrierten Schaltkreise.

Die thermische Oxidation wird auch heutzutage noch zur Oberflächenpassivierung von einkristallinen und polykristallinen Siliziumschichten eingesetzt. Das Verfahren ist dabei nicht auf die Herstellung von mikroelektronischen Bauelementen beschränkt, sondern kann in nahezu allen Bereichen verwendet werden, die Silizium für „elektrische Anwendungen“ nutzen, beispielsweise Solarzellen[20] oder Mikrosysteme.

Bauelementisolierung

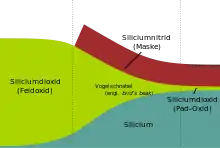

Die Bauelemente (Transistoren, Dioden) eines integrierten Schaltkreises befinden sich in der Regel an der Oberfläche eines Wafers. In den Anfangsjahren der Mikroelektronik lagen sie zunächst ausreichend weit auseinander und die Isolation der Bauelemente (Verhinderung von Leckströmen usw.) wurden durch in Sperrrichtung betriebene p-n-Übergänge realisiert. Anfang der 1970er Jahre stiegen jedoch die Leistungsanforderungen an die Schaltkreise und die Packungsdichte der Bauelemente wurde zunehmend erhöht. Die Isolation durch p-n-Übergänge war nicht mehr ausreichend. Ihren Platz nahmen vor allem Oxidisolationen ein, die nach dem LOCOS-Prozess oder ähnlichen Verfahren hergestellt wurden. Durch sie konnten die Kapazitäten und Leckströme zwischen den Bauelementen minimiert werden, darüber hinaus ermöglichten sie eine höhere Packungsdichte und sparten somit Platz auf dem Wafer. Beim LOCOS-Prozess wird Silizium nur in ausgewählten Bereichen (lokal) oxidiert. Die nicht zu oxidierenden Bereiche werden mit einem Material maskiert, das die für die thermische Oxidation benötigte Diffusion von Sauerstoff und Wasser blockiert, beispielsweise Siliziumnitrid; Die Strukturierung der ganzflächig abgeschiedenen Maskierungsschicht erfolgt fotolithografisch. Infolge Diffusion unter die Maskierungsschicht von der Seite her kann dieses Verfahren jedoch keine scharfen Grenzen, sondern nur Schichtübergänge erzeugen (vgl. „Vogelschnabel“ in LOCOS-Prozess).

In den 1990er Jahren wurden diese „LOCOS-Techniken“ durch die Grabenisolation (engl. shallow trench isolation, STI) abgelöst. Ursache dafür waren die gestiegenen Anforderungen an die Packungsdichte und an die Planarität der Oberfläche, vor allem für die fotolithografische Strukturierung in nachfolgenden Prozessschritten. Die LOCOS-Techniken hatten durch Art des Oxidwachstums bei der thermischen Oxidation (Vogelschnabel usw.) entscheidende Nachteile und Weiterentwicklungen des Prozesses, die diese Nachteile minimierten, wurden zu aufwendig und somit zu teuer.

Dennoch wird die thermische Oxidation auch bei der Isolationsherstellung aktueller ICs genutzt. Sie dient beispielsweise bei der Grabenisolation als Teilprozess zur Herstellung einer dünnen Oxidschicht mit guten elektrischen Eigenschaften, die durch TEOS- bzw. HDP-Oxide nicht erreicht werden (HDP steht hier für englisch high density plasma, dt. hochdichtes Plasma). Weiterhin existieren Verfahren zur Herstellung von Silicon-on-Insulator-Wafern (SOI-Wafern) bei dem zunächst ein thermisches Oxid auf einem Wafer erzeugt und später mit einem weiteren Wafer verbunden wird (Waferbonden).

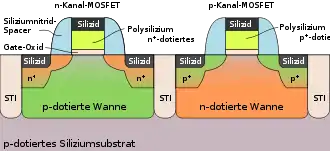

Moderne MOS-Transistoren

Die durch die thermische Oxidation von Silizium hergestellten Isolationsschichten hatten entscheidenden Einfluss auf die Realisierung der ersten Feldeffekttransistoren mit isoliertem Gate (IGFET). Das Prinzip der Feldeffekttransistoren wurde schon Ende der 1920er Jahre durch Wissenschaftler wie J. E. Lilienfeld und O. Heil beschrieben. Aufgrund damals noch nicht vorhandener Herstellungsprozesse, die ausreichend reine Halbleiterkristalle oder Isolationsschichten liefern, konnte diese Ideen damals nicht praktisch realisiert werden. Erst im Juni 1960 veröffentlichten die Bell-Labs-Mitarbeiter Dawon Kahng und Martin M. Atalla erstmals einen funktionierenden MOSFET (engl. metal-oxide-semiconductor field-effect-transistor, dt. Metall-Oxid-Halbleiter-Feldeffekttransistor).[21][22][23]

Ein MOSFET besteht aus einer dünnen Schicht von thermisch hergestelltem Siliziumdioxid auf einem p- oder n-dotierten Siliziumeinkristall und einer Metallschicht (später auch dotiertes polykristallines Silizium) über der Oxidschicht, der Gate-Elektrode. Dieser Metall-Isolator-Halbleiter-Kondensator ist ein wichtiger Teil des Feldeffekttransistors, denn über die Gate-Spannung können Elektronen oder Defektelektronen an der Silizium-Siliziumdioxid-Grenzfläche angesammelt werden, so dass sich ein leitfähiger Kanal zwischen der Source- und Drain-Elektrode bildet. Die ersten MOSFETs hatten jedoch schlecht reproduzierbare elektrische Eigenschaften und liefen teilweise nicht stabil. Trotz der Anstrengungen zahlreicher Firmen wurde die Ursache für diese Effekte erst 1965 durch Mitarbeiter der Firma Fairchild Semiconductor gefunden.[24] Natriumverunreinigungen (genauer positiv geladene Natriumionen) im Oxid und an der Grenzfläche beeinflussten die Schwellspannung und somit das elektrische Verhalten der Transistoren. Nach der Identifikation der Alkaliionen als Quelle der Instabilitäten wurde viel Zeit und Anstrengungen darauf konzentriert, diese ionischen Verunreinigungen zu analysieren, zu entfernen und zu kontrollieren. Dazu zählen unter anderem sogenannte C-V-Messungen (Kapazitäts-Spannungs-Messungen), die es erlauben, Aussagen zu möglichen Ladungen zu treffen.[25] Auch zahlreiche Verfahren für die Bindung der Ionen (Gettern)[26][27] oder der Schutzmaskierung[28] wurden entwickelt.[29]

Auch heute (2009) wird thermisch erzeugtes Siliziumdioxid von den meisten Herstellern als Gate-Material eingesetzt. Die Schichtdicken liegen dabei mittlerweile im Bereich von 1–3 nm und werden durch Rapid Thermal Oxidation hergestellt. Bei diesen geringen Schichtdicken steigen jedoch die Verluste durch Tunnelströme. Durch einen Umstieg auf Gate-Materialien mit einer höheren Dielektrizitätskonstanten als Siliziumdioxid (High-k-Dielektrikum) kann die Dicke der Isolationsschicht wieder erhöht werden, und somit können die Verluste durch Tunnelströme verringert werden.

Polysilizium und Metallsilizide

Neben der Oxidation von einkristallinem Silizium werden in der Halbleitertechnik ähnliche Verfahren auch zur thermischen Oxidation von Polysilizium und Metallsiliziden, z. B. Wolframdisilizid (WSi2), Kobaltsilizid (CoSi2), eingesetzt.

Der Prozess der thermischen Oxidation von Polysilizium ist im Wesentlichen identisch mit der von Siliziumeinkristallen. Durch die polykristalline Struktur kann bei der Oxidation nicht zwischen unterschiedlichen Kristallorientierungen unterschieden werden, und der Prozess wird durch die Dicke des Polysiliziumfilms selbst sowie durch die Größe der Polysiliziumkörner beeinflusst. Die Oxidationsraten von undotiertem Polysilizium liegen in der Regel zwischen denen von {100}- und {111}-orientierten Siliziumeinkristallen. In den meisten Anwendungen sind jedoch die Polysiliziumschichten vor der Oxidation stark dotiert, wodurch sich die Oxidationskinetik ändert. Im Fall von stark p-dotiertem Polysilizium liegen die Oxidationsraten deutlich höher; dieser durch Verunreinigungen verstärkte Effekt ist aber geringer als in Siliziumeinkristallen und bei geringen Prozesstemperaturen (< 1000 °C) am deutlichsten. Angewendet wird die thermische Oxidation von Polysilizium unter anderem bei der elektrischen Isolation von unterschiedlichen Polysiliziumschichten, wie sie in einer Vielzahl von VLSI-Anwendungen verwendet werden, beispielsweise bei dynamischen RAM, löschbaren programmierbaren Speichern (EPROM), ladungsgekoppelten Bauteilen (CCDs) oder Switched-Capacitor-Schaltungen.[30][31]

Metallsilizide werden in der Halbleitertechnik wegen ihrer hohen elektrischen Leitfahigkeit zur Kontaktierung von dotierten Siliziumbereichen (z. B. Source- und Drain-Kontakt) und Polysilizium (z. B. Gate) eingesetzt. Die Oxidation von Metallsiliziden kann beispielsweise bei MOSFETs für die elektrische Isolation der Gate-Elektrode gegenüber nachfolgenden Schichten genutzt werden. Durch die Oxidation wird das Metallsilizid in Siliziumdioxid umgewandelt. Die Wachstumskinetik der SiO2-Schicht hängt analog zur Oxidation von Silizium vom Stoffantransport und Diffusion des Oxidationsmittels (O2 oder H2O) sowie der Reaktion selbst bestimmt. Zur Herstellung gut isolierender, das heißt metallionenfreier, Oxidschichten ist eine ausreichend hohe Versorgung der Grenzfläche Siliziumoxid/Metallsilizid mit Silizium zu gewährleisten.[32]

Literatur

- Ulrich Hilleringmann: Silizium-Halbleitertechnologie: Grundlagen mikroelektronischer Integrationstechnik. 5. Auflage. Vieweg+Teubner, 2008, ISBN 3-8351-0245-1, Kapitel: Die thermische Oxidation von Silizium.

- Dieter Sautter, Hans Weinerth: Lexikon Elektronik und Mikroelektronik. Springer, 1997, ISBN 3-540-62131-8, S. 755 (eingeschränkte Vorschau in der Google-Buchsuche).

- Jan Albers: Grundlagen integrierter Schaltungen: Bauelemente und Mikrostrukturierung. Hanser Fachbuchverlag, 2006, ISBN 3-446-40686-7, Kapitel: Thermische Oxidation, S. 84–93 (eingeschränkte Vorschau in der Google-Buchsuche).

- Richard C. Jaeger: Introduction to Microelectronic Fabrication. Prentice Hall, Upper Saddle River 2001, ISBN 0-201-44494-1, Kapitel: Thermal Oxidation of Silicon.

- Sami Franssila: Introduction to microfabrication. John Wiley and Sons, 2004, ISBN 0-470-85106-6, S. 143–147.

- Marc J. Madou: Fundamentals of microfabrication. CRC Press, 2002, ISBN 0-8493-0826-7, S. 131–134.

Weblinks

- Oxide growth time calculator. Abgerufen am 22. November 2009 (englisch).

- Silicon Thermal Oxide Thickness Calculator. Abgerufen am 22. November 2009 (Online-Rechner inklusive Deal-Grove- und Massoud-Oxidationsmodell, englisch).

Einzelnachweise

- Howard R. Huff, David C. Gilmer: High dielectric constant materials. Springer, 2005, ISBN 3-540-21081-4, S. 67 f. (eingeschränkte Vorschau in der Google-Buchsuche).

- Sami Franssila: Introduction to microfabrication. John Wiley and Sons, 2004, ISBN 0-470-85106-6, S. 315.

- Ulrich Hilleringmann: Silizium-Halbleitertechnologie: Grundlagen mikroelektronischer Integrationstechnik. 5. Auflage. Vieweg+Teubner, 2008, ISBN 3-8351-0245-1, S. 31.

- W. Ahmed, E. Ahmed, D. G. Armour: A comparative investigation of the oxidation of silicon using H2/O2, TCA/O2 and HCl/O2 mixtures. In: Advanced Materials for Optics and Electronics. Band 2, Nr. 4, 1993, S. 165–173, doi:10.1002/amo.860020403.

- B. E. Deal, A. S. Grove: General Relationship for the Thermal Oxidation of Silicon. In: Journal of Applied Physics. Band 36, Nr. 12, 1965, S. 3770–3779, doi:10.1063/1.1713945.

- M. Liu, et al.: Two-dimensional modeling of the self-limiting oxidation in silicon and tungsten nanowires. In: Theoretical and Applied Mechanics Letters. 6, Nr. 5, 2016, S. 195–199. doi:10.1016/j.taml.2016.08.002.

- Alexandra Ludsteck: Optimierung von Gate-Dielektrika für die MOS-Technologie. ( [abgerufen am 14. Mai 2010] Dissertation; Universität der Bundeswehr München, Fakultät für Elektrotechnik und Informationstechnik, 2005).

- Hisham Z. Massoud: Growth Kinetics and Electrical Properties of Ultrathin Silicon Dioxide Layers. In: Howard R. Huff, H. Iwai, H. Richter (Hrsg.): Silicon Materials Science and Technology X. The Electrochemical Society, 2006, ISBN 978-1-56677-439-0 (eingeschränkte Vorschau in der Google-Buchsuche).

- Comparison Vertical vs. Horizontal Furnaces. Crystec Technology Trading GmbH, abgerufen am 20. Dezember 2009 (Abbildungen von Vertikal- und Horizontalöfen des Herstellers Koyo Thermo Systems Co., Ltd.).

- Semiconductor and Solar Thermal Processing Solutions. (Nicht mehr online verfügbar.) Coastal Technologies LLC, archiviert vom Original am 15. Juli 2010; abgerufen am 20. Dezember 2009 (Abbildungen von Vertikal- und Horizontalöfen des Herstellers Coastal Technologies LLC).

- Die Angaben sind nur Richtwerte und können in Abhängigkeit von den Prozessparametern variieren.

- Badih El-Kareh: Fundamentals of semiconductor processing technology. Springer, 1994, ISBN 0-7923-9534-4, S. 40.

- Sami Franssila: Introduction to microfabrication. John Wiley and Sons, 2004, ISBN 0-470-85106-6, S. 145.

- Thomas Giebel: Grundlagen der CMOS-technologie. Vieweg+Teubner Verlag, 2002, ISBN 3-519-00350-3, S. 115 (eingeschränkte Vorschau in der Google-Buchsuche – Darstellung des Segrationsverhaltens von Bor, Phosphor und Arsen).

- H. R. Huff, U. Gosele, H. Tsuya: Semiconductor Silicon. Electrochemical Society, 1998, ISBN 1-56677-193-5, S. 179–189.

- C. J. Frosch, L Derick: Surface Protection and Selective Masking during Diffusion in Silicon. In: Journal of The Electrochemical Society. Band 104, Nr. 9, 1957, S. 547, doi:10.1149/1.2428650.

- Patent US2804405: Manufacture of silicon devices. Angemeldet am 24. Dezember 1954, veröffentlicht am 27. April 1957, Erfinder: L. Derick, C. J. Frosch.

- Chih-Tang Sah: Evolution of the MOS transistor - From conception to VLSI. In: IEEE Proceedings. Band 76, 1988, S. 1280–1326.

- Patent US2899344: Angemeldet am 30. April 1958, veröffentlicht am 11. August 1959, Erfinder: M. M. Atalla, E. J. Scheibner, E. Tannenbaum.

- Stefan W. Glunz, Frank Feldmann: SiO2 surface passivation layers – a key technology for silicon solar cells. In: Solar Energy Materials and Solar Cells. Band 185, 1. Oktober 2018, ISSN 0927-0248, S. 260–269, doi:10.1016/j.solmat.2018.04.029 (sciencedirect.com [abgerufen am 4. März 2021]).

- D. Kahng, M. M. Atalla: Silicon-silicon dioxide field induced surface devices. In: IRE-AIEE Solid-state Device Res. Conf., (Carnegie Inst. of Technol., Pittsburgh, PA). 1960.

- Patent US3102230: Electric field controlled semiconductor device. Angemeldet am 31. Mai 1960, veröffentlicht am 27. August 1963, Erfinder: D. Kahng.

- Patent US3056888: Semiconductor triode. Angemeldet am 17. August 1960, veröffentlicht am 2. Oktober 1962, Erfinder: M. M. Atalla.

- E. H. Snow, A. S. Grove, B. E. Deal, C. T. Sah: Ion Transport Phenomena in Insulating Films. In: Journal of Applied Physics. Band 36, Nr. 5, April 1965, S. 1664–1673, doi:10.1063/1.1703105.

- L.M. Terman: An investigation of surface states at a silicon/silicon oxide interface employing metal-oxide-silicon diodes. In: Solid-State Electronics. Band 5, Nr. 5, 1962, S. 285–299, doi:10.1016/0038-1101(62)90111-9.

- D. R. Kerr, J. S. Logan, P. J. Burkhardt, W. A. Pliskin: Stabilization of Si02 Passivation Layers with P2O5. In: IBM Jr. of Res. and Dev. Band 8, Nr. 4, 1964, S. 376–384.

- R. J. Kriegler, Y. C. Cheng, D. R. Colton: The Effect of HCl and Cl2 on the Thermal Oxidation of Silicon. In: Journal of The Electrochemical Society. Band 119, Nr. 3, Februar 1972, S. 388–392, doi:10.1149/1.2404208.

- J. V. Dalton, J. Drobek: Structure and Sodium Migration in Silicon Nitride Films. In: Journal of The Electrochemical Society. Band 115, Nr. 8, 1968, S. 865–868, doi:10.1149/1.2411450.

- A. H. Agajanian: MOSFET Technologies: A Comprehensive Bibliography. Plenum, New York 1980.

- Mohamed Gad-el-Hak: The MEMS handbook. CRC Press, 2002, ISBN 978-0-8493-0077-6, S. 15-6 f.

- Roland Albert Levy: Microelectronic materials and processes. Springer, 1989, ISBN 978-0-7923-0154-7, S. 97 f.

- Friedemann Völklein,Thomas Zetterer: Praxiswissen Mikrosystemtechnik. Vieweg+Teubner, Wiesbaden 2006, ISBN 978-3-528-13891-2, S. 53.