LOCOS-Prozess

LOCOS, kurz für englisch local oxidation of silicon (dt. »lokale Oxidation von Silicium«), ist in der Halbleitertechnik ein Verfahren zur elektrischen Isolation von Halbleiterbauelementen, beispielsweise Transistoren. Dafür wird der Silicium-Wafer an ausgewählten Stellen maskiert, das heißt mit einer strukturierten Schutzschicht versehen, und das freigelegte Silicium anschließend örtlich begrenzt oberflächennah bei hohen Temperaturen einer sauerstoffreichen Atmosphäre oxidiert, vgl. thermische Oxidation von Silicium. Auf diese Weise entsteht an der Substratoberfläche zwischen den elektrisch aktiven Siliciumgebieten für die Bauelemente ein elektrischer Isolationsbereich aus Siliciumdioxid.

Der LOCOS-Prozess war in der Halbleitertechnik lange Zeit das bevorzugte Verfahren für die Herstellung der genannten Isolationsbereiche. Da das Verfahren jedoch relativ platzintensiv ist und weitere Nachteile mit sich bringt (siehe unten), wurde es Mitte der 1990er Jahre in der industriellen Produktion von hochintegrierten Schaltkreisen, das heißt mit Strukturgrößen um 0,25 µm und kleiner, durch die sogenannte Grabenisolation abgelöst.

Hintergrund

Isolation von Bauelementen

Eine der Haupttriebkräfte der Mikroelektronik ist eine stetig steigende Integrationsdichte der aktiven Bauelemente auf einem Substrat, das heißt, sowohl die Bauelemente als auch die Räume dazwischen werden von Generation zu Generation kleiner. Diese zunehmende Verkleinerung führt neben herstellungsbedingten Problemen auch zu elektrischen Problemen, wie beispielsweise das Übersprechen von Signalen auf Leiterbahnen oder steigende Leckströme aufgrund des geringeren Isolationsabstandes. Diese Problematik hat in der Entwicklungsgeschichte zu verschiedenen Isolationstechniken und deren Anwendung bei integrierten Schaltungen geführt, wozu die LOCOS-Technik gehört.

Vor der Entwicklung der Planartechnik wurden Transistoren und Dioden üblicherweise als Mesabauelemente (vgl. Mesatransistor) gefertigt. Trotz der relativ weit voneinander entfernten und quasi freistehenden Bauelemente war schon damals die Reduzierung der relativ großen oberflächlichen Leckströme, beispielsweise verursacht durch Grenzflächenladungen, eine der wichtigen Herausforderungen. Bereits 1959 stellte eine Arbeitsgruppe um Martin M. Atalla eine Technik vor, bei der diese Leckströme durch ein direkt auf einem Silicium-Substrat thermisches gewachsenes Siliciumdioxid drastisch reduziert werden konnten.[1] Dies bildete die Grundlage des heute als LOCOS-Prozess bekannten Verfahrens, das ab 1966 von E. Kooi am Philips Natuurkundig Laboratorium entwickelt wurde.[2][3]

Der Planar- und der Planox-Prozess

Die Entdeckung der (elektrischen) Oberflächenpassivierung führte wenige Jahre später zum industriellen Einsatz dieser Technik.[4] Dabei wurde auf dem mittlerweile standardmäßig eingesetzten Siliciumsubstrat (Silicium-Wafer) ein ganzflächiges Feldoxid aufgebracht (thermische Oxidation). Um die gewünschten Transistor- und Diodenelemente zu fertigen, wurde das Siliciumdioxid anschließend an entsprechenden Stellen nasschemisch geätzt (strukturiert), so dass das Siliciumsubstrat für die Diffusion- oder Implantation-Prozesse zugänglich ist. Diese Vorgehensweise hat jedoch einige entscheidende Nachteile. An den bei der Strukturierung des Oxids entstehenden Stufen (damals im Bereich von 1,5 µm) kann sich beispielsweise Fotolack, der bei der fotolithografischen Strukturierung für nachfolgende Prozessschritte genutzt wird, ansammeln und so das Auflösungsvermögen verringern. Da das nasschemische Siliciumdioxidätzen ein isotroper Ätzprozess ist (die Ätzung ist in alle Raumrichtungen gleich) sind Lackmaskenanpassungen als Ausgleich für die Unterätzungen notwendig. Ein weiteres Problem ist die begrenzte Konformität der Metallisierung an den Stufenkanten. Dadurch treten Leiterbahneneinschnürungen auf und die damit verbundene lokale Erhöhung der Stromdichte führt zu Schäden und einer vorzeitigen Alterung durch Elektromigration – das bis zur Jahrtausendwende verwendete Leiterbahnmaterial Aluminium ist für Elektromigration relativ „anfällig“. Um die Packungsdichte der mikroelektronischen Schaltungen weiter zu erhöhen, also möglichst viele Bauelemente auf möglichst geringer Fläche unterzubringen, war es notwendig, eine möglichst glatte Topografie zu erreichen, das heißt, die Stufen und Unebenheiten zu vermeiden beziehungsweise zu reduzieren.

Eine erste Verbesserung zeigte der von F. Morandi 1969 vorgestellte „Planox“-Prozess[5][6]. Dabei wurde bereits der Umstand ausgenutzt, dass eine Siliciumnitridschicht das darunter befindende Siliciumsubstrat vor der Oxidation schützt. Beim Planox-Prozess wurde daher zunächst eine Siliciumnitridschicht ganzflächig auf dem Siliciumwafer abgeschieden, anschließend fotolithografisch strukturiert und das Nitrid geätzt. Danach folgte die Oxidation des Wafers in einem Ofen, bis das Oxid in den unmaskierten Bereichen etwas über die Höhe der Nitridschicht gewachsen ist. Nun wurde das Nitrid mit heißer Phosphorsäure selektiv geätzt, um die Bereiche freizulegen in denen sich später die aktiven Gebiete der Transistoren befinden. In einem zweiten Oxidationschritt wurde dieser Bereich auf das Niveau der Isolationsbereiche gebracht, dies ist möglich, da die Oxidschicht bei dünneren Schichtdicken deutlich schneller wächst. Mit diesem Prozess konnten Bauelemente hergestellt werden, bei denen das circa 2 µm dicke Oxid weitgehend im Siliciumsubstrat lag und die höchste Stufe nur ungefähr 0,5 µm betrug.

Dennoch brachte erst die 1970 von Appels et al.[7] vorgestellte Technik der lokalen Oxidation von Silicium (LOCOS) den Durchbruch. Die LOCOS-Technik ist dem Planoxprozess sehr ähnlich und schafft diesen Einschränkungen des Planarprozesses Abhilfe, indem die Übergänge zwischen den Schichten weniger abrupt ausgeführt wurden.

Verfahren

Bei der LOCOS-Technik wird ein zur Planox-Technik entgegengesetzter Ablauf genutzt. Dabei werden die Bereiche freigelegt, in denen sich das spätere Isolationsoxid befinden soll. Als Maske für den strukturierten Oxidationsprozess dient eine Siliciumnitridschicht (Si3N4-Schicht), die mit den gewöhnlichen Ätztechniken strukturiert wird. Im Vergleich zu Silicium verläuft die Oxidation von Siliciumnitrid um einige Größenordnungen langsamer, so dass hier quasi keine Beeinflussung durch den Oxidationsprozess stattfindet. Die Hochtemperaturbelastung durch den Oxidationsprozess führt zu Verspannungen zwischen dem Siliciumsubstrat und der Siliciumnitridmaske, daher ist eine Zwischenschicht aus Siliciumoxid (Padoxid genannt) notwendig, um die Verspannungen zu entschärfen und so ein Abplatzen der Nitridschicht zu verhindern.

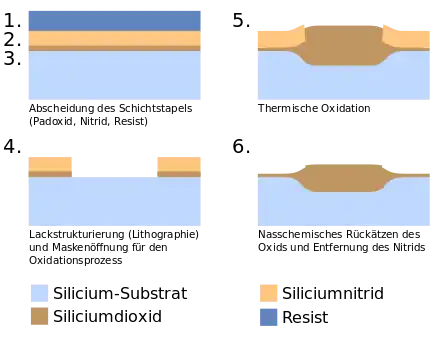

Ein typischer LOCOS-Prozess setzt sich aus den nachfolgenden Schritten zusammen:

- Vorbereitung der Siliciumsubstrate: Dazu zählt üblicherweise die Entfernung von Partikeln und organischen Verunreinigungen was beispielsweise durch eine RCA-Reinigung erfolgen kann.

- Abscheidung einer 10–20 nm dünnen Siliciumdioxidschicht: Sie dient als Puffer gegen mechanische Verspannungen. Diese treten zwischen dem Siliciumsubstrat und der Siliciumnitridschicht (Maske, siehe 3.) durch den höheren thermischen Ausdehnungskoeffizienten und der hohen Temperaturbelastung durch den thermischen Oxidationsprozess auf. Dies würde unter anderem zu Kristallbaufehlern führen. Die Oxidschicht wird daher Pad- oder Puffer-Oxid genannt und durch einen CVD-Prozess aus der Gasphase abgeschieden, oft ein TEOS-Oxid.

- Abscheidung einer 100–200 nm dicken Siliciumnitridschicht, die durch den Oxidationsprozess chemisch kaum beeinflusst wird und die maskierten Bereiche vor der Oxidation schützt. Die Herstellung erfolgt im Allgemeinen über einen LPCVD-Prozess.

- Fotolithografische Strukturierung und Ätzen der Nitrid- und Oxidschicht, so dass das Siliciumsubstrat für den Oxidationsprozess zugänglich ist

- Thermisches Aufwachsen von SiO2 auf Silicium in den nicht maskierten Bereichen. Die thermische Oxidation ist im engeren Maß keine Beschichtung, sondern eher eine Schichtmodifikation. Dabei reagiert Sauerstoff mit dem reinen Siliciumsubstrat zu Siliciumdioxid. Zwei Effekte sind wesentlich: zum einen wird dabei Silicium „verbraucht“, sodass die entstehende Oxidschicht zum Teil in den Bereich des Substrat wächst, zum anderen kommt es durch die starke Einlagerung von Sauerstoff und Kristallmodifizierung zu einem Volumenwachstum, sodass etwa 55 Prozent der gewünschten Oxidschichtdicke im vorherigen Siliciumsubstrat liegt. Ein weiterer Effekt ist die seitliche Sauerstoffdiffusion unter die nitridmaskierten Bereiche (vgl. Vogelschnabel).

- Entfernung der Nitridmaske durch nasschemisches Ätzen mit Phosphorsäure bei 150–175 °C. Anschließend kurzes Ätzen des Padoxids mit gepufferter HF-Lösung (engl. buffered oxide etch, BOE). Durch die Oxidätzung wird weiterhin der Übergang weiter eingeebnet und die Ausdehnung des Vogelschnabels verringert.

Vor- und Nachteile

Im Vergleich zu der vorher eingesetzten Planox-Technik hat die LOCOS-Technik einige entscheidende Vorteile. Bei LOCOS werden die scharfen Kanten und Stufen in der Topografie der Oberfläche deutlich reduziert. Dies erlaubt einen verbesserten Fotolackauftrag in nachfolgenden Prozessen und eine bessere Konformität der metallischen Leiterbahnen, das heißt wesentlich geringere Einschnürungen der Leiterbahnen und somit eine geringere Gefahr von Verbindungsproblemen, keine lokalen Widerstandserhöhungen und eine geringe Elektromigrationsanfäligkeit. So konnten die minimal herstellbaren Strukturgrößen gegenüber der damals herkömmlichen Planartechnik bis circa 1 µm reduziert werden.

Durch das Wachstum des Oxids während der thermischen Oxidation in die Tiefe, ragt die isolierende Oxidbarriere deutlich in das Substrat, was das Übersprechen der benachbarten Transistoren behindert, das heißt, die elektrische Isolation der aktiven Bauelemente auf dem Substrat wird verbessert.

Nachteilig am LOCOS-Prozess sind die weiterhin nicht planare Topografie nach der Oxidation, die Ausbildung eines Übergangsbereichs vom oxidierten zum nichtoxidierten Bereich, dem sogenannten Vogelschnabel, und die Abscheidung einer Siliciumnitridschicht an der Grenzfläche zum Siliciumsubstrat, der White-Ribbon-Effekt. Vor allem der entstehende Vogelschnabel begrenzt die praktisch erreichbare Integrationsdichte der Bauelemente und die nicht planare Topografie erschwert die nachfolgenden Fotolithografieschritte, da sie den gleichmäßigen Auftrag von Fotolack behindert und den für die Belichtung notwendigen Fokus lokal ändert. Unter anderem aus diesen Gründen wurden zahlreiche Weiterentwicklungen des ursprünglichen LOCOS-Prozesses in der Industrie entwickelt, die die parasitären Effekte verringern und eine höhere Integration der Schaltkreise ermöglichen, siehe Abschnitt Weiterentwicklungen. Einige dieser Techniken sind jedoch deutlich komplexer und so mit kostenintensiver, zudem können sie die Nachteile nur abmildern und nicht ganz entfernen. Deshalb setzte sich in den 1990er-Jahren eine alternative Technik durch, die Grabenisolation (engl. shallow trench isolation, STI, oder engl. box isolation technique). Dabei werden tiefengeätzte Gräben durch Abscheiden aus der Gasphase mit Siliciumoxid aufgefüllt (typischerweise TEOS- oder HDP-SiO2-CVD). Dies ist mit dem thermischen Oxid der LOCOS-Technik nicht möglich, da die Volumenänderung während des Oxidwachstums zu hohe mechanische Spannungen im Graben erzeugt und zu Defekten führt. Die Grabenisolation erlaubt im Vergleich zu LOCOS-Technik eine deutlich bessere seitliche Isolation (auch in tiefere Regionen) und ist zudem noch platzsparender herzustellen, was wiederum eine höhere Packungsdichte ermöglicht.

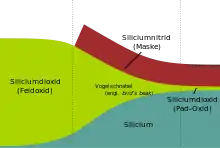

Vogelschnabel

Wie schon in der kurzen Prozesszusammenfassung erwähnt, wächst das Siliciumdioxid während der thermischen Oxidation unter den Rand der eigentlich maskierten Bereiche. Ursache dafür ist die isotrope und damit auch seitliche Sauerstoffdiffusion sowohl im LOCOS-Oxid als auch im Padoxid. Es entsteht eine für den LOCOS-Prozess charakteristische Oxidstruktur, deren Rand bis zu einem Mikrometer unter der Nitridschicht ausläuft und aufgrund ihres Profils Vogelschnabel (engl. bird’s beak) genannt wird.

Bei fortschreitender Oxidation kommt es durch das Wachstum der Oxidschicht an den Kanten der maskierten Bereiche zu einer Verbiegung (vom Substrat weg) der Nitridmaske. Da aufgrund der unterschiedlichen Gitterabstände die mechanischen Verspannungen während des Prozesses bei einem direkten Kontakt zwischen Silicium und Siliciumnitrid zu groß wären – die Nitridschicht würde durch die Verbiegung abplatzen – ist das Padoxid als Puffer notwendig.

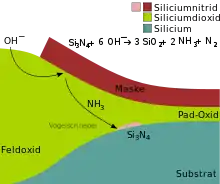

White-Ribbon- oder Kooi-Effekt

Der White-Ribbon- beziehungsweise Kooi-Effekt, benannt nach E. Kooi, einem Mitentwickler der LOCOS-Technik, ist ein parasitärer Effekt beim LOCOS-Prozess.[8] Er beschreibt die Entstehung einer dünnen Siliciumnitridschicht zwischen dem Pad-Oxid und dem Siliciumsubstrat im auslaufenden Gebiet des Vogelschnabels. Diese zeichnet sich bei Untersuchungen mittels Hellfeldmikroskopie als weißliches Band (engl. white ribbon) ab. Diese unerwünschte Schichtbildung tritt hauptsächlich bei einer Schicht aus der sogenannten nassen Oxidation auf. Diese Methode wird standardmäßig für dickere Oxidschichten genutzt, da sie im Vergleich zur trockenen Oxidation in sauerstoffreicher Atmosphäre ohne Wasserdampf ein schnelleres Schichtwachstums zeigt. Dies bietet bei den langen Prozesszeiten dicker Oxidschichten vor allem ökonomische Vorteile.

Die nasse Oxidation wird in einer mit Wasserdampf angereicherten Atmosphäre bei Temperaturen über 1100 °C durchgeführt. Hier führt die Diffusion von Hydroxidionen (OH−) durch die Siliciumnitridschicht zu einer geringfügigen Oxidation der Siliciumnitridschicht an der Pad-Oxidseite. Als Reaktionsprodukt dieser Oxidation entsteht unter anderem Ammoniak. Das Ammoniak diffundiert wiederum durch das Padoxid zum Siliciumsubstrat. Infolge der hohen Temperaturen kommt es zur thermische Nitridation des Siliciums, das heißt, Ammoniak reagiert mit dem Silicium zu Siliciumnitrid, und es bildet sich die von Kooi beobachtete Siliciumnitridschicht zwischen dem Padoxid und dem Suliciumsubstrat.

Der Effekt tritt nur im Bereich des Vogelschnabels auf, da hier die Oxidationsrate des Siliciums niedrig und der Diffusionsweg des Ammoniaks kurz ist. Im Hinblick auf den Gesamtprozess der Schaltkreisherstellung muss diese Nitridansammlung vor dem folgenden Oxidationsschritt für das sogenannte Gate-Oxid, das als Dielektrikum beim MISFET genutzt wird, entfernt werden, da sie das Oxidwachstum behindert beziehungsweise verhindert.

Weiterentwicklungen

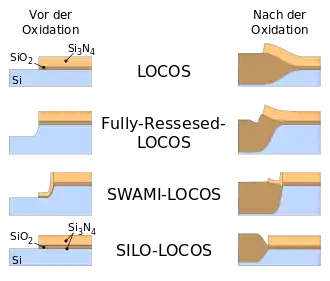

Der Vogelschnabel- und der White-Ribbon-Effekt sowie die nicht mehr ebene Topographie nach der Oxidation sind die wesentlichen Nachteile der Standard-LOCOS-Technik. Aus diesem Grund wurde die Weiterentwicklungen schnell vorangetrieben und zahlreiche Varianten entwickelt, um durch eine abgewandelte Prozessfolge ein oder mehrere dieser Nachteile reduzieren. Die wichtigsten Weiterentwicklungen sind:[9][10]

- semi recessed LOCOS und fully recessed LOCOS

- SPOT (engl. self-aligned planar oxidation technology, auch super planar oxidation technology)

- SILO (engl. sealed interface local oxidation)

- Polysilicium gepuffertes LOCOS

- SWAMI (engl. side wall mask isolatated)[11]

- FUROX (engl. FUlly Recessed Oxide)[12]

Fully-recessed LOCOS

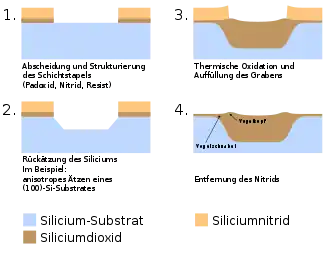

Der Fully-recessed-LOCOS-Prozess[13] (engl. fully recessed, dt. ‚voll zurückgesetzt‘) ist eine vergleichsweise einfache Möglichkeit die Oberflächentopografie weiter einzuebnen und das Feldoxid tiefer in das Substrat einzubringen. Dazu wird nach der Strukturierung (1) des Padoxid-Nitrid-Schichtstapels das Siliciumsubstrat anisotrop zurückgeätzt (2). Dabei entstehen Gräben im Silicium, deren Tiefe ungefähr 50 % späteren Feldoxiddicke beträgt. Für die Ätzung gibt es unterschiedliche Varianten, sie kann beispielsweise mit Salpetersäure-Fluorwasserstoffsäure-Lösung nasschemisch isotrop, mit einer Kaliumhydroxid-Lösung nasschemisch anisotrop oder per Trockenätzen erfolgen. Anschließend folgt der thermische Oxidationsschritt (3), wobei das Oxid wiederum 45 % in das Siliciumsubstrat und zu 55 % nach oben wächst. Dabei füllt es den geätzten Graben auf. Nach der Oxidation wird die Siliciumnitridmaske entfernt (4) und es entsteht eine relativ ebene Oberfläche.

Der Hauptvorteil des Fully-recessed-LOCOS-Prozess’ sind die guten elektrischen Isolationseigenschaften, z. B. einem niedrigen Leckstrom im Aus-Zustand bei Feldeffekttransistoren. Sie resultieren vor allem aus der größeren Isolationslänge, das heißt die Länge der Si-SiO2-Grenzfläche von einem aktiven Gebiet zum nächsten. Nachteilig ist eine etwas vergrößerte Länge des Vogelschnabels und der Bildung von „Vogelköpfen“ (engl. bird’s head) an den Seitenbereichen. Letzteres stellt eine erhöhte Topographie dar und kann wiederum zu Komplikationen beider Stufenüberdeckung während der Metallisierung führen.

SPOT-Technik

Die SPOT-Technik[14] stellt eine Möglichkeit dar, auf Basis des Standard-LOCOS-Verfahrens eine sehr ebene Topografie nach der Oxidation zu erhalten. Im Wesentlichen wird dazu der LOCOS-Prozess doppelt durchgeführt.

Zunächst wird nach der Feldoxidation das Feldoxid wieder vollständig durch nasschemisches Ätzen entfernt. Durch die Wahl eines geeigneten Ätzers mit hoher Ätzselektivität zwischen Siliciumoxid und Siliciumnitrid bleibt dabei das Maskierungsnitrid quasi unverändert. Nach der Ätzung erfolgt eine kantenkonforme ganzflächige Nitridabscheidung, das heißt, die Nitridschicht überall gleich dick, auch in den Bereichen der nach der Ätzung frei liegenden Unterseite des durch den Vogelschnabel hochgedrückten Maskennitrids. Vor der Oxidation muss jedoch diese zweite Nitridschicht wieder großflächig entfernt werden. Einzig an den Rändern des bei der ersten Oxidation entstandenen Vogelschnabels soll sie die Diffusion unter das Maskennitrid begrenzen, so dass sich der Vogelschnabel bei der folgenden Oxidation nicht weiter unter das Maskennitrid ausbreiten kann. Dieser anisotrope Ätzschritt erfolgt durch reaktives Ionenätzen des Nitrids. Nun folgt ein weiterer Oxidationsschritt bestehend aus einer kurzen Padoxidation und einer nassen thermischen Oxidation für das Feldoxid. Nachdem die erforderliche Schichtdicke erreicht wurde, können nun gemäß dem Standardprozess die Nitridschichten entfernt werden.

Das Endergebnis ist eine nahezu plane Waferoberfläche, die jedoch weiterhin einen Übergangsbereich (Teil des Vogelschnabels) zwischen dem aktiven Gebiet und der Oxidationswanne aufweist. Auch treten weiterhin parasitäre Effekte (White-Ribbon-Effekt etc.) auf. Durch die zusätzlichen Prozessschritte ist das Verfahren zudem wesentlich zeit- und kostenintensiver.

SILO-Technik

Die SILO-Technik[15] (SILO = engl. sealed interface local oxidation, dt. „lokale Oxidation mit versiegelter Grenzfläche“) wurde gezielt für die Unterdrückung des Vogelschnabels und des White-Ribbon-Effekts entwickelt.

Im Unterschied zum konventionellen LOCOS-Verfahren wird beim SILO-LOCOS-Verfahren die Oberfläche zunächst mit einer etwa 4–10 nm dünnen Schicht aus thermischen Siliciumnitrid (Si3N4) überzogen. Die thermische Nitridierung ist vergleichbar mit der thermischen Oxidation von Silicium. Sie erfolgt beispielsweise unter einer Ammoniakatmosphäre (NH3) bei etwa 1200 °C. Dabei reagiert Silicium mit Ammoniak zu Siliciumnitrid und Wasserstoff (H2)

Die beim konventionellen LOCOS-Verfahren kritischen Spannungen in der Nitridschicht sind aufgrund der geringen Dicke zu tolerieren und beeinflussen die nachfolgenden Prozesse nicht negativ. Im zweiten Schritt wird das Nitrid mit einem Padoxid und einer dicken CVD-Nitridschicht überzogen. Anschließend erfolgt die Strukturierung des gesamten Schichtstapels mit einer Fotolackmaske und dem reaktiven Ionenätzen.

Die thermische Nitridschicht soll die Siliciumoberfläche während der Feldoxidation vor der Sauerstoffdiffusion unter die Strukturkanten schützen. Der relativ komplexe Aufbau der Maskierungsschicht ist notwendig, da die dünne Nitridschicht während der Feldoxidation vollständig oxidieren würde und somit allein nicht als Maske genutzt werden kann. Der Herstellungsaufwand erhöht sich durch eine zusätzlich erforderliche CVD-Oxidabscheidung nochmals um zwei Prozessschritte.

Die durch die SILO-Technik erreichten Eigenschaften sind gut, denn sowohl die Ausbildung des Vogelschnabels (Reduktion um bis zu 65 %) als auch des White-Ribbon-Effekts kann durch die Versiegelung mit der thermischen Nitridschicht gut unterdrückt werden. In Hinsicht auf die Topografie nach der Oxidation, bringt die SILO-Technik keine Vorteile gegenüber der konventionellem LOCOS-Verfahren, das heißt, es entsteht ebenfalls eine Stufe von etwa 55 % der Feldoxiddicke.

Um die Belastungen durch die thermische Nitridierung zu reduzieren, kann es alternativ durch ein LPCVD-Nitrid ersetzt werden. Dies ist möglich da sich zwischen der Siliciumoberfläche und dem Nitrid unvermeidlich ein natürliches Oxid als Padoxid befindet und als Haftvermittler dient.

Polysilicium-gepufferte LOCOS-Technik

Die Ausprägung des Vogelschnabels kann bei der konventionellen LOCOS-Technik durch die Verringerung der Schichtdicke des Padoxids bzw. der Erhöhung der Schichtdicke des Maskennitrids erreicht werden. Dies verursacht jedoch zusätzlichen mechanischen Stress bei der Oxidation und birgt die Gefahr, dass sich beispielsweise die Nitridschicht ablösen kann. Die Polysilicium-gepufferte LOCOS-Technik[16][17] (engl. poly-buffered LOCOS, PBL) ist eine Weiterentwicklung, die gezielt an diesem Punkt ansetzt und vor allem die Reduzierung des Vogelschnabels und des White-Ribbon-Effekts zum Ziel hat.

Dabei wird zwischen dem Pufferoxid und der Nitridschicht eine zusätzliche 20–50 nm dicke Schicht aus Polysilicium eingefügt, sie dient teilweise als Opferschicht und wird nach dem Prozess wieder vollständig entfernt. Durch die zusätzliche Schicht wird zum einen der mechanische Stress in der Nitridmaske zum anderen die Ausdehnung des Vogelschnabels verringert. Die Polysiliciumschicht nimmt während der Oxidation Sauerstoff stärker auf als das Siliciumsubstrat (kürzerer Diffusionsweg, höhere Diffusionsgeschwindigkeit). Dadurch steht in diesem Bereiche weniger Sauerstoff für die Oxidation des Substratmaterials zur Verfügung. Die Folge ist, dass weniger Substrat verbraucht wird. Durch den geringeren mechanischen Stress in der Nitridschicht, können dünnere Padoxid- und dickere Nitridschichten genutzt werden, die ebenfalls zur Verringerung des Vogelschnabels beitragen und sich positiv auf die Strukturtreue auswirkt.

Negativ für den Einsatz der Polysilicium-gepufferten LOCOS-Technik sind die zusätzlichen Prozessschritte für die Herstellung und Entfernung der nichtoxidierten Polysiliciumschicht. Das Polysilicium wird typischerweise durch Plasmaätzen entfernt. In Abhängigkeit von der Korngröße der Schicht kann dabei eine erhöhte Oberflächenrauigkeit entstehen, was gerade bei den späteren Gategebieten zu Problemen führt. Durch den Einsatz von amorphen Silicium kann die Oberflächenaufrauung deutlich reduziert werden. Allerdings kann es bei den hohen Temperaturen, die bei der thermischen Oxidation von Silicium eingesetzt werden, zu einer Rekristallisierung der amorphen Schicht kommen. Eine Möglichkeit dies zu verhindern, ist die Dotierung der Schicht mit Stickstoff.[18]

SWAMI-LOCOS-Technik

Die SWAMI-LOCOS-Technik (SWAMI von englisch sidewall-masked isolation, dt. Seitenwand-maskierte Isolation) wurde 1982 von Chiu u. a. vorgestellt.[19][20][21] Dabei handelt es sich ebenfalls um eine LOCOS-Variante bei der zunächst das Silicium zurückgeätzt (engl. recessed) und der Graben anschließend durch eine oxidationsbedingte Volumenexpansion wieder aufgefüllt wird.

Wie beim Fully-recessed-LOCOS-Prozess wird ein Schichtstapel aus einer Padoxid- und einer Siliciumnitridschicht ganzflächig auf dem Wafer abgeschieden. Anschließend werden die aktiven Gebiete fotolithografisch maskiert und in den Bereichen des späteren Feldoxids der Schichtstapel durch reaktives Ionenätzen (RIE) entfernt. In einem weiteren Schritt wird das Siliciumsubstrat anisotrop geätzt, entweder ebenfalls per RIE oder nasschemisch mit KOH-Lösung. Die Tiefe der Ätzung beträgt ungefähr 55 % der gewünschten Dicke des späteren Feldoxids.

Nun folgen die SWAMI-spezifischen Prozessschritte. Zunächst werden die freigelegten Siliciumbereich (Graben) kurz thermisch Reoxidation. Dies dient zum einen der „Abrundung“ der kantigen Siliciumgrabenstruktur, zum anderen dient das dünne Oxid (im Folgenden Oxid-II genannt) als Pufferschicht, um mechanische Spannung zwischen dem Silicium und der Nitridschicht zu verringern. Danach wird ein zweiter Schichtstapel aus einer Si3N4- und einer SiO2-Schicht (Nitrid-II und Oxid-III) ganzflächig abgeschieden. Dabei kommt es unter anderem auf eine gute Seitenbedeckung der geätzten Strukturen an, weshalb in der Regel ein Verfahren der chemischen Gasphasenabscheidung (CVD) genutzt wird. Im nächsten Schritt wird die Oxid-III-Schicht mit einem stark anisotropen Prozess geätzt. Die Oxidschicht an den Seitenwänden wird aufgrund des anisotropen Charakters der Ätzung nicht abgedünnt und bleibt als Abstandshalter (engl. spacer) erhalten. Nach der Entfernung des Abstandhalter (Oxid-III) verbleibt ein Silicium-Mesa zurück, dessen Seitenwände durch das Nitrid-II und das Oxid-II geschützt ist. Die Länge des überstehenden Nitrids am Grabenboden des vertieften Siliciums wird so gewählt, dass das Wachstum des Vogelschnabels in die späteren aktiven Bereiche minimal ist. Die Grenze der aktiven Bereiche wird durch den Rand des ersten Nitrids festgelegt. Bei der anschließenden thermischen Oxidation wird dieser Bereich wieder durch das Feldoxid aufgefüllt, bis das Oxid das Niveau der ursprünglichen Siliciumoberfläche erreicht hat. Dabei wird das dünne Seitenwandnitrid hochgebogen.

Nach der Entfernung der Maskierungs- und Pufferschichten ergibt sich so eine nahezu planare Oberfläche. Die Ausprägung des Vogelschnabels oder des Vogelkopfes wird wirkungsvoll unterdrückt. Die wichtigsten Vorteile der SWAMI-LOCOS-Technik sind daher eine Erhöhung der Packungsdichte und kaum Einschränkungen hinsichtlich der Feldoxiddicke. Auch der White-Ribbon-Effekt tritt nicht auf.

Literatur

- Ulrich Hilleringmann: Silizium-Halbleitertechnologie: Grundlagen mikroelektronischer Integrationstechnik. 5. Auflage. Vieweg+Teubner, 2008, ISBN 978-3-8351-0245-3.

- Stanley Wolf, Richard N. Tauber: Silicon Processing for the VLSI Era, Vol. 2: Process Integration. 5. Auflage. Lattice Press, 1990, ISBN 0-9616721-4-5, S. 20–45.

Weblinks

- Helmut Föll: LOCOS Process. Basic Concept of Local Oxidation. In: Electronic Materials. Abgerufen am 2. Dezember 2008 (englisch).

Einzelnachweise

- M. M. Atalla, E. Tannenbaum, E. J. Scheibner: Stabilization of silicon surfaces by thermally grown oxide. In: Bell System Technical Journal. Band 38, 1959, S. 749.

- Else Kooi: The invention of locos. Institute of Electrical and Electronics, Engineers, New York, N.Y. 1991, ISBN 0-7803-0302-4.

- Else Kooi: The history of LOCOS. In: H.R. Huff, U. Gösele, H. Tsuya (Hrsg.): Silicon Materials Science and Technology: Proceedings of the Eighth International Symposium on Silicon Materials Science and Technology. Band 98. The Electrochemical Society, 1998, S. 200–214 (eingeschränkte Vorschau in der Google-Buchsuche).

- Ingolf Ruge, Hermann Mader: Halbleiter-Technologie. Springer, 1991, ISBN 3-540-53873-9, S. 226–227.

- F. Morandi: The MOS planox process. In: Electron Devices Meeting, 1969 International. Band 15, 1969, S. 126, doi:10.1109/IEDM.1969.188179.

- F. Morandi: Planox process smooths path to greater MOS density. Electronics, 1971, S. 44–48.

- J. Appels, E. Kooi, M. M. Paffen, J. J. H. Schatorje, W. H. C. G. Verkuylen: Local oxidation of silicon and its application in semiconductor-device technology. In: Philips Research Reports. Band 25, Nr. 2, 1970, S. 118–132.

- Chue San Yoo: Semiconductor Manufacturing Technology. World Scientific, 2008, ISBN 978-981-256-823-6, S. 84 ff.

- Ulrich Hilleringmann: Silizium-Halbleitertechnologie: Grundlagen mikroelektronischer Integrationstechnik. 5. Auflage. Vieweg+Teubner, 2008, ISBN 978-3-8351-0245-3.

- Stanley Wolf, Richard N. Tauber: Silicon Processing for the VLSI Era, Vol. 2: Process Integration. 5. Auflage. Lattice Press, 1990, ISBN 0-9616721-4-5, S. 20–45.

- K. Y. Chiu, J. L. Moll, K. M. Cham, Jung Lin, C. Lage, S. Angelos, R. L. Tillman: The sloped-wall SWAMI — A defect-free zero bird's-beak local oxidation process for scaled VLSI technology. In: IEEE Transactions on Electron Devices. Band 30, Nr. 11, 1983, S. 1506–1511, doi:10.1109/T-ED.1983.21329.

- H.-H. Tsai, S.-M. Chen, H.-B. Chen, C.-Y. Wu: An evaluation of FUROX isolation technology for VLSI/nMOSFET fabrication. In: IEEE Transactions on Electron Devices. Band 35, Nr. 3, 1988, S. 275–284, doi:10.1109/16.2451.

- Stanley Wolf, Richard N. Tauber: Silicon Processing for the VLSI Era, Vol. 2: Process Integration. 5. Auflage. Lattice Press, 1990, ISBN 0-9616721-4-5, S. 28–31.

- Kazuhito Sakuma, Yoshinobu Arita, Masanobu Doken: A New Self-Aligned Planar Oxidation Technology. In: Journal of The Electrochemical Society. Band 134, Nr. 6, 1987, S. 1503–1507, doi:10.1149/1.2100700.

- J. Hui, T. Y. Chiu, S. Wong, W. G. Oldham: Selective oxidation technologies for high density MOS. In: Electron Device Letters, IEEE. Band 2, Nr. 10, 1981, S. 244–247, doi:10.1109/EDL.1981.25419.

- Y. P. Han, B. Ma: Isolation process using polysilicon buffer layer for scaled MOS/VLSI. In: The Electrochem. Society Extended Abstracts. Nr. 1. Electrochemical Society, 1984, S. 98.

- Y. P. Han, B. Ma: Isolation process using polysilicon buffer layer for scaled MOS/VLSI. In: VLSI Science and Technology/1984: Materials for High Speed/high Density Applications: Proceedings of the Second International Symposium on Very Large Scale Integration Science and Technology. Electrochemical Society, 1984, S. 334.

- T. Kobayashi, S. Nakayama, M. Miyake, Y. Okazaki, H. Inokawa: Nitrogen in-situ doped poly buffer LOCOS: simple and scalable isolation technology for deep-submicron silicon devices. In: IEEE Transactions on Electron Devices. Band 43, Nr. 2, 1996, S. 311–317, doi:10.1109/16.481733.

- K. Y. Chiu, J. L. Moll, J. Manoliu: A bird's beak free local oxidation technology feasible for VLSI circuits fabrication. In: IEEE Transactions on Electron Devices. ED-29, Nr. 4, 2002, S. 536–540, doi:10.1109/T-ED.1982.20739.

- K. Y. Chiu, J. L. Moll, J. Manoliu: A bird's beak free local oxidation technology feasible for VLSI circuits fabrication. In: IEEE Journal of Solid-State Circuits. Band 17, Nr. 2, 1982, S. 166–170, doi:10.1109/JSSC.1982.1051711.

- K. Y. Chiu, J. L. Moll, K. M. Cham, J. Lin, C. Lage, S. Angelos, R. L. Tillman: The sloped-wall SWAMI- A defect-free zero bird' s-beak local oxidation process for scaled VLSI technology. In: IEEE Transactions on Electron Devices. ED-30, Nr. 11, 1983, S. 1506–1511, doi:10.1109/T-ED.1983.21329.