Grabenisolation

Die Grabenisolation (englisch shallow trench isolation, STI, auch box isolation technique, BIT) ist ein Verfahren der Halbleitertechnik zur elektrischen Isolation einzelner Bauelemente (meist MIS-Feldeffekttransistoren) auf integrierten Schaltkreisen (IC). Dazu werden zwischen den elektrisch aktiven Gebieten ca. 250 bis 700 nm tiefe Gräben erzeugt und mit einem elektrisch isolierenden Material (meist Siliziumdioxid) aufgefüllt. Ein ähnlicher Prozess wird auch bei anderen Halbleiterprodukten eingesetzt, beispielsweise bei Hochleistungsbipolartransistoren oder analogen integrierten Schaltkreisen. Dabei werden Grabentiefen von ca. 5 µm eingesetzt. Zur Unterscheidung von der „flachen Grabenisolation“ (STI, shallow = dt. flach) wird dieser Prozess als „tiefe Grabenisolation“ (engl. deep trench isolation, DTI, deep = dt. tief) bezeichnet.

Darüber hinaus gibt es noch eine Reihe unterschiedlicher Isolationsmethoden, die ebenfalls einen mehr oder weniger tiefen, mit elektrisch isolierendem Material gefüllten Graben nutzen.[1]

Hintergrund

Die STI-Technik ist seit Jahren die bevorzugte Isolationstechnik (zur elektrischen Isolation einzelner Bauelemente) bei CMOS-Schaltkreisen (vor allem bei Technologieknoten unter 0,25 µm[2][3]). Das Verfahren wurde entwickelt, da früher genutzte Techniken (vor allem LOCOS-Prozess und Erweiterungen) nicht mehr ausreichten, um bei der verwendeten minimalen Strukturgröße (engl. feature size) eine ausreichende Isolation zu gewährleisten. Die LOCOS-Technik hatte dabei einige wesentliche Nachteile, beispielsweise begrenzt die Ausbildung von „Vogelschnäbeln“ die Packungsdichte und die Isolationswirkung ist eher oberflächlich. Zudem beeinflusst die LOCOS-Technik die Topographie der Chipoberfläche negativ, so dass nachfolgende Schritte infolge der schlechter durchführbaren lithographischen Strukturierung behindert wird. Der Hauptnachteil des STI-Prozesses gegenüber LOCOS ist die höhere Anzahl von Prozessschritten.

STI-Prozess

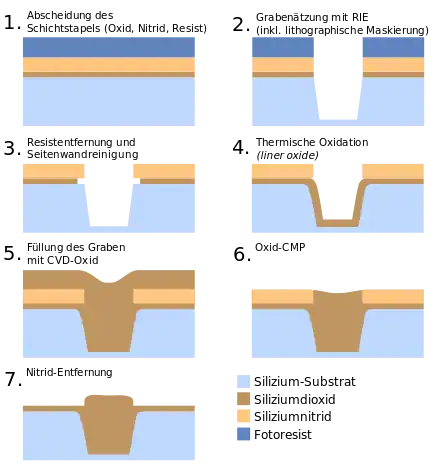

Der STI-Prozess ist in der Regel einer der ersten Fertigungsschritte bei der Herstellung von integrierten Schaltkreisen. Ausgangsmaterial ist ein unstrukturierter Siliziumwafer. Die in der nachfolgenden Grundbeschreibung angegebenen Schichtdicken[4][5] sind Orientierungswerte und können sich bei real verwendeten Prozessen zum Teil deutlich unterscheiden.

Der erste Prozessabschnitt (Bild 1) umfasst, die Abscheidung des Schichtstapels, der später strukturiert wird. Dazu wird durch thermische Oxidation von Silizium zunächst eine sehr dünne Siliziumdioxidschicht erzeugt (ca. 20–40 nm). Dieses Oxid dient für die nachfolgende Siliziumnitridschicht als Pufferschicht, die durch unterschiedlich große Gitterkonstanten und thermischen Ausdehnungskoeffizienten entstehenden mechanischen Spannungen reduzieren soll und so die Haftung der Nitridschicht verbessert. Das Oxid wird danach über chemische Gasphasenabscheidung bei Niederdruck (engl. low pressure cvd, LPCVD) mit einer Siliziumnitridschicht (ca. 100–150 nm) beschichtet; die Nitridschicht dient später als Stoppschicht für den CMP-Prozess (engl. chemical-mechanical planarization). Abschließend erfolgt der Auftrag eines Fotolacks durch Rotationsbeschichtung.

Der nun folgende zweite Prozessabschnitt (Bild 2) ist das Freilegen der späteren Isolationswannen. Dazu wird der zuvor aufgetragene Fotolack fotolithografisch strukturiert und somit die späteren Grabengebiete maskiert. Danach erfolgt das anisotrope Ätzen des Schichtstapels und der Grabengebiete (ca. 250–700 nm tief), beispielsweise durch reaktives Ionentiefenätzen (DRIE). Um Polymerreste von RIE-Schritt zu entfernen, folgt ein kurzer nasschemischer Ätzschritt mit Fluorwasserstoff-Lösung (Flusssäure), der gleichzeitig das Pufferoxid leicht unterätzt (Bild 3).

Nun erfolgt das Füllen der Gräben mit dem Isolationsmaterial Siliziumdioxid. Die Abscheidung erfolgt ganzflächig über ein CVD-Verfahren bis zum Überfüllen der Gräben. Das CVD-Verfahren muss dabei die Eigenschaft aufweisen, auch kleinere Strukturen mit höheren Aspektverhältnissen homogen zu füllen. Dies ist beispielsweise mit HDP-TEOS-PECVD (High-Density-Plasma-Tetraethylorthosilicat-Plasma-Enhanced-CVD) möglich. Um eine qualitativ höherwertige Grenzfläche zwischen dem Silizium und dem CVD-Siliziumdioxid zu erhalten, das heißt eine Grenzfläche mit wenigen Grenzflächenladungen, wird häufig vor der CVD-Beschichtung nochmals ein thermisches Siliziumdioxid auf den Grabenflächen erzeugt, das sogenannte liner oxide (Bild 4, ca. 20–50 nm). Dabei werden unter anderem auch durch den Ätzprozess verursachte Schäden und mechanischer Stress an den Grabenkanten reduziert.

Nach dem Füllen der Gräben ist der Wafer vollständig mit einem Schichtsystem aus Siliziumdioxid und -nitrid bedeckt. Für die nachfolgenden Fertigungsschritte wie dem Aufbau der Transistorstrukturen ist es daher notwendig, das Siliziumsubstrat wieder freizulegen. Dies erfolgt auch in Hinblick auf die Verbesserung der Oberfläche des Wafers (Topografie) – wichtig vor allem für die Fotolithografie – durch den Abtrag der über dem Wafer liegenden Schichten durch chemisch-mechanisches Polieren (CMP) des Siliziumdioxids, die sogenannte Oxid-CMP. Das Siliziumnitrid dient dabei als Stoppschicht für den Polierprozess. Anschließend folgt noch die nasschemische Entfernung der Siliziumnitrid-Stoppschicht (mit Phosphorsäure) sowie eine Rückätzung des verbleibenden Oxids mit Flusssäure, bis die Pufferoxidschicht entfernt ist.

Literatur

- Gary S. May, Simon M. Sze: Fundamentals of Semiconductor Fabrication. Wiley & Sons, 2003, ISBN 0-471-23279-3.

- Stephen A. Campbell: The Science and Engineering of Microelectronic Fabrication. 2. Auflage. Oxford University Press, 2001, ISBN 0-19-513605-5.

Einzelnachweise

- vgl. Dinesh C. Gupta: Semiconductor Fabrication: Technology and Metrology. ASTM International, 1989, ISBN 0-8031-1273-4, S. 291.

- Michael Quirk, Julian Serda: Semiconductor Manufacturing Technology: Instructor's Manual (Memento vom 28. September 2007 im Internet Archive) (PDF; 1,4 MB). S. 25.

- Gary S. May, Simon M. Sze: Fundamentals of Semiconductor Fabrication. Wiley & Sons, 2003, ISBN 0-471-23279-3, S. 207.

- Sami Franssila: Introduction to Microfabrication. John Wiley & Sons, 2010, ISBN 978-0-470-74983-8, S. 336.

- Yuzhuo Li: Microelectronic Applications of Chemical Mechanical Planarization. John Wiley & Sons, 2007, ISBN 978-0-471-71919-9, S. 349–350.