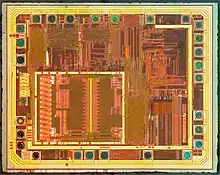

TI MSP430

Der MSP430 ist ein 16-Bit-RISC-Mikrocontroller der Firma Texas Instruments. Er wurde Anfang der 1990er Jahre bei der deutschen Niederlassung von Texas Instruments in Freising entwickelt und kam 1993 auf den Markt. Der Mikrocontroller ist für Anwendungen mit niedrigstem Stromverbrauch optimiert. Der Prozessorkern ist mittels Compiler in der Programmiersprache C und/oder Assembler programmierbar. Der Controller ist in verschiedenen Ausführungen verfügbar. Texas Instruments erweitert die Palette laufend, was auf einen großen Erfolg dieser Controllerlinie hindeutet. Typische Anwendungen sind Geräte mit Langzeitbatterie, wie zum Beispiel Wärmezähler, Heizkostenverteiler, Tauchcomputer oder auch Blutdruckmessgeräte im medizinischen Bereich.

Die MCU gilt in der Elektronik als Quasi-Standard, wird aber zunehmend von Cortex-M-Derivaten verdrängt.

Speicheraufteilung

Der MSP430 besitzt eine klassische Von-Neumann-Architektur. Die Größe des adressierbaren Speichers ist bei den meisten Derivaten auf 64 kByte limitiert. Speichergrößen liegen bei bis zu 256 kByte FLASH und bis zu 16 kByte RAM (aktuell [November 2008] auch im gleichen Baustein). Bei allen Derivaten sind ca. 2 kByte der unteren adressierbaren 64 kByte für interne Funktionen (wie zum Beispiel einen Boot-Loader) reserviert, so dass mit den zwei größten 16 Bit Speicherausbauten 60 kByte FLASH mit 2 kByte RAM bzw. 48 kByte FLASH mit 10 kByte RAM bereitstehen.

Seit November 2006 bietet TI auch eine Familie mit einer so genannten MSP430X-CPU an. Diese basiert auf einem Speichermodell, welches bis zu 1 MByte Speicher adressieren kann. Der Adressbus hat hierbei 20 Bit, alle Register (außer dem Statusregister R2/SR) sind deshalb nicht mehr 16 Bit breit, sondern 20 Bit. So sind die in den „normalen“ CPUs verfügbaren Befehle weiterhin ohne Änderung verfügbar. Die interne Abarbeitung musste jedoch an die größere Adressbreite angepasst werden, zum Beispiel muss beim CALL-Befehl ein Wort mehr auf den Stack geschrieben werden, da ja 4 weitere Bit als Rücksprungadresse abgelegt werden müssen. Erhältlich sind Bausteine mit bis zu 120 kByte Flash/4 kByte RAM bzw. 116 kByte Flash/8 kByte RAM, alle mit LCD-Treibern.

In den untersten 16 Byte (Adresse 0000 h bis 000F h) sind spezielle Register (SFR, Special Function Register) für die Interrupt- und „Modul“-Steuerung eingeblendet. Die Register der 8-Bit-Peripherie belegen die nächsten 240 Byte (Adresse 0010 h bis 00FF h). Bis hierher ist ein Speicherzugriff byteweise notwendig. Darüber sind die nächsten 255 Byte (Adresse 0100 h bis 01FF h) für die 16-Bit-Peripherie reserviert. Ab hier wird wortweise auf den Speicher zugegriffen.

Ab dem 513. Byte (Adresse 0200 h bis 09FF h) liegt das RAM. Bei den größeren RAM-Ausbauten (größer 2 kByte) liegt dieses tatsächlich im Speicher weiter oben (Adresse 1100 h bis 38FF h), wird aber zum Teil in den unteren Adressbereich gespiegelt. Dazwischen liegen Boot- und Informations-Speicher (Adresse 0C00 h bis 0FFF h resp. 1000 h bis 10FF h).

Der Informations-Speicher ist wie der Code-Speicher ein Flash-Speicher, dessen Besonderheit die Aufteilung in zwei 128 Byte große Segmente darstellt, die als „Zwischenspeicher“ benutzt werden können, für Daten, die immer mal wieder zu ändern sind. Der restliche FLASH-Speicher (für den Programmcode und Konstanten) hat Segmente von 512 Byte. Er liegt grundsätzlich im Speicherbereich 1100 h bis FFFF h, wird aber je nach Speicherausbau (mehr RAM oder kleineres FLASH) erst ab Adresse FC00 h (für 1 kByte FLASH) liegen. Außerdem sind die obersten 32 Byte (Adresse FFE0 h bis FFFF h) des Speichers für die Interrupt-Vektoren vorbehalten, die jedoch nur bei Bedarf benutzt werden. Werden keine Interrupts benutzt, kann auch der Speicher für deren Vektoren als Programmspeicher genutzt werden.

Neuerdings werden auch FRAM basierende MSP430 angeboten[1]. Dieser Speichertyp lässt sich, im Vergleich zu Flash, schneller und mit viel weniger Energie beschreiben. Ein weiterer Vorteil dieser Bausteine ist, dass es keine starre Grenze zwischen Code und Daten (Flash und RRAM) gibt, sondern diese nach Bedarf gewählt werden kann. Der verwendete Fertigungsprozess der FRAM-Bausteine wurde gemeinsam von Ramtron und TI entwickelt.

Interruptbehandlung

Der MSP430 kennt grundsätzlich 16 Interruptquellen, die nach ihrer Lage in den Interrupt-Vektoren priorisiert sind. Nicht in jedem Baustein sind alle Quellen belegt, dies ist vom Ausbau der „internen“ Peripherie abhängig.

Mehrere Interrupts können den gleichen Vektor belegen. Ist das der Fall, muss von der Software über entsprechende Bits entschieden werden, welcher Interrupt aktuell vorliegt. Außerdem haben verschiedene Interrupts „eigene“ Vektorregister, über die es jeweils wieder bis zu 10 unterschiedliche Quellen (erweiterbar bis zu 128) geben kann. Als Beispiel seien hier die Timer-Interrupts genannt.

Der MSP430 beherrscht mehrere Power-Down-Modi, in denen die Befehlsverarbeitung gestoppt oder der Takt abgeschaltet wird. Im niedrigsten Modus liegt der Stromverbrauch, je nach Typ, bei 0,4 µA. Will man eine Echtzeituhr realisieren, werden ca. 2 µA benötigt. Die CPU kann durch verschiedene Interrupts wieder aufgeweckt werden.

Prozessor

Der Befehlssatz enthält nur 27 „Grundinstruktionen“ und 24 „emulierte“ Instruktionen, die aus den Grundinstruktionen zusammengesetzt sind. Der Begriff „RISC“ ist dafür angemessen.

Die Abarbeitung eines Befehl dauert 1 bis 6 Takte. Bei Taktfrequenzen von bis zu 25 MHz werden so Schrittzeiten bis herab zu 40 ns erreicht. Die maximale Taktfrequenz ist vom Typ und der Speisespannung abhängig, etwa:

- MSP430x1xx: 4,15 MHz bei 1,8 V .. 8 MHz bei 3,6 V (linear)

- MSP430x2xx: 4,15 MHz bei 1,8 V, 16 MHz bei 3,3 .. 3,6 V (nichtlinear)

- MSP430x5xx: 8 MHz bei 1,8 V, 25 MHz bei 2,4 .. 3,6 V (gestuft)

MSP430-Mikrocontroller können einen MSP430-Kern oder einen MSP430X-Kern als Prozessor enthalten. Letzterer verarbeitet zusätzliche Befehle, um die auf 20 Bit verbreiterten Register zu bedienen und mehr als 64 KiByte (die Grenze von 16 bit) zu adressieren, und ist zum MSP430-Kern (ohne „X“) kompatibel. Aus Sicht des MSP430X-Befehlssatzes ist die erweiterte Bitbreite auf 32 Bits „limitiert“, die 20-Bit-Registerbreite wurde als derzeitiger Kompromiss zwischen Adressierumfang (1 MiByte) und Komplexität sowie Energieverbrauch gewählt. Genügen 20 Bit für bestimmte arithmetische Operationen, kann man diese erweiterten Register auch allgemein verwenden (zurzeit nur in Assembler möglich).

Architektur

Der MSP430 hst 16 Register. Register 0 ist der Program-Counter (PC), Register 1 der Stack-Pointer (SP, Stapelzeiger) und Register 2 das Prozessor-Status-Register (PS). Register 3 (Constant-Generator, CG) ist ein Pseudo-Register, das die häufig benötigten Konstanten −1, 0, +1 und +2 liefert. Diese vier Register haben spezielle Funktionen, sind aber wie alle anderen zwölf Register auch frei benutzbar. Die Möglichkeit, den Program-Counter oder den Stack-Pointer als „freie“ Register zu benutzen, wurde bereits bei der PDP-11 verwendet. Die Register sind nicht adressierbar; sie sind nicht als Kopie im Adressraum des MSP430 verfügbar.

Mögliche Adressierungsarten sind Registeradressierung (Rn), indizierte Adressierung (X(Rn)), symbolische Adressierung, absolute Adressierung, indirekte Adressierung (@Rn), indirekte Adressierung mit Autoinkrement (@Rn+) und direkte Adressierung für Konstanten. Diese Adressierungsarten stehen für den Quelloperanden zur Verfügung. Bei Instruktionen mit zwei Operanden stehen für den Zieloperanden nur Register-Adressierung, symbolische Adressierung, absolute Adressierung und indizierte Adressierung bereit.

Interne Peripherie („Module“)

Die Register der „internen“ Peripherie (Takt-Erzeugung, SVS (Überwachung der Versorgungsspannung), Hardwaremultiplizierer, DMA, Ports, Watchdog, Timer, serielle Schnittstellen, Komparatoren, ADCs und DACs) sind (wie oben erwähnt) im Adressbereich eingebunden. Diese Peripherie ist je nach Modell mit auf dem Chip integriert. Es wird zwischen 8-Bit-Peripherie und 16-Bit-Peripherie unterschieden.

Takterzeugung

Bei der Takterzeugung setzt TI auf drei unterschiedliche Quellen, die je nach Bedarf sehr geringen Stromverbrauch (32,768 kHz in Form eines Uhrenquarz), sehr schnelles Aufwachen nach einem Interrupt (interner RC-Oszillator, 6 µs Zeit bis zum Erreichen der nominellen RC-Taktfrequenz) oder hohe Frequenz (bis zu 16 MHz) ermöglichen. Der MSP430 eignet sich sehr gut zum Übertakten: Der Niederfrequenzoszillator kann mit einem 100-kHz-Quarz (rund 200 % Übertaktung) betrieben werden, und der HF-Oszillator kann um 100 % übertaktet werden, zumindest bei Raumtemperatur und bei der maximal zulässigen Betriebsspannung.

SVS

Der Supply Voltage Supervisor, auch Brown Out Reset oder Brown Out Detector genannt, überwacht die Versorgungsspannung und ermöglicht auch bei einem kurzfristigen Unterschreiten der Mindestspannung ein geregeltes neues Hochfahren (Reset) des Systems. Wird die Mindestspannung unterschritten, können unvorhersehbare Fehler im System auftreten, die zu nicht gewollten Programmausführungen oder Hängen bleiben führen können. Mit dem SVS werden solche Fehler vermieden und ein geregelter Neustart, auch ohne Abschaltung der Versorgungsspannung, vollzogen.

Hardwaremultiplizierer

Der Hardwaremultiplizierer beherrscht die Multiplikation von vorzeichenlosen und vorzeichenbehafteten 8-Bit- und 16-Bit-Zahlen, wobei als Ergebnis eine bis zu 32 Bit große Zahl entsteht. Das jüngste Kind der MSP430-Familie beherrscht sogar 32 Bit große Zahlen und ein 64 Bit großes Resultat. Er beherrscht ebenso vorzeichenloses und vorzeichenbehaftetes Multiplizieren und Zusammenzählen (MAC, eine Domäne der DSPs). Der erste Operand dieser vier Operationen ist jeweils in einem speziellen Register abzulegen, der zweite Operand immer im gleichen Register. Das Ergebnis steht immer in den beiden gleichen Ausgangsregistern. Es liegt automatisch drei (!) Takte nach dem Ablegen des zweiten Operanden zur Verfügung.

DMA

Mit Hilfe des DMA-Controllers können ohne Zutun der CPU sehr schnell Daten von einem Speicherbereich in einen anderen transferiert werden. In dieser Zeit kann die CPU nicht auf den Bus zugreifen, weshalb sie angehalten werden muss. Der DMA-Transfer ist aber auch in den Low-Power-Modi zugelassen, wobei der CPU-Takt hochgefahren werden muss. Ein weiterer Vorteil des DMA-Moduls besteht darin, dass es im „Tandem“-Prinzip verwendet werden kann, das heißt, dass die Taktzyklen alternierend zwischen CPU und DMA aufgeteilt werden. Das eignet sich beispielsweise hervorragend, um ein Videobild aufzubauen, ohne dass dazu die CPU verwendet werden muss. Durch die Möglichkeit der Hintereinanderschaltung der DMA-Einheiten (meistens 3) kann so aber auch ein digitaler Filter realisiert werden, welcher mit Hilfe der AD- und DA-Wandler beispielsweise für Audioapplikationen verwendet werden kann. Eine weitere sehr hilfreiche Funktion mit dem DMA ist, Speicherinhalte zu verschieben, das erspart erheblich Zeit und Programmieraufwand. Es ist beispielsweise bei der MSP430F16XX-Serie sehr interessant, da diese mehr Speicher (RAM) besitzen. Auch das Kopieren vom RAM zum FLASH kann per DMA einfacher gestaltet werden als mit Software.

Ports

Die Ports sind zum Teil interrupt-fähig, was bedeutet, dass der MSP430 über sie aus einem Low-Power-Mode aufgeweckt werden kann. In solch einem Zustand verbraucht der MSP430 die wenigste Energie (ca. 0,4 µA). Die Ports selbst können nur sehr wenig Strom treiben und aufnehmen (ca. 6 mA, wobei der Gesamtstrom in den Baustein je nach Typ bei weitem kein Vielfaches der Pinanzahl dieses Wertes ist). Die Bezeichnungen der Ports verlaufen so: P1.0 - P2.5, es gibt also z. B. zwei Register beim MSP430G2xxxx (P1,P2), die dann jeweils einzelne Ausgänge haben(P1.0). Die einzelnen Ausgänge können sowohl als Eingang als auch als Ausgang verwendet werden. So lassen sich alle Ausgänge/Eingänge auf einmal über den Port definieren, oder man definiert jeden Ausgang/Eingang einzeln.

Watchdog

Der Watchdog-Timer wird eingesetzt, wenn das System nach einem Deadlock ohne Zutun des Nutzers wieder bedienbar sein soll. Dazu zählt der Watchdog einen Timer herauf, der von der Applikation immer wieder auf Null gesetzt werden muss. Ist die Applikation wegen eines Deadlocks dazu nicht in der Lage (im Allgemeinen sagt man, sie hat sich verlaufen), wird durch den Watchdog ein Reset ausgelöst. Das System fängt von vorne an und ist wieder bedienbar (auch wenn es dem Benutzer nicht unbedingt gefällt, wenn er von vorne anfangen muss). So kann sichergestellt werden, dass auch nach einer intensiven Störung von außen, zum Beispiel ESD-Entladung über den Prozessor, das Programm wieder in einen definierten Betriebszustand zurückkehrt. Auch sehr selten auftretende, bei Tests nicht gefundene, Programmablauffehler können so abgefangen werden.

Die Funktion des Watchdog-Timers kann jedoch auch abgeschaltet werden, wenn die oben genannte Funktionalität nicht gewünscht wird bzw. störend ist. Man kann den Watchdog-Timer auch als zusätzlichen Zähler benutzen, um damit zum Beispiel eine Real-Time-Clock zu realisieren. Das geschieht, indem man den Zähler so konfiguriert, dass er jede Sekunde einen Interrupt auslöst, und zählt dann in dem Interrupt die Sekunden hoch. Nachteil dieser „Softwareuhr“ gegenüber einem externen Uhrenschaltkreis: Wenn der MSP430 komplett ausgeschaltet wird, also keine Möglichkeit mehr hat den Interrupt auszulösen, kann natürlicherweise die Zeit nicht mitgezählt werden und muss dann beim nächsten Starten neu initialisiert werden.

Timer

Die Timer haben grundsätzlich 16 Bit. Sie können durch unterschiedliche Takte angesprochen werden, auch von externen Ereignissen. Damit sind von sehr kurzen Timerzeiten im Bereich einiger hundert Nanosekunden (schneller 16-MHz-Takt) bis zu beliebig langen Timerzeiten (viele Monate und Jahre durch sehr langsame externe Signale) möglich. Selbst durch die zweite eigene Zeitbasis mit 32 kHz sind noch direkte Timerzeiten von bis zu zwei Sekunden, bei Benutzung eines zusätzlichen Registers bis zu 1,5 Tagen, realisierbar. Auch Timer können die CPU aus einem Low-Power-Modus aufwecken. Damit sie aber laufen – sie brauchen einen Takt – kann die Stromsparfunktionalität nicht so hoch getrieben werden wie bei den Ports, wo praktisch keine interne Peripherie zur Unterstützung notwendig ist.

Serielle Schnittstellen

Bei den seriellen Schnittstellen sind derzeit als Protokoll UART, SPI, USB (nur slave) und I²C in Hardware realisiert. Weitere wie z. B. LIN sollen folgen. CAN wird auf absehbare Zeit nicht durch den MSP430 unterstützt werden, da der Fertigungsprozess, mit dem die Controller hergestellt werden, nicht für den Temperaturbereich im Automotive-Sektor geeignet ist. Die Baudrate könnte theoretisch auf bis zu 16 MBit/s gesetzt werden. Asynchrone Kommunikation läuft sicher bis 115,2 kBit/s, SPI arbeitet um 1 MBit/s und I²C in den unterstützten Modi bis 400 kBit/s.

Komparatoren

Mit den Komparatoren können analoge Spannungen gegen unterschiedliche Referenzspannungen verglichen werden. Die Referenzspannung kann intern (0,5·VCC, 0,25·VCC oder rund 0,55 V) oder extern erzeugt werden. Mit dem Ergebnis können Interrupts ausgelöst oder Timer getriggert werden. Mit dem getriggerten Timer sind so PWM-Signale erzeugbar, die von einem Eingangssignal abhängig pulsweiten-moduliert sind.

Man kann auch den Vergleich direkt auf einen Port, CAOUT, schalten. Wenn die 2 Eingangsports des Comparators mit und bezeichnet sind, dann ist CAOUT High, wenn die Spannung größer ist, die an anliegt. Welcher der beiden Ports und welcher ist, kann mittels der Bits CARSEL und CAEX im Comparator Control Register eingestellt werden.

ADCs

Die AD-Wandler haben eine Auflösung von 10, 12, 14 oder 16 Bit, wobei je nach Typ des MSP430 als Wandlungsverfahren das SAR- (Sukzessive Approximation), Slope- (Rampenverfahren) oder Sigma-Delta-Verfahren eingesetzt wird. Wie bei den Komparatoren, benötigt man für AD-Wandler ebenfalls eine Referenzspannung, die intern oder extern erzeugt werden kann. Die Abtastrate kann nominell bis 5 MHz betragen, womit Signale bis theoretisch 2,5 MHz abtastbar wären. Die mit derart hoher Abtastrate gewonnenen Daten könnten aber kaum von der CPU verarbeitet werden, da dieser pro Abtastwert nur 3,2 Taktzyklen (16-MHz-Takt) zur Verfügung stünden.

CRC16

Das CRC16-Modul erzeugt einen CRC-Code, beruhend auf einer Folge von Datenwerten und kann für die Prüfung und Korrektur der Daten verwendet werden. Der CRC16-Modul-Prüfcode beruht auf dem CRC-CCITT-Standard. Ideal kann dieses Modul für Datenübertragung via TCP/IP oder mit angekoppelten W-LAN-Modulen verwendet werden. Es eignet sich aber auch als Prüfcodegenerator beim Schreiben auf magnetische Datenträger wie Disketten oder Festplatten.

DACs

Die DACs haben eine Auflösung von 8 oder 12 Bit. Das analoge Ausgangssignal kann also in 256 oder 4096 Stufen variiert werden. Als Referenzspannung können hier, wie bei den Komparatoren und ADCs, die internen oder externen Referenzen benutzt werden. Als „Ausgabeformat“ können die binären Daten direkt oder als Zweierkomplement ausgegeben werden. Der Ausgangsverstärker kann automatisch kalibriert werden, damit die Ausgangsspannung korrekt den digitalen Werten folgt. Der DAC selbst kann mit bis zu 550 kHz getaktet werden, was entsprechend eine theoretische Ausgangsfrequenz bis zu 275 kHz ermöglicht.

Operationsverstärker

Bausteine mit integrierten Operationsverstärkern erlauben es, analoge Spannungen zu verstärken (was der Nutzung in Messsystemen zugutekommt). Die Operationsverstärker sind wie der Rest des Bausteins stromsparend und werden aus einer einzigen Spannungsquelle versorgt (single supply, low current). Die Ausgangsspannung kann bis zur Versorgungsspannung reichen (rail to rail). Die Einschwingzeit (settling time) kann bei höherem Stromverbrauch kürzer programmiert werden. Für eine programmierbare Verstärkung sind unterschiedliche Widerstände für die Rückkopplung eingebaut.

LCD-Treiber

Der in den Bausteinen der 4xx-Serie und der 6xx-Serie eingebaute LCD-Treiber kann statische und gemultiplexte LCDs ansteuern. Dabei sind bis zu 40 Segmente und 4 gemeinsame Anschlüsse (backplanes) möglich. Dafür reicht der Displayspeicher mit 20 Byte aus, der im Adressbereich 0091h bis 00A4h eingeblendet ist. Über externe Widerstände kann der Kontrast eingestellt werden.

Echtzeituhr

Die Echtzeituhr (RTC, englisch Real Time Clock) kann als Mehrzweck-32-Bit-Zähler (counter mode) oder als Uhr mit Kalenderfunktion verwendet werden (calendar mode). Im Zählmodus umfasst das RTC-Modul zwei unabhängige 8-Bit-Timer, die auch als ein 16-Bit-Timer zusammenschaltet werden können. Beide Zähler sind dann Zeitgeber und können durch die Software gelesen und beschrieben werden. Die Kalenderfunktion beachtet Monate mit weniger als 31 Tagen und sogar Schaltjahre. Das RTC-Modul hat Alarm-Register zur Weckfunktion und unterstützt Hardware-Interrupts. Im Gegensatz zu den Timern „überlebt“ die Echtzeituhr Resets.

USB

MSP430F55XX mit integriertem Universal Serial Bus (USB) sind verfügbar.

- Full-Speed Universal Serial Bus (USB) Device mit integrierter physikalischer Übertragungseinheit und SIE

- Integriertes 3,3 V/1,8 V USB-Stromversorgungs-System, geeignet für self-powered und bus-powered USB-Geräte ohne zusätzliche Spannungsregler

- Integrierter Frequenzgenerator (PLL) für USB — Quarz erforderlich

- Acht Eingangs- und acht Ausgangs-USB-Endpunkte (nicht-isochroner Transfermodus) verfügbar

- USB-Bootloader läuft mit einer ganzen Reihe verschiedener Quarze an (nicht nur ein bestimmter Quarz)

Mit der USB-Schnittstelle lässt sich beispielsweise ein HID, ein serielles USB-Gerät oder ein USB-Stick realisieren, nicht aber ansteuern. Sein zugeordneter Dual-Port-RAM (2 KByte) kann bei Nichtbenutzung des USB-Moduls als zusätzlicher Arbeitsspeicher dem internen ohnehin etwas knappen Arbeitsspeicher zugefügt werden. Isochrone Datenübertragung ist nicht vorgesehen, daher kann die Video- und Audio-Geräteklasse nicht implementiert werden.

Weitere Peripheriemodule

Seit dem Shrinking Ende 2008 gibt es einige Typen der Reihe MSP430X5xx mit integriertem RF-Transceiver, LDO-Spannungsregler und einer AES-Cryptoengine.

Programmierung

Als Programmiersprache bietet sich C an. Die Architektur ist dafür ausgelegt. Zeiger, Arrays und Stapelspeicher lassen sich leicht implementieren. Obwohl der MSP430 einen RISC-Befehlssatz hat, lässt er es zum Teil zu, dass ein C-Ausdruck dank der unterschiedlichen Adressierungsmodi in eine einzelne Maschinenanweisung übersetzt wird. Unterschiedliche kommerzielle und freie C-Compiler stehen zur Verfügung.

Liste der verfügbaren C-Compiler (unvollständige Auswahl)

| Name | Hersteller | Erhältliche Versionen |

|---|---|---|

| MSP-CCE430 | TI | Freeware-Version vorhanden. Bis zu 16 kB Code sind in der neuen Version 3 erlaubt. |

| MSP430-GCC | TI | GNU Compiler Collection für MSP430. Vollständiger Open-Source Compiler und Debug-Stack |

| IAR EW430 Kickstart | TI | Freeware, de facto von IAR, mit bis zu 4 kB Code |

| AQ430 | Quadravox | Demo-Version mit Codebegrenzung auf 4 kB |

| Crossworks | Rowley Associates | 30-Tage Demo |

| Hi-Tech | HI-TECH Software | Zeitlich begrenzte Demo-Version erhältlich |

| HFW_430 | HiTex | Vollversion die aber MSP-EVK330 voraussetzt. |

| EW430 | IAR | 30-Tage Demo-Version mit 4 kB Code-Limit |

| ICC430 | Imagecraft (Memento vom 12. Oktober 2007 im Internet Archive) | 30-Tage Demo |

| MCC-430 | MicroCOSM (Memento vom 12. Januar 2010 im Internet Archive) | Demo mit Codebegrenzung auf 4 kB |

| MSPGCC | Peter A. Bigot et al. | Freie GNU-Variante (eingestellt, abgelöst durch den GCC von Texas Instruments) |

| LLVM-MSP430 | Verschiedene Entwickler (Memento vom 25. März 2012 im Internet Archive) | Backend für die LLVM |

Es gibt auch Anwender, die den MSP430 in Assembler programmieren. Da die C-Compiler in der Regel hoch optimierend eingestellt werden können und es eigentlich per se auch schon sind, ist das wirklich nur für zeitkritische Applikationsteile notwendig. Dazu können die meisten C-Compilern Assembler- in den C-Code einbauen.

Ein etwas ausgefallenes aber sehr effizientes Programmier- und Testsystem ist FORTH. Neben einigen OpenSource-FORTH-Projekten gibt es ein sehr gutes professionelles FORTH-Entwicklungssystem „Swift-X“. Forth verwendet die umgekehrte polnische Notation (UPN).

Die Programmierung des Bausteins und das Debugging sind über eine JTAG-Schnittstelle zu realisieren. Dazu bietet TI eine als FLASH-Emulation-Tool (FET) bezeichnete Hardware an, die über den Parallelport oder die USB-Schnittstelle des PC auf den JTAG-Port zugreift. In den neuesten Varianten (MSP430F20xx) ist der JTAG-Port (der eigentlich über mindestens vier Signalleitungen und Reset verfügt) durch ein Interface, das TI „Spy-Bi-Wire“ nennt, auf 2 Signalleitungen reduziert worden, so dass nur noch vier Anschlüsse auf einem Zielsystem zum Debugging notwendig sind: Zwei für Spy Bi-Wire, Masse und Versorgungsspannung.

Das moderne FET-Tool wird als USB-Stick geliefert. Wenn das Zielsystem hinreichend wenig Speisestrom benötigt, genügt dafür USB und eine externe Spannungsversorgung ist nicht notwendig.

Das MSP430 LaunchPad (MSP-EXP430G2), eigentlich ein Eval-Board, lässt sich ebenfalls ganz offiziell zur Programmierung per Spy Bi-Wire verwenden. Die benötigende Anschlüsse finden sich auf der Anschlussleiste J3 und der nicht bestückten Anschlussleiste J4.

Liste der FLASH-Emulation-Tools (FET)

| Name | Hersteller | Schnittstelle | Protokoll |

|---|---|---|---|

| MSP-FET430PIF | TI | Parallel-Port | JTAG |

| MSP-FET430UIF | TI | USB-Schnittstelle | JTAG, Spy-Bi-Wire |

| MSP-430 LaunchPad | TI | USB-Schnittstelle | Spy-Bi-Wire |

| eZ430-F2013 | TI | USB-Schnittstelle | Spy-Bi-Wire |

| eZ430-RF2500 | TI | USB-Schnittstelle | Spy-Bi-Wire |

| FETP | SoftBaugh (Memento vom 14. Mai 2015 im Internet Archive) | Parallel-Port | JTAG |

| USBP | SoftBaugh (Memento vom 14. Mai 2015 im Internet Archive) | USB-Schnittstelle | JTAG, Spy-Bi-Wire |

| MSP430-JTAG | Olimex (Memento vom 1. Juli 2012 im Internet Archive) | Parallel-Port | JTAG |

| MSP430-JTAG-ISO | Olimex | USB-Schnittstelle | JTAG, Spy-Bi-Wire |

| MSP430-JTAG-Tiny | Olimex | USB-Schnittstelle | JTAG, Spy-Bi-Wire |

| MSP430-JTAG-RF | Olimex | USB-Schnittstelle | JTAG, Spy-Bi-Wire |

| FlashPro-CC | Elprotronic | USB-Schnittstelle | JTAG, Spy-Bi-Wire, BSL |

| VisSim/ECD | Visual Solutions | USB-Schnittstelle | JTAG, Spy-Bi-Wire |

| LA-3713 | Lauterbach | USB-Schnittstelle / Ethernet | JTAG, Spy-bi-Wire |

Des Weiteren enthält jeder programmierbare MSP 430 einen Bootstraploader, der über eine UART-Schnittstelle das Programmieren der Bausteine erlaubt. Details sind in einer TI Application Note[2] aufgeführt.

Nicht jeder MSP430 ist mit einem Bootstraploader ausgestattet (MSP430F20xy x = 0, 1 y = 1, 2, 3 sh. SLAU319AE Seite 4), diese können aber mit dem MSP430 Flasher programmiert werden (SLAU654).

Mit Hilfe des Boot-Strap-Loaders (BSL) kann aber auch über eine serielle Schnittstelle das Programm neu geladen werden.

Das von HiTex angebotene Tool „DProbe430“ mit seinem Aufrüstmodul „DBox16“ ist der bislang einzige Emulator für den MSP430. Es unterstützt Realtime-Debugging in Assembler (von TI) und Hochsprache (mit IAR C-Compiler), mit Anzeige sämtlicher Prozessor-Ressourcen. Es werden nur wenige Derivate der MSP430-Reihe unterstützt.

Übertaktung

Ein unfreiwilliges Eingeständnis von TI zur Übertaktung zeigt das Entwicklungstool eZ430: Es beinhaltet als Hostrechner für die USB-Bridge einen MSP430F169. Laut Datenblatt hat dieser eine maximale Taktfrequenz von 8 MHz. Der Quarz für diesen Baustein ist aber ein 12-MHz-Typ[3]. Somit gibt TI hier ein eigenes Produkt mit einer Übertaktung von 50 % in den Markt.

MSP432

Am 24. März 2015 stellte Texas Instruments eine neue Familie mit einer 32-bit-CPU des Typs Arm Cortex-M4 vor. Die meisten Peripherieelemente stellen sich – selbst wenn sie technisch neu entwickelt oder verbessert wurden – aus Entwicklersicht wie beim MSP430 dar, so dass eine Codeportierung vom MSP430 zum MSP432 vergleichsweise einfach umgesetzt werden kann.[4]

Literatur

- Lutz Bierl: Das große MSP430 Praxisbuch. Franzis, München 2004, ISBN 978-3-7723-4299-8.

- John H. Davies: MSP430 Microcontroller Basics. 1. Auflage. Newnes, 2008, ISBN 978-0-7506-8276-3.

- Marian Walter, Stefan Tappertzhofen: Das MSP430 Mikrokontroller Buch. 1. Auflage. Elektor, 2011, ISBN 978-3-89576-236-9.

- Matthias Sturm: Mikrocontrollertechnik. 2. Auflage. Carl Hanser Verlag, München 2011, ISBN 978-3-446-42231-5.

Einzelnachweise

- Überblick über die FRAM-Technologie MSP430 Webseite

- Application Note - Features of the MSP430 Bootstrap Loader

- slau176d Seite 9 (PDF; 283 kB)

- Frank Riemenschneider: TIs MSP432-Mikrocontroller mit ARM Cortex-M4. Artikel bei Elektroniknet.de vom 24. März 2015.

Weblinks

- MSP430-Homepage

- GCC für MSP430

- Installationsanleitung der MSPGCC Toolchain + Eclipse + msp430-gdbproxy (Tutorial) Betriebssystem: Linux / Debian / Ubuntu

- Zahlreiche Tutorials und Beispielprojekte, u. a. (G)LCD, USART, I2C, CAN

- Technical Documents MSP430 Memory Programming User's Guide

- Mikrocontroller.net - Artikel zum MSP430