Joint Test Action Group

Joint Test Action Group (kurz JTAG) ist ein häufig verwendetes Synonym für den IEEE-Standard 1149.1, der eine Methodik für das Testen und Debuggen integrierter Schaltungen, also Hardware auf Leiterplatten, beschreibt. Das prominenteste und gleichzeitig zuerst in der JTAG-Arbeitsgruppe implementierte Verfahren ist der Boundary Scan Test nach IEEE 1149.1. Durch Hinzufügen weiterer Verfahren (1149.1–1149.8) sind die Begriffe nicht mehr synonym, während die Beschreibungssprache von der IEEE-Arbeitsgruppe mit Boundary Scan Description Language den ursprünglichen Namen beibehielt.

Zweck des Verfahrens ist es, integrierte Schaltungen (ICs) auf Funktion zu testen, während sie sich bereits in ihrer Arbeitsumgebung befinden, beispielsweise verlötet auf einer Platine. Dazu besitzt ein JTAG-fähiges Gerät IC Komponenten, die im Normalbetrieb vollkommen abgetrennt sind und somit die Funktion des Bauteils nicht stören. Erst durch Aktivierung der JTAG-Funktion an einem bestimmten Pin, dem Test Mode Select Input, kann mit Hilfe dieser zusätzlichen Komponenten das Hardwaresystem beeinflusst und dadurch kontrolliert werden. Die Schnittstelle von JTAG zur Außenwelt ist als Schieberegister implementiert.

Motivation und Entwicklung

Ende der 1970er Jahre war der Integrationsgrad der Mikroelektronik soweit gestiegen (zeitgenössische komplexe IC sind Intel 4004, Intel 8008 oder Zilog Z80), dass ICs mit tausenden Flipflops bzw. Registern in einem Chip arbeiteten. Die Zustände dieser internen Flipflops sind bei einem IC nicht mehr zugänglich. Es entstand die Forderung (zunächst der IC-Hersteller selbst), dass zum Test der Struktur eines komplexen Bausteins dessen Gatter und Leitungen steuerbar, zum Test der Funktion die Zustände (aller Register und Flipflops) beobachtbar sein sollten. Eichelberger veröffentlichte 1977[1] einen als Scan-Path bezeichneten Lösungsansatz, bei dem jedes Flipflop im IC einen zusätzlichen Multiplexer (Transfergate) am Eingang erhält. Auf diese Weise können nun alle Flipflops des IC wahlweise zu einem langen Schieberegister zusammengeschaltet werden, über das jeder Zustand jedes Flipflops von außen beobachtbar und steuerbar wird.

Der JTAG-Standard entstand durch einen Zusammenschluss von Halbleiterherstellern im Jahr 1985/86. Es wurde ein Standard erarbeitet, der in der Norm IEEE 1149.1–1990 festgehalten wurde. Mit der Überarbeitung IEEE 1149.1–1994 ist die Boundary Scan Description Language Teil des Standards. Die aktuelle Version des Standards ist 1149.1-2001 IEEE standard test access port and boundary-scan architecture.[2]

Funktionsweise

Aufbau

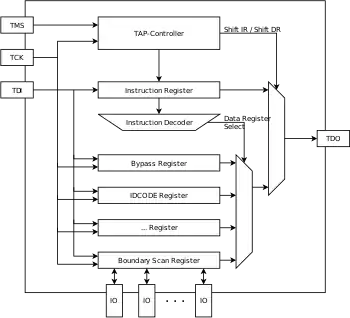

Eine JTAG-Komponente besteht im Wesentlichen aus folgenden Teilen:

- Dem Test Access Port (TAP) mit den Steuerleitungen, im Allgemeinen auch JTAG-Port oder JTAG-Schnittstelle genannt.

- Dem TAP-Controller, einer State-Machine, welche die Testlogik steuert.

- Zwei Schieberegistern, dem „Instruction Register“ (IR) und dem „Data Register“ (DR).

Test Access Port

Der Test Access Port (TAP) besteht aus fünf Steuerleitungen:

- Test Data Input (TDI). Serieller Eingang der Schieberegister.

- Test Data Output (TDO). Serieller Ausgang der Schieberegister.

- Test Clock (TCK). Das Taktsignal für die gesamte Testlogik.

- Test Mode Select (TMS). Diese steuert die State Machine des TAP-Controllers.

- Test Reset (TRST). Reset der Testlogik. Diese Leitung ist optional, da ein Reset auch über den TAP-Controller ausgelöst werden kann.

Verdrahtung in der Gesamtschaltung

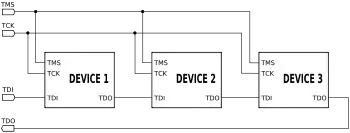

An einem Hardwaresystem können mehrere TAPs vorhanden sein, die miteinander verkettet sind. Das wird als „JTAG-Chain“ bezeichnet. Effektiv kommt es in der Regel dabei zu einer Reihenschaltung der Schieberegister der beteiligten TAPs, wobei aber auch andere Schaltungsmuster im JTAG-Standard definiert sind. Die TAP-Controller der einzelnen TAPs laufen dabei parallel.

TAP-Controller

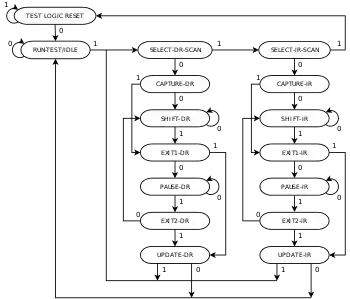

Der TAP-Controller ist ein von TCK getakteter und von der TMS-Leitung gesteuerter Zustandsautomat. Die TMS-Leitung bestimmt dabei, in welchen Folgezustand beim nächsten Takt gesprungen wird. Der TAP-Controller hat sechs stabile Zustände, das heißt Zustände, in denen mehrere Takte lang verblieben werden kann. Diese sechs Zustände sind „Test Logic Reset“, „Run Test / Idle“, „Shift-DR“ und „Shift-IR“ sowie „Pause-DR“ und „Pause-IR“. Im Zustand „Test Logic Reset“ wird die Testlogik zurückgesetzt, „Run Test / Idle“ wird als Ruhezustand oder für Wartezeiten benutzt. Die beiden „Shift“-Zustände schieben jeweils das DR- oder IR-Schieberegister. Die beiden „Pause“-Zustände dienen der Unterbrechung von Schiebeoperationen. Aus allen anderen Zuständen wird beim folgenden Takt in einen anderen Zustand gesprungen. Beim Durchlaufen werden jeweils bestimmte Steuerfunktionen ausgelöst.

Register

Ein IC mit JTAG-Port verfügt nach außen über zwei Register, das Instruction Register (IR) und das Data Register (DR). Das Data Register steht dabei für eine Gruppe von verschiedenen Registern, die an der Übertragung von Nutzdaten beteiligt sind.

Bei einer Schiebeoperation wird dabei der TDI-Eingang in das vorderste Bit des Schieberegisters „hineingeschoben“, das hinterste Bit des Schieberegisters wird zum TDO-Ausgang „hinausgeschoben“. Sind mehrere TAPs in einer JTAG-Chain hintereinandergeschaltet, müssen Informationen, die für einen bestimmten TAP gedacht sind, durch die Schieberegister der anderen TAPs hindurchgeschoben werden. Welches der beiden Register (IR oder DR) geschoben wird, hängt davon ab, ob sich der TAP-Controller im DR- oder im IR-Zweig befindet.

Das Instruction Register

Wenn eine Schiebeoperation durch die Datenregister (DR, siehe unten) erfolgt, gibt der Wert des Instruction Register (IR) an, durch welches der Datenregister die Schiebeoperation erfolgt. Aufgrund der Verschaltung der Schieberegister können die Instruction Register aller Bausteine in einer JTAG-Chain nur gemeinsam geschrieben werden.

Das IR hat keine festgelegte Länge, muss allerdings mindestens 2 Bit groß sein. Bei einigen Mikrocontrollern ist es 4 Bit (z. B. ARM, Maxim/Dallas DS4550, Renesas SH-Mikrocontroller), bei anderen 5 Bit (z. B. Freescale MPC5554) oder auch 8 Bit (z. B. Infineon C166) breit.

Bestimmte Werte des IR können vom TAP bei Beendigung der Schiebeoperation als Kommando interpretiert werden. Beim Auslesen wird das Instruction Register oft als Statusregister benutzt.

Die Data Register

Als Data Register (DR) werden diejenigen Register bezeichnet, die an der Übertragung von Nutzdaten beteiligt sind. Hardwareseitig ist das oft ein einzelnes Schieberegister, welches die Aufgabe des jeweiligen JTAG-Registers übernimmt. Welches Register darauf abgebildet wird, wird vom Instruction Register bestimmt. Das kann als Steuerung eines Multiplexers verstanden werden, der die Datenregister auf den TDO-Ausgang multiplext. Der IEEE 1149.1-Standard schreibt bestimmte Register vor, die in allen JTAG-fähigen Bausteinen enthalten sein müssen. Das sind das BYPASS-, das IDCODES- und das Boundary-Scan-Register.

Das BYPASS-Register

Bei diesem Datenregister handelt es sich um ein Schieberegister mit einem Bit Breite. Hintergrund ist, dass die Datenregister (DR) aller TAPs wie beim IR nur gleichzeitig gelesen und beschrieben werden können. Soll nur das Datenregister eines einzelnen TAP in der JTAG-Chain gelesen oder geschrieben werden, so wird über die IRs aller anderen TAPs die BYPASS-Instruktion geladen, so dass dieses Register ausgewählt wird. Dadurch kann die Latenz der Scan-Chain, welche durch den Schiebevorgang entsteht, minimiert werden.

Das IDCODES-Register

Beim Beginn einer Schiebeoperation durch dieses Datenregister (DR) wird eine Identifikationsnummer (Hersteller und Produkttyp) in das Schieberegister geladen, die zur Identifizierung des TAP dient.

Das Boundary-Scan-Register

Die einzelnen Speicherzellen des Boundary-Scan-Register (BSR) erlauben den Zugriff auf die an den TAP angeschlossenen Logikschaltungen. Das können für spezielle Scan Tests benötigte Schaltungen sein oder auch ganze In-Circuit-Emulatoren darstellen. Die genaue Bedeutung ist herstellerabhängig. Ähnlich wie bei einer speicherprogrammierbaren Steuerung kann mit dem Boundary-Scan-Register der Spannungspegel aller Ausgänge bestimmt und die Spannungspegel aller Eingänge gelesen werden. Das wird für Scan Tests genutzt.

Weitere Register

Über die drei vorgeschriebenen Datenregister hinaus können noch zusätzliche Register definiert werden, die beispielsweise eine Debug- oder Programmierschnittstelle zur Verfügung stellen. So verfügt beispielsweise im Fall von ARMv5 der TAP über drei spezielle Register, die als Datenregister (DR) angesprochen werden.

Um den JTAG-Port eines IC nutzen zu können, ist es notwendig, seinen Aufbau und die enthaltenen Register genau zu kennen. Das wird in einer vom Hersteller bereitgestellten BSDL-Datei beschrieben.

Weitere Anwendungen

Inzwischen wird JTAG vermehrt auch zur Konfiguration von FPGAs und CPLDs sowie zum Programmieren und zum Debuggen von Mikrocontrollern verwendet. Parallel programmierbare Speicher wie zum Beispiel Flashspeicher, die direkt an ein IC mit JTAG-Port angeschlossen sind, können deshalb im eingebauten Zustand umprogrammiert werden, weil der IC für den Speicherchip ein Programmiergerät emulieren kann. Zum Austausch solcher Programmierdaten dient oft das Serial Vector Format (SVF).

JTAG und Computer-Sicherheit

Wegen des direkten Hardware-Zugriffs per JTAG eignet sich die Schnittstelle dafür, Sicherheitsmaßnahmen zu umgehen.[3] Daher wird der Begriff JTAG vielfach – und nicht immer mit einheitlicher Definition – im Kontext der Hackerszene verwendet. Gamer sprechen von einer jtagged XBox, wenn Modding-Techniken benutzt wurden, um auf einer Spielekonsole Inhalte ohne Herstellersignatur laufen lassen zu können. Im Hardware-Kontext wird JTAG synonym mit Debugging verwendet, was im Software-Bereich irreführend sein kann.

JTAG kann besonders dafür verwendet werden, den Bootprozess von Geräten zu erkunden, mit dem Ziel ihn zu unterbrechen und durch Code Injection die Kontrolle über das Gerät zu erlangen. Um diesen Zugriff zu verhindern, werden bei ICs häufig die JTAG-Ports nicht als solche markiert oder aktiv verschleiert. Weitere Sicherheitsmaßnahmen sind eine nachträgliche Maskierung der Pins, ein Gehäuse, das die JTAG-Pins abdeckt oder Schmelzsicherungen in den JTAG-Verbindungen, die nach Abschluss der Tests zerstört werden. Der Zugang zu JTAG-Ports kann daher erschwert sein, ist aber mit entsprechendem Aufwand in praktisch jedem Fall möglich.

Der Zugang auf Hardware über JTAG-Ports könnte nur unterbunden werden, wenn der Zugriff selbst über Verschlüsselung oder Authentifikation verfügen würde. Verschiedene Entwürfe dazu wurden vorgelegt, es gibt aber keine Standards und nur wenige Implementationen.[3]

Erweiterungen

Der IEEE-Standard 1149.1 wurde inzwischen mit einer Anzahl Erweiterungen versehen. Das sind:

- 1149.4: IEEE Standard for a Mixed-Signal Test Bus, Testen von analogen Schaltkreisen.[4]

- 1149.5: IEEE Standard for Module Test and Maintenance Bus (MTM-Bus) Protocol, wurde 2003 zurückgezogen.[5]

- 1149.6: IEEE Standard for Boundary-Scan Testing of Advanced Digital Networks, Testen von Differenzsignalen, auch mit AC-Kopplung.[6]

- 1149.7: IEEE Standard for Boundary-Scan Testing of Advanced Digital Networks, vereinfachter Test-Port mit nur zwei Signalen.[7]

Eine weitere Erweiterung des JTAG-Standards, speziell zum Programmieren von JTAG-fähigen Bausteinen wurde unter der Bezeichnung IEEE Std 1532-2002: IEEE Standard for In-System Configuration of Programmable Devices[8] verabschiedet. Ein diesem Standard entsprechender Baustein verfügt über bestimmte zusätzliche Register, die für seine Programmierung vorgesehen sind.

Siehe auch

Einzelnachweise

- Edward Eichelberger, Thomas Williams: A logic Design Structure for LSI Testability. In: Proceedings of the 14th Design Automation Conference. June 1977, S. 462–468.

- IEEE OPAC: IEEE Std 1149.1-2001 IEEE standard test access port and boundary-scan architecture doi:10.1109/IEEESTD.2001.92950

- Senrio: JTAG Explained, 28. September 2016

- IEEE OPAC: IEEE Std 1149.4-1999: IEEE Standard for a Mixed-Signal Test Bus doi:10.1109/IEEESTD.2000.91314

- IEEE Std 1149.5-1995: IEEE Standard for Module Test and Maintenance Bus (MTM-Bus) Protocol (Memento des Originals vom 9. Februar 2009 im Internet Archive) Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis.

- IEEE OPAC: IEEE Std 1149.6-2003: IEEE Standard for Boundary-Scan Testing of Advanced Digital Networks doi:10.1109/IEEESTD.2003.94249

- IEEE OPAC: IEEE Std 1149.7-2009: IEEE Standard for Reduced-Pin and Enhanced-Functionality Test Access Port and Boundary-Scan Architecture doi:10.1109/IEEESTD.2010.5412866

- IEEE OPAC: IEEE Std 1532-2002: IEEE Standard for In-System Configuration of Programmable Devices doi:10.1109/IEEESTD.2003.94229

Weblinks

- Boundary-Scan Tutorial (englisch)

- JTAG-FAQ (englisch)

- Free JTAG/Boundary Scan Resources (englisch)

- Overview of JTAG technology (englisch)

- goJTAG - free and open source alternative (englisch)