PicoBlaze

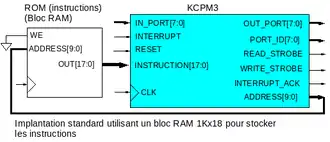

Als PicoBlaze wird eine ausschließlich in FPGAs und CPLDs der Firma Xilinx verwendbare Prozessorfamilie bezeichnet. Die Prozessoren existieren nicht als physische Hardware, sondern sind in den Hardwarebeschreibungssprachen VHDL und Verilog als sogenannte Softcores verfügbar, was ihre Erweiterung durch Hinzufügen von Peripherie zu kleinen Mikrocontrollern sehr einfach macht.

Durch die spezielle Optimierung auf die Besonderheiten bestimmter FPGA/CPLD-Bausteine der Firma Xilinx ist der Logikbedarf der Prozessoren sehr gering. Nachteilig ist, dass durch die Optimierung und durch rechtliche Beschränkungen PicoBlaze-Prozessoren nur auf FPGAs und CPLDs der Firma Xilinx verwendet werden können und dürfen.

Die Stärke der PicoBlaze-Prozessoren liegt im Einsatz als Finite State Machine, wobei diese aber nicht besonders zeitkritisch sein sollte. Implementierung von Finite State Machines direkt in der Hardwarebeschreibungssprache sind je nach Umfang der Zustände stark größenabhängig, was durch den Einsatz eines PicoBlaze-Prozessors vermieden werden kann. Dadurch vereinfacht sich die Entwicklung der restlichen Hardware. Aufgrund eines vergleichsweise eher geringen Leistungsumfangs von PicoBlaze-Prozessoren sollten bei komplexeren Aufgaben andere, leistungsfähigere Prozessoren bzw. Mikrocontroller wie der ebenfalls von Xilinx für FPGAs als Softcore verfügbare MicroBlaze verwendet werden.

PicoBlaze-Prozessoren hießen ursprünglich KCPSM, was eine Abkürzung für Constant(k) Coded Programmable State Machine ist. Oft wird angenommen, KCPSM sei eine Abkürzung für Ken Chapman’s Programmable State Machine. Ken Chapman, der Entwickler der PicoBlaze-Prozessoren bei Xilinx, dementiert dies allerdings mit Augenzwinkern.

PicoBlaze-Familie

Die PicoBlaze-Prozessorfamilie umfasst die folgenden Derivate:

- PicoBlaze CPLD (optimiert für Xilinx CoolRunner-II CPLDs)

- PicoBlaze (optimiert für Xilinx Virtex-E and Spartan-II/IIE FPGAs)

- PicoBlaze II (optimiert für Xilinx Virtex-II FPGAs)

- PicoBlaze 3 (optimiert für Xilinx Spartan-3 und neuere Spartan, Virtex-II, Virtex-II Pro, Virtex 4 und neuere Virtex FPGAs)

- PicoBlaze 6 (optimiert für Xilinx Spartan-6 und neuere Spartan, Virtex-6 und neuere Virtex FPGAs)

Hardware-Merkmale

PicoBlaze-Prozessoren basieren auf einer 8-Bit RISC-Architektur. Die Geschwindigkeit variiert stark mit der eingesetzten Hardware, kann jedoch weit über 100 MIPS erreichen. Für die Ausführung einer Instruktion werden jeweils zwei Taktzyklen benötigt.

| Merkmal | PicoBlaze | PicoBlaze II | PicoBlaze 3 | PicoBlaze 6 | PicoBlaze CPLD |

|---|---|---|---|---|---|

| Anzahl IO-Portadressen | 256 | 256 | 256 | 256 | 256 |

| Anzahl Register | 16 | 32 | 16 | 2 × 16 | 8 |

| Scratchpad-Größe [in Byte] | – | – | 64 | 64 / 128 / 256 | – |

| Callstack-Größe | 15 | 31 | 31 | 30 | 4 |

| Max. Programmgröße [in Befehlen] | 256 | 1024 | 1024 | 1024 / 2048 / 4096 | 256 |

- IO-Ports

- PicoBlaze-Prozessoren besitzen je einen 8 Bit breiten Ein- und Ausgabeport, die über 8-Bit-Port-IDs adressiert werden können, woraus sich theoretisch 256 Ein- und Ausgabeports ergeben. Praktisch wird die tatsächlich mögliche Anzahl von Portadressen jedoch von der durch die Beschaltung entstehenden Signallaufzeit sowie die verwendete Taktfrequenz eingeschränkt.

- Register

- Die PicoBlaze-Prozessoren verfügen über eine unterschiedliche Anzahl von 8-Bit-Registern. Die Register sind funktional identisch und können mit allen Register-Befehlen gleichermaßen verwendet werden. Der PicoBlaze 6 verfügt über zwei Registerbänke, welche jeweils 16 Register enthalten.

- Scratchpad

- Das Scratchpad ist ein RAM-Speicher, in welchen mit den Befehlen STORE und FETCH Registerwerte gespeichert oder zurückgelesen werden können. Zum Teil kann die Scratchpad-Größe über Parameter festgelegt werden.

- Callstack

- Der Callstack sämtlicher PicoBlaze-Prozessoren wird sowohl für CALL-Aufrufe als auch für Interrupts gemeinsam verwendet.

Befehlssatz

Der PicoBlaze besitzt einen kleinen Befehlssatz, der auf die wichtigsten Befehle begrenzt ist.

| Befehl | PicoBlaze | PicoBlaze II | PicoBlaze 3 | PicoBlaze 6 | PicoBlaze CPLD |

|---|---|---|---|---|---|

| Programmfluss | |||||

| JUMP | ja | ja | ja | ja | ja |

| CALL | ja | ja | ja | ja | ja |

| RET | ja | ja | ja | ja | ja |

| Interrupt | |||||

| RETI | ja | ja | ja | ja | ja |

| EINT | ja | ja | ja | ja | ja |

| DINT | ja | ja | ja | ja | ja |

| Logik | |||||

| AND | ja | ja | ja | ja | ja |

| OR | ja | ja | ja | ja | ja |

| XOR | ja | ja | ja | ja | ja |

| COMP | nein | nein | ja | ja | nein |

| COMPC | nein | nein | nein | ja | nein |

| TEST | nein | nein | ja | ja | nein |

| TESTC | nein | nein | nein | ja | nein |

| Arithmetik | |||||

| ADD | ja | ja | ja | ja | ja |

| ADDC | ja | ja | ja | ja1 | ja |

| SUB | ja | ja | ja | ja | ja |

| SUBC | ja | ja | ja | ja1 | ja |

| Befehl | PicoBlaze | PicoBlaze II | PicoBlaze 3 | PicoBlaze 6 | PicoBlaze CPLD |

|---|---|---|---|---|---|

| Schiebe- und Rotationsbefehle | |||||

| SR0 | ja | ja | ja | ja | ja |

| SR1 | ja | ja | ja | ja | ja |

| SRX | ja | ja | ja | ja | ja |

| SRA | ja | ja | ja | ja | ja |

| RR | ja | ja | ja | ja | ja |

| SL0 | ja | ja | ja | ja | ja |

| SL1 | ja | ja | ja | ja | ja |

| SLX | ja | ja | ja | ja | ja |

| SLA | ja | ja | ja | ja | ja |

| RL | ja | ja | ja | ja | ja |

| Ein-/Ausgabe, Daten bewegen | |||||

| REGBANK | nein | nein | nein | ja | nein |

| LOAD | ja | ja | ja | ja | ja |

| LOADRET | nein | nein | nein | ja | nein |

| IN | ja | ja | ja | ja | ja |

| OUT | ja | ja | ja | ja | ja |

| FETCH | nein | nein | ja | ja | nein |

| STORE | nein | nein | ja | ja | nein |

| STAR | nein | nein | nein | ja | nein |

| NOP | ja | ja | ja | ja | ja |

Für weitere Details zu den Befehlen können die Application Notes zu Rate gezogen werden (siehe Weblinks).

Programmierung

Die PicoBlaze-Prozessoren werden ihrer Einfachheit wegen praktisch ausschließlich in Assembler programmiert. Da es von Xilinx lediglich DOS-Compiler gibt, wurden von der Community verschiedene Integrierte Entwicklungsumgebungen hervorgebracht, welche sowohl Editoren als auch Compiler und Simulatoren zur Verfügung stellen.

PicoBlaze-Prozessoren werden üblicherweise nicht wie herkömmliche Prozessoren oder Mikrocontroller direkt programmiert, da der Zugriff auf den Programmspeicher von außerhalb des FPGAs/CPLDs nur bedingt möglich ist. Stattdessen wird mit einem der zahlreichen Compiler eine vorinitialisierte VHDL/Verilog-Programmspeicherinstanz erzeugt, welche mit der Prozessorinstanz zusammen in die eigene Schaltung eingebunden werden kann. Die Compiler verwenden hierzu eine VHDL/Verilog-Vorlage, welche eingelesen und ergänzt wird. So ist es möglich, auf den Programmspeichertyp Einfluss zu nehmen, was die Verwendung von Dual-Port-Speicherblöcken als Programmspeicher ermöglicht.

Bei Verwendung von Dual-Port-Speicherblöcken als Programmspeicher können optional zwei PicoBlaze-Prozessoren mit demselben Speicher/Programm arbeiten oder der Programmspeicher unter Verwendung zusätzlicher Logik zur Laufzeit verändert werden.

Fehlersuche

Da der Zugriff auf die interne Prozessorhardware im FPGA/CPLD nicht möglich ist, können PicoBlaze-Prozessoren nicht wie herkömmliche Prozessoren oder Mikrocontroller direkt zur Laufzeit diagnostiziert werden. PicoBlaze-Prozessoren sind in der Regel nahtlos in den eigenen VHDL/Verilog-Code integriert, weshalb dieser Umstand keinen Verlust bedeutet, da generell der gesamte Code (VHDL/Verilog, PicoBlaze-Programm) mit einem VHDL/Verilog-Simulator diagnostiziert werden sollte, denn eine Fehlfunktion des FPGAs/CPLDs kann sowohl durch den VHDL/Verilog- als auch durch den Prozessorcode hervorgerufen werden.

Für die abstrakte Betrachtung des Prozessorcodes stehen verschiedene PicoBlaze-Simulatoren zur Verfügung.

Weblinks

Xilinx-Links

- PicoBlaze for Extended Spartan-3A Family, Virtex-4, Virtex-II, and Virtex-II Pro FPGAs (Memento vom 1. September 2010 im Internet Archive). Download PicoBlaze von der Xilinx Website.

- Dokumentation PicoBlaze auf der Xilinx Webseite

Community-Links

- MDS – eine PicoBlaze-IDE mit MacroAssembler für Linux und Windows

- FIDEx – eine PicoBlaze-Assembler-IDE für Linux, Mac und Windows (PicoBlaze-Familie und weitere Soft-Core-Prozessoren)

- kpicosim – eine PicoBlaze-Assembler-IDE für Linux (PicoBlaze 3, seit 2006 nicht mehr weiterentwickelt)

- pBlazXYZ – verschiedene Tools für Linux und Windows

- PauloBlaze – eine vollständig zum PicoBlaze 6 kompatible VHDL Implementierung