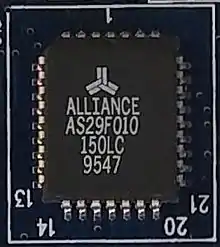

Electrically Erasable Programmable Read-Only Memory

Ein EEPROM (engl. Abk. für electrically erasable programmable read-only memory, wörtlich: elektrisch löschbarer programmierbarer Nur-Lese-Speicher, auch E2PROM) ist ein nichtflüchtiger, elektronischer Speicherbaustein, dessen gespeicherte Information elektrisch gelöscht werden kann. Er ist verwandt mit anderen löschbaren Speichern, wie dem durch UV-Licht löschbaren EPROMs und dem ebenfalls elektrisch löschbaren Flash-Speicher. Er wird verwendet zur Speicherung kleinerer Datenmengen in elektrischen Geräten, bei denen die Information auch ohne anliegende Versorgungsspannung erhalten bleiben muss oder bei denen einzelne Speicherelemente bzw. Datenworte einfach zu ändern sein müssen. Zur Speicherung größerer Datenmengen wie z. B. dem BIOS in PC-Systemen sind meist Flash-Speicher ökonomischer.

Funktionsweise

Der Ausdruck „EEPROM“ beschreibt lediglich die Eigenschaften des Speichers, dass dieser nicht-flüchtig ist und allein mit elektrischer Energie gelöscht werden kann (im Gegensatz zu dem nur durch UV-Licht löschbaren EPROM). Der Ausdruck „EEPROM“ umfasst deshalb genau genommen die heute üblicherweise als EEPROM bezeichneten wort- oder byteweise löschbaren Speicher, als auch die neueren blockweise löschbaren Flashspeicher. Da bei letzteren die sonst pro Speicherzelle notwendigen Schreib-, Lese- und Löschtransistoren entfallen können, ist mit ihnen eine deutliche höhere Speicherdichte erreichbar.

Ein EEPROM besteht aus einer Matrix aus Feldeffekttransistoren (FETs) mit isoliertem Steueranschluss (Floating Gate), in der jeder dieser FETs ein Bit repräsentiert. Beim Programmiervorgang wird auf das Floating Gate eine Ladung eingebracht, die nur durch den Löschvorgang wieder entfernt werden kann. Im Normalbetrieb bleibt die Ladung auf dem vollständig isolierten Gate erhalten.

Bei (UV-löschbaren) EPROMs wird beim Schreiben die Ladung durch Injektion heißer Ladungsträger (engl. hot-carrier injection, HCI) auf das Gate gebracht und kann nur durch Bestrahlung mit UV-Licht wieder entfernt werden.

Bei EEPROMs wird sowohl beim Schreiben als auch Löschen die Ladung durch Fowler-Nordheim-Tunneln auf das isolierte Gate aufgebracht bzw. von diesem entfernt.

Beim Flash-Speicher hingegen wird die Ladung beim Schreiben durch HCI auf das Gate aufgebracht und beim Löschen durch Fowler-Nordheim-Tunneln wieder entfernt.

Zum Programmieren des EEPROMs wird ein hoher Spannungspuls an das Control Gate gelegt, wobei ein Tunnelstrom von diesem durch das isolierende Dielektrikum auf das Floating Gate fließt. Diese hohe Spannung musste bei EPROMs von außen an den Speicherbaustein angelegt werden, während sie beim EEPROM, und auch bei den Flash-Speichern, baustein-intern erzeugt wird.

Nach dem Schreiben des Speichers, d. h. dem selektiven Aufbringen von Ladung auf die Floating Gates, werden die geschriebenen Daten durch ein Bitmuster geladener/ungeladener Gates repräsentiert. Diese Daten lassen sich nun über die Drain-Source-Anschlüsse der Transistoren beliebig oft auslesen, wobei die normale Betriebsspannung beim Lesen weit unterhalb der Programmierspannung liegt. Die Anzahl der möglichen Schreibvorgänge der einzelnen Speicherzellen ist allerdings begrenzt, die Hersteller garantieren üblicherweise einige 10.000 bis über 1.000.000 Schreibzyklen. Dieses wird zum Teil durch redundante Speicherzellen erreicht.

Anwendungsgebiete

EEPROMs können im Unterschied zu Flash-EEPROMs byteweise beschrieben und gelöscht werden. Im Vergleich zu Flash-EEPROMs, die zwischen 1 μs und 1 ms für einen Schreibzyklus benötigen, sind herkömmliche EEPROMs mit 1 ms bis 10 ms erheblich langsamer. EEPROMs verwendet man deshalb bevorzugt, wenn einzelne Datenbytes in größeren Zeitabständen verändert und netzausfallsicher gespeichert werden müssen, wie zum Beispiel bei Konfigurationsdaten oder Betriebsstundenzählern.

Als Ersatz für die früher als Programm- oder Tabellenspeicher dienenden ROMs oder EPROMs eignete sich das EEPROM aufgrund der deutlich höheren Herstellungskosten nicht, diese Rolle wurde später durch die Flash-Speicher übernommen. Die höheren Kosten der EEPROM-Technologie führten dazu, dass zunächst eigenständige EEPROM-Bausteine zumeist über ein serielles Interface an die Mikrocontroller angeschlossen wurden. Später wurden dann bei etlichen Mikrocontrollern auch On-Chip-EEPROMs angeboten. Da Mikrocontroller heute meist sowieso in robusten Flashtechnologien hergestellt werden, die ein häufigeres Löschen und Programmieren erlauben, kann meist auch ein Bereich des Flash-Speichers für veränderliche Daten verwendet werden. Dazu wird ein Teilbereich des Flashspeichers reserviert und z. T. mit speziellen Algorithmen beschrieben und gelesen[1]. Dabei muss ein Block (Page) vor der Löschung, ebenso wie der gesamte reservierte Bereich, erst komplett ausgenutzt sein, bevor er neu beschrieben wird. Dieses Verfahren macht in vielen Fällen das EEPROM in Mikrocontrollern überflüssig.

Allerdings lässt sich ein EEPROM nicht in allen Anwendungen durch Flash ersetzen:

Zum einen ist es z. Z. noch nicht möglich, Flash über einen so weiten Temperaturbereich wie EEPROMs zuverlässig zu beschreiben. Allerdings macht hier die Prozesstechnik Fortschritte und Temperaturkompensation beim Schreiben verbessert das Verhalten.

Zum anderen kann es in bestimmten Anwendungen problematisch sein, wenn eine Page gelöscht werden soll, aber wegen der EEPROM-Emulation mittels Flash nicht sofort gelöscht werden kann, und es damit nicht feststeht, wann die Page gelöscht werden wird (was aber umgangen werden könnte, indem die Page eben, wenn sie gelöscht werden soll, zuerst absichtlich / gezielt vollgeschrieben wird).

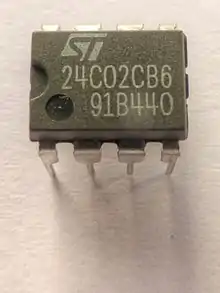

Neben Bausteinen mit parallel herausgeführten Adress- und Datenbussen gibt es auch EEPROMs in Gehäusen mit z. B. nur 8 Anschlüssen, bei denen Adressen und Daten über einen seriellen Bus wie I²C ausgetauscht werden. Derartige EEPROMs werden z. B. auf SDRAM-Modulen vom Hersteller zur Speicherung von Produktparametern verwendet, die dann von der CPU ausgelesen werden können. Mit dieser Information im SPD-EEPROM können die Speichermodule im PC dann automatisch konfiguriert werden.

Ausfallerscheinungen und Lebensdauer

In EEPROMs gespeicherte Daten können von drei Arten von Ausfallerscheinungen betroffen sein:

- dem ungewollten Überschreiben benachbarter Speicherzellen, wenn eine Speicherzelle geändert wird (bezeichnet als „write disturb“),

- dem begrenzten Erhaltungsvermögen des Speicherzustands der einzelnen Speicherplätze im EEPROM („retention“) und

- der begrenzten Lebensdauer bzw. Beschreibbarkeit („byte endurance“)[2][3].

In der Oxidschicht des Gates der in EEPROMs eingesetzten Floating-Gate-Transistoren sammeln sich eingefangene Elektronen an. Das elektrische Feld der eingefangenen Elektronen summiert sich zu dem Feld des Floating Gates und schmälert so das Fenster zwischen den Schwellenspannungen, die für die Speicherzustände Eins bzw. Null stehen. Nach einer bestimmten Anzahl von Schreibvorgängen wird die Differenz zu klein, um unterscheidbar zu bleiben, und die Speicherstelle bleibt dauerhaft auf dem programmierten Wert stehen. Hersteller geben üblicherweise die maximale Anzahl von Schreibvorgängen mit 106 oder mehr an.

Die während der Speicherung in das Floating Gate eingebrachten Elektronen können durch die Isolierschicht lecken, dies vor allem bei erhöhten Temperaturen (z. B. 170…180 °C), dadurch einen Verlust des Ladungszustands verursachen und die Speicherstelle so in den gelöschten Zustand zurückversetzen. Hersteller gewährleisten üblicherweise die Beständigkeit gespeicherter Daten für einen Zeitraum von 10 Jahren[4].

Beim Beschreiben von Speicherzellen wird der Inhalt benachbarter Zellen dann verändert, wenn nach der letzten Änderung der Nachbarzelle insgesamt eine Anzahl von Schreibvorgängen auf dem Chip erfolgte (z. B. Zelle 0x0000 geändert, Zelle 0x0001 aktuell nicht geändert und nach der letzten Änderung von 0x0001 bisher an beliebiger Stelle insgesamt 1 Mio. Schreibvorgänge insgesamt dadurch dann Gefahr von Datenverlust auf Zelle 0x0001). Somit kann die Angabe für „write disturb“ zehnmal größer sein als die Angabe für „byte endurance“. Kurz bevor „write disturb“ erreicht wird, sollte ein Refresh des gesamten EEPROM erfolgen. Es wird jede Speicherzelle einzeln gelesen und neu beschrieben. Möglich ist auch, erst zu lesen dann zu löschen und danach neu zu schreiben.

Literatur

- Leonhard Stiny: Das EEPROM, ein besonderer Speicher, MC, 7/1982, S. 44–48.

Weblinks

Einzelnachweise

- Algorithmus zum Ersatz von EEPROM durch Flash-Speicher

- Lynn Reed, Vema Reddy "The Effects of Repeated Refresh Cycles on the Oxide Integrity of EEPROM Memories at High Temperature" Tekmos Inc.

- EEPROM endurance, Online Quelle

- System Integration - From Transistor Design to Large Scale Integrated Circuits