OpenRISC

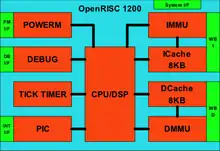

OpenRISC ist ein Projekt der OpenCores-Entwickler-Community. Das Ziel des Projekts ist die Entwicklung einer hochkonfigurierbaren RISC-CPU als Open Hardware. Die bisher einzige fertiggestellte Architektur ist die OpenRISC-1000-Familie (kurz OR1k), die als 32- und 64-Bit-Version verfügbar ist.[1] Das Design des OpenRISC 1200 (kurz OR1200) war das erste, das in der Hardwarebeschreibungssprache Verilog unter der GNU Lesser General Public License (GNU LGPL) veröffentlicht wurde. Die Firmware und der Microcode zum Prozessor wurden unter der GNU General Public License (GNU GPL) bereitgestellt. Basierend auf dem OpenRISC 1200 wurde eine System-on-a-Chip-Variante mit der Bezeichnung ORPSoC (= OpenRISC Reference Platform System-on-Chip) entwickelt. Auf beiden Varianten wurde der Betrieb eines Linux-Systems erfolgreich getestet. Dazu wurden die Prozessoren in einem FPGA implementiert.[2][3]

Aufbau

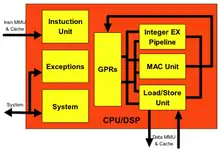

Das Design des OpenRISC 1000 entspricht einer schlanken Umsetzung von modernen RISC-Architekturen mit 16 oder 32 Registern und einer fixen Instruktionslänge von 32 Bit. Die 32- und 64-Bit-Version verwenden den gleichen Befehlssatz. Das Design enthält alle Funktionen, die von heutigen Desktop- oder Server-Prozessoren erwartet werden. Dazu gehören beispielsweise: Virtuelle Speicherverwaltung, eine Secure Virtual Machine, MAC, eine SIMD-Implementierung oder der Mehrprozessorsystem-Betrieb. Die Cachegröße ist skalierbar zwischen 1 und 64 KiB.

Anwendungen

Die meisten Anwendungen wurden bisher auf einem FPGA realisiert. Anfang 2011 erließ OpenCores einen Spendenaufruf um zum ersten Mal einen OpenRISC 1200 in ASIC-Technik zu produzieren.[4] Obwohl das OpenRISC-1000-Design als stabil gilt, wird momentan noch die Rechenleistung und der Energieverbrauch verbessert, weshalb bis heute (September 2012) kein ASIC-Chip produziert wurde.[5]

Außer den Bemühungen von OpenCores, einen vollständig freien Chip herzustellen, gibt es kommerzielle Implementierungen. Einige Firmen verwendeten das OpenRISC-1200- oder ORPSoC-Design als Grundlage für ihre eigenen Entwicklungen. Folgende Prozessoren wurden auf der Grundlage von OpenRISC 1000 entwickelt:

- BA12, BA14, BA22 von Beyond Semiconductor basieren direkt auf dem OpenRISC 1200.

- Der OpenRISC 1200 ist eine Funktionseinheit auf komplexeren ASIC von Flextronics International und Jennic Limited.

- Samsung verwendet ORPSoC in den Chip-Serien: SDP83 B, SDP92 C, SDP1001/SDP1002 D, und SDP1103/SDP1106 E.[6] Dies Chips dienen als CPU in DTV-Geräten.

- Cadence Design Systems benutzt OpenRISC als Referenzimplementierung in ihren Dokumentationen.[7]

- Am 21. Juli 2012 startete die NASA einen TechEdSat genannten Satelliten mit einem auf OpenRISC 1200 basierenden Bordcomputer.[8]

Akademische Verwertung

Da bei OpenRISC aufgrund des Opensource-Ansatzes alle Details bekannt sind, eignet sich die Architektur gut für Ausbildung, Forschung und Hobbyentwickler. Folgende nichtkommerzielle Anwendungen sind deshalb bekannt:

- Ein Team am Institute for Integrated Systems an der Technischen Universität München erforscht auf den Grundlagen von OpenRISC die Architektur und Programmierung von Mehrprozessorsystemen.[9]

- Die britische Open Source Hardware User Group führt Veranstaltungen durch, bei denen die FPGA-Programmierung anhand von OpenRISC erlernt oder vertieft wird.[10][11]

Betriebssysteme und Toolchain

Neben Linux sind RTEMS, FreeRTOS und eCos auf der OpenRISC-1000-Architektur lauffähig. Der or32 genannte Port wurde mit Version 3.1 des Linux-Kernels in den Hauptentwicklungszweig aufgenommen und gilt somit als stabil.[12] Eine µClinux-Portierung ist ebenfalls verfügbar, wird aber momentan nicht weiterentwickelt. Neben der GNU Toolchain wurde auch newlib, uClibc und Busybox für OpenRISC 1000 portiert.[13] Eine Portierung von LLVM befindet sich in der Entwicklung.[14]

Emulatoren

Das OpenRISC-Projekt stellt einen Befehlssatz-Simulator zur Verfügung, welcher auf SystemC basiert und direkt auf die, in der Hardwarebeschreibungssprache Verilog vorliegenden, Prozessorquellen zurückgreift. Die folgenden virtuelle Maschinen können ein OpenRISC-1000-System emulieren:

- QEMU[15]

- OVPsim

- jor1k (Implementierung in JavaScript)[16]

Weblinks

Einzelnachweise

- OpenRISC 1000 Architecture Manual (englisch), Damjan Lampret et al., Rev. 1.3, 15. November 2007

- Basic Custom OpenRISC System Hardware Tutorial: Embedded system design based upon Soft- and Hardcore FPGA’s (Memento vom 27. November 2006 im Internet Archive) (PDF; 350 kB), (englisch), Patrick Pelgrims, Tom Tierens and Dries Driessens, De Nayer Instituut, Hogeschool voor Wetenschap & Kunst, 2004

- Open source embedded platform based on OpenRISC and DE2-70 (englisch), Xiang Li and Lin Zuo, KTH

- OpenCores donation FAQ(englisch), OpenCores

- OpenCores - Call for OpenRISC ASIC donations (Memento vom 1. Mai 2011 im Internet Archive) (englisch), OpenCores

- Samsung Open Source Release Center (nach OpenRISC suchen)

- UVM Reference Flow (englisch), Accellera.

- NEWSLETTER SEPTEMBER 2010 (Memento vom 28. Februar 2017 im Internet Archive) (englisch) OpenCores, zugegriffen: 1. April 2021

- Multicore Architecture and Programming Model Co-Optimization (MAPCO) (PDF; 4,0 MB), Stefan Wallentowitz, Thomas Wild and Andreas Herkersdorf, Technische Universität München, zugegriffen: 7. September 2012

- Chips (Programmable Logic, Computer Conservation with FPGAs, OpenCores & OpenRISC 1000), OSHUG, zugegriffen: 7. September 2012

- Practical System-on-Chip (Program your own open source FPGA SoC), OSHUG, zugegriffen: 7. September 2012

- Linux (englisch), OpenCores, zugegriffen: 7. September 2012

- OpenRISC1200 platform (Memento vom 17. September 2012 im Internet Archive), OpenCores, zugegriffen: 1. April 2021

- project wiki page (Memento vom 14. Oktober 2013 im Internet Archive), OpenCores

- Qemu 1.2.0 verbessert Live Migration, Heise Zeitschriften Verlag, zugegriffen: 7. September 2012

- jor1k-Projektseite