Programmable Array Logic

Programmable Array Logic (kurz PAL genannt) sind elektronische Halbleiterbausteine im Bereich der Digitaltechnik, die durch Programmierung eine logische Verknüpfungsstruktur der Eingangssignale zu den Ausgangssignalen erhalten. Eine alternative deutsche Bezeichnung lautete auch "programmierbare Zellenlogik"[1]. Sie wurden 1978 durch die Firma Monolithic Memories Inc. (MMI) entwickelt und in den Folgejahren produziert.[2] PAL wurden in einer der ersten Hardwarebeschreibungssprachen PALASM programmiert. AMD brachte 1983 den PAL AMPAL22V10 (22V10) auf den Markt. Die deutsche Philips-Tochterfirma Valvo fertigte laut Datenbuch 1984 programmierbare integrierte Logik-Schaltkreise[3]. 1986 hatten die universelleren PLAs die entwicklungstechnisch älteren PALs bereits weitgehend vom Halbleitermarkt verdrängt[4].

Allgemeines

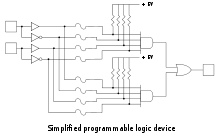

PALs sind Sonderfälle von PLAs (Programmable Logic Arrays) und dadurch gekennzeichnet, dass ausschließlich ihr UND-Array programmierbar ist. PALs sind nur einmal beschreibbar, da die Verknüpfungen auf dem Chip im Rahmen des Programmierprozesses mittels Durchbrennen von Verbindungen (Fuse-Technologie) oder Durchbrennen von Isolierungen (Antifuse-Technologie) hergestellt werden. Für die Programmierung werden die dazu notwendigen Daten in der Regel in Dateien im JEDEC-Format gespeichert.

Eine Weiterentwicklung der PALs und PLAs sind GALs (Generic Array Logic) und die entwicklungstechnisch noch jüngeren, aber komplizierter aufgebauten CPLDs (Complex Programmable Logic Device).

Seit Mitte der 1990er Jahre werden PALs und GALs in neu entwickelten Schaltungen kaum noch eingesetzt und sind fast vollständig durch Complex Programmable Logic Devices (CPLDs) abgelöst worden. CPLDs besitzen keine Einschränkungen bezüglich der Verwendbarkeit der UND-/ODER-Matrizen im Eingangsbereich, sind elektronisch programmier- und löschbar und umfassen darüber hinaus eine bestimmte Anzahl an Registern. Die Funktion wird wie auch bei Field Programmable Gate Arrays (FPGAs) mittels abstrakter Hardware-Programmiersprachen, wie beispielsweise VHDL, spezifiziert.

Hersteller

- ehem. Monolithic Memories Inc., USA

- ehem. Valvo GmbH, Deutschland

- ehem. Philips GmbH, Niederlande

- ehem. Texas Instruments, USA

- ehem. AMD, USA

- ehem. National Semiconductor, USA

- ehem. Lattice

- ehem. Cypress Semiconductor Corporation

Weiterentwicklungen

Generic Array Logic (GAL)

Als Weiterentwicklung der PALs kamen zuerst durch die Lattice Semiconductor Corporation die wiederbeschreibbaren Generic Array Logic (kurz GAL genannt) -Bausteine auf den Markt. Sie bestehen aus einer programmierbaren UND-Matrix und einer fest verdrahteten ODER-Matrix. Im Gegensatz zum PAL sind sie elektrisch beschreibbar und entweder durch UV-Licht (EPLD) oder elektrisch (EEPLD) löschbar, wodurch eine Neuprogrammierung möglich wird.

Die Bezeichnung GAL ist ein Warenzeichen der Firma Lattice, wodurch es einige Firmen gibt, die diese Bausteine mit ihrem Originalnamen unter Lizenz bezeichnen, und andere Firmen, welche diese Bausteine umbenannt haben (bei AMD beispielsweise unter dem Namen PALCE) – hierbei unterscheidet sich der Programmieralgorithmus, jedoch nicht die Pinbelegung und Funktion.

Die Bezeichnung gibt im Muster an, um was für einen Logikbaustein es sich handelt, und gibt Informationen über seine Eigenschaften an. Ein GAL16v8 ist ein GAL-Baustein mit 16 Matrixeingängen für die Logikmatrix, dem Ausgangstyp v (variable Architektur) und verfügt über acht Ausgänge. Anschließend kommt nach einem Minus die Gatterdurchlaufverzögerung in ns und weitere Informationen über Betriebstemperaturen und das Chipgehäuse.

GAL-Bausteine haben drei verschiedene Betriebsmodi, welche durch zwei Architekturbits beim Programmieren festgelegt werden. Ein drittes Bit setzt für Ausgänge die Funktion, ob sie als Eingang oder Ausgang fungieren sollen (AC1(n), n=Pinnummer). Das bedeutet, dass generell jeder Ausgang auch als Eingang verwendet werden kann. Der Simple-Mode (SYN=1, AC0=0) ermöglicht die Verwendung des GAL-Bausteins als einfaches Logikgatter, mit Verknüpfung der AND-Bausteine mit nachfolgenden OR-Bausteinen. Der Complex-Mode (SYN=1, AC0=1) lässt das Multiplexen mithilfe von Tri-State-ausgängen zu und der letzte der Modi, der Registermodus, ermöglicht die Verschaltung von Logikgattern mit Registern durch integrierte D-Flipflops. Dadurch kann man sogar kleinere komplexere Schaltungen aufbauen, ohne ständig die Schaltungen durch weitere externe Logikbausteine erweitern zu müssen.

Ende 1988 brachte SGS-Thomson laut genanntem Datenbuch GALs auf den Markt[5].

Hersteller von GALs:

Sonstige

Seit Mitte der 1990er Jahre werden PALs/PLAs und GALs in neu entwickelten Schaltungen kaum noch eingesetzt und sind fast vollständig durch die komplexer aufgebauten Complex Programmable Logic Devices (CPLDs) abgelöst worden. CPLDs besitzen keine Einschränkungen bezüglich der Verwendbarkeit der UND-/ODER-Matrizen im Eingangsbereich, sind elektronisch programmier- und löschbar, sind wie Field Programmable Gate Arrays (FPGAs) in einheitlichen Hardware-Programmiersprachen, wie beispielsweise VHDL, programmierbar und umfassen darüber hinaus eine bestimmte Anzahl an Registern. siehe: Complex Programmable Logic Device

CPLD gehört laut Böhmer noch zur Gruppe der PAL/PLA/PLD(Programmable Logic Device) und GAL, hat aber einen komplizierteren Innenaufbau im IC. Die noch neueren FPGAs gehören hingegen zu einer anderen Technologie[7].

PIN-Kompatibilität und Benennung von PALs und GALs

Die Bezeichnung 16L8 des PAL bedeutet, dass dieser 16 Eingänge hat und 8 Ausgänge mit negativer Ausgangslogik (L="Low" als Ausgangslogik). Ein H anstelle des L steht für positive Ausgangslogik. Ein R steht für die Nutzung als Register (Speicher für Dualzahlen)[8].

Die älteren GALs von Lattice sind mit den deutlich älteren PALs pinkompatibel. So kann anstelle des PAL "16L8" der GAL "16V8" von Lattice eingesetzt werden. Auch dieser hat 16 Eingänge und 8 Ausgänge.

IC-Typen

PALs:

- PAL16R4... (kurz: 16R4) von Texas Instruments

- PAL16R6CN (kurz: 16R6) von MMI, 20PIN DIP, seit 1978

- PAL16R8BCN (kurz: 16R8) von MMI, 20PIN DIP

- PAL16L8... (kurz: 16L8) von MMI, 20PIN DIP

- AMPAL22V10APC (kurz: 22V10) von AMD, 24PIN DIP, seit 1983

- TI16L8-25 (kurz: 16L8), philippinischer Produzent

- 16X4, Hersteller?

GALs:

- PALCE16V8H-25JC (kurz: 16V8H) von AMD, 20PIN DIP

- PALCE16V8Z-12PI (kurz: 16V8Z) von AMD, 20PIN DIP

- PALCE16V8H-25 (kurz: 16V8H) von AMD, 20PIN DIP

- PALCE 16V8H-25JC/4 (kurz: 16V8H) von AMD, 20PIN (4x5PINs)

Literatur

PAL

- PAL/PLE Device. Programmable Logik Array Handbook. 5. Auflage. Monolithic Memories, 1986 (archive.org).

- Ton Zengerink: PAL-Praxis: der Umgang mit den modernen programmierbaren Logikbausteinen. Franzis, München 1987, ISBN 3-7723-8551-6.

- Advanced Micro Devices (Hrsg.): PAL Device Handbook. 1988 (archive.org [abgerufen am 3. Januar 2020]).

- Advanced Micro Devices (Hrsg.): PAL Device Data Book. 1988.

GAL

- Programmable Logic Manual – GAL Products. SGS-Thomson, 1988.

- Dieter Bitterle: GALs, Programmierbare Logikbausteine in Theorie und Praxis. 2. Auflage, Franzis-Verlag, München 1992, ISBN 3-7723-5903-5.

- Dieter Bitterle: Schaltungstechnik mit GALs, Über 50 Schaltungen für die praktische Anwendung. Franzis-Verlag, München 1992, ISBN 3-7723-4681-2.

- Erwin Böhmer, Dietmar Ehrhardt, Wolfgang Oberschelp: Elemente der angewandten Elektronik. 15. Auflage, Vieweg Verlag, Wiesbaden 2007, ISBN 978-3-8348-9021-4, Kapitel ROMs, PROMs und PLDs, S. 268–269, Aufbau und Programmierung von GALs im Anhang S. 418–419.

Weitere

- Integrierte programmierbare Logikschaltungen. Datenbuch. Valvo GmbH, 1984.

- Programmable Logic Devices Databook & Design Guide. National Semiconductor, 1990 (archive.org [abgerufen am 3. Januar 2020]).

- A. Auer: Programmierbare Logik-IC, Eigenschaften, Anwendung, Programmierung. Hüthig Buch, Heidelberg 1990, ISBN 3778519107 (Aufbau und Programmierung von Programmable Logic Device (PLD), Generic Array Logic (GAL), Abänderbarer Gatteranordnung (AGA) und Logic Cell Array (LCA)).

- Geoff Bostock: Programmable logic handbook. 2. Auflage. Butterworth Heinemann, Oxford / Boston 1993, ISBN 0-7506-0808-0.

Weblinks

- Computer History Museum timeline/1978-PAL auf computerhistory.org (englisch)

- Datenblatt von PAL ICs auf ti.com(März 1992, englisch)

Einzelnachweise

- Manfred Seifart: "Prinzipielle Struktur einer PLA", In: "Digitale Schaltungen", VEB Verlag Technik Berlin, DDR, Berlin 1986, zweite Auflage, ISBN 3-341-00148-4., PROM PLA und PAL auf S. 273

- Monolithic Memories announces: a revolution in logic design. In: Hayden Publishing (Hrsg.): Electronic Design. 26, Nr. 6, Rochelle, NJ, 18. März 1978, S. 148B bis 148C. Introductory advertisement on PAL (Programmable Array Logic).

- "Integrierte programmierbare Logikschaltungen. Datenbuch." Valvo GmbH, 1984

- Manfred Seifart: "Prinzipielle Struktur einer PLA", In: "Digitale Schaltungen", VEB Verlag Technik Berlin, DDR, Berlin 1986, zweite Auflage, ISBN 3-341-00148-4, S. 273

- "Programmable Logic Manual - GAL Products", First Edition, October 1988, SGS-Thomson

- Erwin Böhmer/Dietmar Ehrhardt/Wolfgang Oberschelp: Elemente der angewandten Elektronik, Vieweg Verlag Wiesbaden, 2007, 15. Auflage, Anmerkungen zu PAL/PLD/GAL/CPLD S. 418

- Erwin Böhmer: Elemente der angewandten Elektronik, Vieweg Verlag Wiesbaden, 1996, 10. Auflage, Kapitel "ROM, PLD und PAL" S. 269