Programmierbare logische Schaltung

Eine programmierbare logische Schaltung, häufig auch in deutschsprachiger Fachliteratur als Programmable Logic Device oder kurz PLD bezeichnet, ist ein elektronisches Bauelement für integrierte Schaltkreise. Anders als logische Gatter, die eine feste Funktion vorgegeben haben, erhalten PLDs erst nach der Herstellung ihre Funktion durch die entsprechende Programmierung (Konfiguration). PLD ist der Oberbegriff für Logik-IC-Technologien wie PAL, PLA, GAL, CPLD[1] und für neuere Technologien wie FPGAs.

Unterscheidung nach Komplexität

Beispiele unterschiedlich komplexer PLDs sind (in aufsteigender Komplexität):

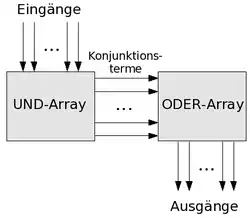

Einfache programmierbare logische Schaltungen bestehen meist aus einem Array aus UND-Verknüpfungen gefolgt von einem Array aus ODER-Verknüpfungen.

- Programmable Read-Only Memory (PROM)

Ein PROM stellt ein festes UND-Array mit einem programmierbaren ODER-Array bzw. eine Lookup-Tabelle (LUT) dar. - Programmable Array Logic (PAL) bzw. Generic Array Logic (GAL)

Ein PAL stellt ein programmierbares UND-Array mit einem festen ODER-Array dar. Ein GAL ist im Gegensatz zu einem PAL wiederbeschreibbar. - Programmierbare logische Anordnung (PLA)

Bei einem PLA sind sowohl das UND-Array als auch das ODER-Array programmierbar.

PLAs wurden meistens eingesetzt, um sogenannte Glue Logic zu ersetzen. Inzwischen werden sie kaum noch eingesetzt und sind durch folgende PLDs ersetzt worden.

- Complex Programmable Logic Device (CPLD)

Ein CPLD besteht aus Blöcken, die ein PLA, Ein- und Ausgangsblöcke sowie eine programmierbare Rückkopplung enthalten. Diese Blöcke können untereinander verbunden werden. In der Regel ist für jeden I/O-Pin auch ein Flipflop enthalten. - Field Programmable Gate Array (FPGA)

Ein FPGA besteht ähnlich wie ein CPLD aus untereinander vernetzten Blöcken, jedoch sind diese komplexer. Ein Block besteht hier aus Flip-Flops und LUTs. Auch die Möglichkeiten, diese Blöcke untereinander zu verbinden, sind gegenüber dem CPLD stark erweitert. Ein FPGA enthält oft auch fertige Funktionsblöcke wie RAM, PLLs oder ganze CPU-Kerne.

CPLDs wie FPGAs bieten außerdem oft programmierbare I/O-Zellen, die es erlauben, verschiedene Signalschnittstellen (z. B. TTL, PCI oder LVDS) an den Baustein anzuschließen. Siehe auch: Unterschiede von CPLDs zu FPGAs

Unterscheidung nach Programmierbarkeit

- Maskenprogrammiert

Hier wird die Konfiguration schon bei der Produktion des Bauteils festgelegt (siehe Gate-Array). Sollen FPGAs in großen Stückzahlen eingesetzt werden, können diese bei einigen Herstellern maskenprogrammiert geordert werden. Dies spart zusätzliche Produktionsschritte und die zur Konfiguration notwendigen externen Bauteile. - One Time Programmable (OTP)

Hier gibt es die Programmierung durch Durchbrennen von Verbindungen (Fusible-link) oder das Schaffen von Verbindungen bei der Antifuse-Technologie. - Erasable Programmable Read Only Memory (EPROM)

Die EPROM-Programmierung wurde meist nur bei PLAs eingesetzt. - Electrically Erasable Programmable Read-Only Memory (EEPROM) oder Flash

GALs sind EEPROM programmiert und können deshalb im Gegensatz zu PALs wiederverwendet werden. Die Konfiguration von CPLDs findet in der Regel über Flash-Speicher statt. Die Programmierung über EEPROM bzw. Flash hat den Vorteil, dass das Bauteil sofort nach dem Einschalten fertig konfiguriert zu Verfügung steht. - SRAM basiert

Die Konfiguration von FPGAs ist in der Regel SRAM-basiert. Diese muss nach dem Einschalten des FPGAs erst in den Baustein geladen werden, entweder durch ein Konfigurations-PROM oder einen angeschlossenen Mikroprozessor. Ein FPGA kann sogar während des Betriebes ganz oder teilweise neu programmiert werden, z. B. um einen laufenden Verarbeitungsalgorithmus zu ändern. Ein Anwendungsgebiet dafür ist das Reconfigurable Computing.

Siehe auch

Literatur

- A. Auer: PLD-Handbuch, Tabellen und Daten, Mikroelektronik 6. Hüthig-Verlag, Heidelberg 1990, ISBN 978-3-7785-1991-2.

- Erwin Böhmer, Dietmar Ehrhardt, Wolfgang Oberschelp: Elemente der angewandten Elektronik. 15. Aufl. Vieweg Verlag, Wiesbaden 2007, Kapitel ROMs, PROMs und PLDs. (ROM, PLD und PAL auf S. 268–269, Aufbau und Programmierung von GALs im Anhang S. 418–419, Gliederung der verschiedenen PLD-Technologien S. 418).

Weblinks

Einzelnachweise

- Erwin Böhmer, Dietmar Ehrhardt, Wolfgang Oberschelp: Elemente der angewandten Elektronik. 15. Aufl. Vieweg Verlag, Wiesbaden 2007, Gliederung der PLDs S. 418 (Kapitel „ROM, PLD und PAL“ auf S. 268–269, Aufbau und Programmierung von GALs im Anhang S. 418–419).