Oder-Gatter

Ein Oder-Gatter ist ein Gatter mit mehreren Eingängen und einem Ausgang, bei dem der Ausgang eine 1 liefert, wenn an mindestens einem Eingang eine 1 anliegt. Es entspricht dem Logischen ODER. In der Schaltalgebra wird die Oder-Verknüpfung durch + oder (Ursprung ist das lat. Wort „vel“ (oder)) dargestellt und wird auch als Disjunktion bezeichnet.

| Gatter-Typen | |

|---|---|

| NOT | |

| AND | NAND |

| OR | NOR |

| XOR | XNOR |

Übersicht

| Funktion | Schaltsymbol | Wahrheitstabelle | Relais-Logik | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| IEC 60617-12 | US ANSI 91-1984 | DIN 40700 (vor 1976) | ||||||||||||||||||

|

|

|

| |||||||||||||||||

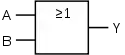

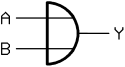

Das Größer-Gleich-Zeichen ≥ verdeutlicht beim gegenwärtig in Deutschland gültigen Schaltsymbol, dass bei einer oder mehr Einsen an den Eingängen (High, logisch 1) der Ausgang 1 ist.

Oder-Gatter mit größerer Anzahl von Eingängen

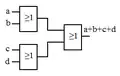

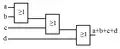

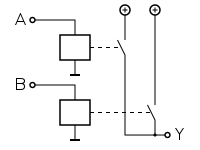

Das minimale Oder-Gatter hat zwei Eingänge (OR2), es stehen aber auch Gatter mit mehr Eingängen zur Verfügung. Sollte man auf Gatter mit einer bestimmten Anzahl Eingänge beschränkt sein, kann man mit diesen auch Gatter mit einer höheren oder niedrigeren Anzahl von Eingängen realisieren. Zur Erhöhung verknüpft man mehrere Gatter, wie in Abb. 1 und 2 zu sehen ist. Dabei sollte man zur Reduzierung der Gatterlaufzeit und der benötigten Anzahl Gatter auf einen möglichst optimalen Aufbau achten.

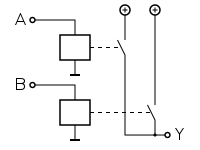

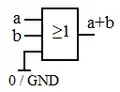

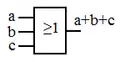

Wenn man hingegen Gatter mit geringerer Anzahl von Eingängen braucht, muss man die nicht benötigten Eingänge auf logisch 0 (oft Masse, Nullpotenzial) legen, siehe Abb. 3. In Abb. 4 wird das Schaltsymbol für ein Oder-Gatter mit drei Eingängen gezeigt. Oder-Gatter mit mehr Eingängen werden entsprechend gezeichnet.

Abb. 1: OR4-Gatter zusammengesetzt aus OR2-Gattern auf ökonomische Weise

Abb. 1: OR4-Gatter zusammengesetzt aus OR2-Gattern auf ökonomische Weise Abb. 2: OR4-Gatter aus OR2-Gattern auf ungünstige Art

Abb. 2: OR4-Gatter aus OR2-Gattern auf ungünstige Art Abb. 3: OR3-Gatter reduziert zu einem OR2-Gatter

Abb. 3: OR3-Gatter reduziert zu einem OR2-Gatter Abb. 4: OR3-Gatter

Abb. 4: OR3-Gatter

Schaltungstechnische Realisierung

Oder-Gatter werden als integrierte Schaltung (IC) von vielen Herstellern produziert. Standardbausteine dieser Art sind z. B. unter der Bezeichnung „7432“ in TTL-Technik und als „4071“ in CMOS-Technologie erhältlich und enthalten vier Oder-Gatter mit jeweils zwei Eingängen. Die genaue Bauteilbezeichnung ist abhängig vom Hersteller. Logik-Gatter dieser Art sind für wenige Cent im Elektronik-Fachhandel erhältlich.

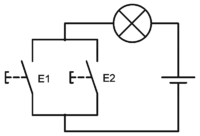

Elektrische Realisierung eines ODER-Gatters mit Schaltern

Elektrische Realisierung eines ODER-Gatters mit Schaltern Realisierung eines ODER-Gatters mit Relais

Realisierung eines ODER-Gatters mit Relais

Bei parallel zusammengeschalteten Offenen Kollektoren spricht man vom „Verdrahteten Oder“ (Wired-OR), da sich hier eine Oder-Funktion bildet. Zwar ist das Signal an den Kollektoren negativ (NOR-Gatter), bezogen auf den Pull-Up-Widerstand oder das zusteuernde Bauteil, positiv.

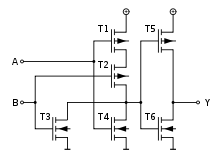

CMOS

Nebenstehende Abbildung zeigt das Schaltbild eines Oder-Gatters in CMOS-Technologie. Die Transistoren T1 bis T4 bilden zusammen ein NOR-Gatter. Liegt z. B. an Eingang A oder B High-Potential an, dann leitet T3 bzw. T4, wobei T1 bzw. T2 sperrt. Am Ausgang des NOR-Gatters realisieren die Transistoren T5 und T6 die Funktionalität eines NOT-Gatters. Ein negiertes NOR-Gatter ergibt das gewünschte OR-Gatter. Mit der erwähnten Eingangsbelegung an A und B liegt an T5 und T6 Low-Potential an und T5 leitet, aber T6 sperrt. Dadurch ergibt sich am Ausgang Y High-Potential.

Literatur

- Ulrich Tietze, Christoph Schenk: Halbleiter-Schaltungstechnik. 12. Auflage. Springer, 2002, ISBN 3-540-42849-6.