Nanoelektronik

Als Nanoelektronik werden integrierte Schaltkreise bezeichnet, deren Strukturbreiten (kleinste, über Strukturierungsverfahren wie Lithographie realisierbare Abmessung bei integrierten Schaltkreisen) unter 100 nm liegen.[1] In diesem Bereich müssen physikalische Effekte beachtet werden, die zuvor unbekannt oder vernachlässigbar waren. Dies führt zu neuen Formen der Bauelemente und ganz neuen Funktionsprinzipien. Allerdings ist dies nur eine grobe Einordnung und der Begriff der Nanoelektronik unterliegt keiner strengen Definition oder Norm, da der Übergang zwischen Mikroelektronik und Nanoelektronik fließend verläuft oder es wird nicht unterschieden, d. h., alles unter dem Begriff Mikroelektronik behandelt.

Hintergrund

Die Nanoelektronik ist eng verwandt mit der Mikroelektronik, die sich mit der Miniaturisierung von elektronischen Bauelementen und dessen Integration zu komplexeren Baugruppen beschäftigt. Dies stellte eine deutliche Verkleinerung gegenüber der zuvor genutzten Röhrenelektronik, weswegen man die „neue“ Elektronik als Mikroelektronik bezeichnet (von. μικρός mikros, dt. ‚klein‘) bezeichnet. Zugleich lagen in der Anfangsphase die Maße dieser Bauelemente sowie deren kleinster Bestandteile (z. B. Gate-Länge oder Gate-Oxide-Dicke) im Mikrometer-Bereich und wurden Ende des 20. Jahrhunderts und Anfang des 21. Jahrhunderts immer kleiner, vgl. Skalierung (Mikroelektronik) oder auch mooresches Gesetz. Die grundlegende Funktionsweise und Aufbau der elektronischen Bauelemente (vor allem der Transistoren) blieben dabei weitgehend unverändert. Gestiegene Anforderungen an die Fertigung wurden weitgehend mit denselben bzw. modifizierte Herstellungsprinzipien erfüllt.

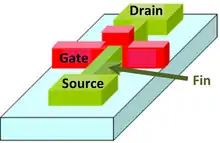

In dieser Hinsicht wird die Nanoelektronik einfach als Mikroelektronik im Nanometerbereich interpretiert, das heißt mit Strukturgrößen kleiner als 100 nm.[1] Diese einfache, sehr grobe Definition enthält keinen direkten Bezug auf neue notwendige Lösungsstrategien, die aufgrund des steigenden Einflusses quantenmechanischer Phänomene nicht mehr bei der Funktionsweise und Aufbau der elektronischen Bauelemente als auch bei der Fertigung vernachlässigbar sind. Mit diesen neuen Ansätzen ist die Nanoelektronik somit auch verbunden mit der Nutzung auch neuer Materialien (z. B. High-k-Dielektrika), Fertigungsprinzipien (z. B. Immersionslithografie, EUV-Lithografie) und Bauelementkonzepte (z. B. FinFET und dessen Weiterentwicklungen sowie Kohlenstoff-Nanoröhren-Feldeffekttransistor) für die Fortführung der Skalierung „konventionellen“ Konzepte im Rahmen des mooreschen Gesetzes als auch neuer Konzepte der Nanoelektronik, die unter anderem mit den Begriffen „More Moore“, „More than Moore“ oder „Beyond CMOS/Moore“ bezeichnet werden. Die Einschränkung Nanoelektronik nutzt quantenmechanische Funktionsprinzipien oder Ähnliches wird ebenfalls als nicht sinnvoll erachtet, auch da dies „Bauelemente einschließen würde, die seit Jahrzehnten in Verwendung sind (beispielsweise Laserdioden, SQUIDs etc.) und üblicherweise nicht zur Nanoelektronik gezählt werden.“[1]

Eingesetzte Materialien

Basismaterial für die Mikroelektronik bildet seit mehreren Jahrzehnten der Halbleiter Silizium. Verantwortlich dafür ist unter anderem die Beherrschung des Einkristall-Herstellungsprozesses und vor allem die Kombination mit seinem Oxid (Siliziumdioxid), das als Isolatormaterial eingesetzt wird und sehr gute Haftungseigenschaften auf Silizium besitzt. Die bisherige Entwicklung der Herstellungsprozesse für Siliziumeinkristalle ermöglicht mittlerweile die großvolumige Herstellung qualitativ hochwertiger Kristalle für Substrate (Wafer) mit Durchmessern von 300 mm.

Herausforderungen und Lösungen

Da sich aber mit sinkenden Strukturbreiten Leckströme und Quanteneffekte immer stärker bemerkbar machen, wurde es notwendig, neue Konzepte, wie den Y-Transistor oder den FinFET-Transistor zu entwickeln, und neue Materialien in den Herstellungsprozess zu integrieren. Nur so wurde es möglich, weiterhin die Leistung elektronischer Komponenten zu steigern und gleichzeitig die Kosten zu reduzieren. Das Ende dieser Entwicklung wurde in den letzten Jahrzehnten bereits mehrmals prognostiziert, die bestehenden Probleme, insbesondere die für unüberwindbar gehaltenen physikalischen Grenzen im Herstellungsprozess, konnten aber immer wieder überwunden werden. Trotzdem werden die „konventionellen“ Konzepte irgendwann ausgeschöpft sein, und es wird notwendig sein, völlig neue Konzepte zu entwickeln.

Ein Beispiel ist die Extrem-Ultraviolett-Lithografie (EUVL). 2012 erfolgte die Strukturierung der kritischen Ebenen noch ausschließlich mit „konventioneller“ Fotolithografie, die UV-Licht mit einer Wellenlänge von 193 nm (Argonfluorid-Excimerlaser) verwendete. Mithilfe von aufwendigen und damit teuren Konzepten wie der Mehrfachstrukturierung konnte die Nutzung der ArF-Immersionslithografie bis hin zum 10- bzw. 7-nm-Technologieknoten verlängert werden. Dennoch wurde die Entwicklung der EUVL vorangetrieben und kam 2019 bei ähnlichen Strukturgrößen zum Einsatz, da sie nun ausreichend ausgereift für den produktiven Einsatz war und nun endlich auch im kommerziellen Umfeld Vorteile ggü. den „konventioneller“ Methoden hatte.

Zielsetzung und Einsatzfelder

Zielsetzung der Nanoelektronik ist es, elektronische Bauteile im Nanometerbereich zu verkleinern, um letztlich Rechenkapazitäten, Speicherkapazitäten, die Geschwindigkeit und die Effizienz von Computerchips zu steigern. Dazu sollen v. a. die elektronischen Eigenschaften von Nanohalbleiterstrukturen erforscht und verbessert werden. Daneben gilt es, den Schaltungsaufbau und die Architektur von Computerchips anwendungsbezogen zu optimieren. Die Gesetze der Quantenphysik sollen für die Elektronik nutzbar gemacht werden.

Weiterhin soll die Nanoelektronik bessere Techniken und Geräte für die Elektronikfertigung liefern und durch neuartige Schaltungen und Bauelemente die logische Verknüpfung, Speicherung und Verarbeitung von Daten optimieren. Es wird erwartet, dass analog zur Entwicklung der Mikroelektronik der technische Fortschritt in nahezu allen Branchen positiv beeinflusst wird und dass im Ergebnis eine noch höhere Funktionalität von Geräten bei geringeren Kosten vorliegen wird.

Kommerzielle Einsatzfelder für die Nanoelektronik sind die Unterhaltungselektronik, die Automatisierungstechnik, die Medizintechnik, mobile Kommunikationsgeräte, Computer, Navigation, Sensorik, Autos und alle Bereiche technikorientierter Forschung, in denen Messgeräte höchster Präzision zum Einsatz kommen.

Physikalische Grenze & Voraussage

Der kleinste Abstand von Siliziumatomen im Einkristall beträgt 0,235 nm (= 235 pm)[2], was nur wenig größer als der doppelte kovalente Radius von 0,222 nm ist. Daraus ergibt sich, dass bei einer Strukturbreite von 5 nm nur noch etwa 20–25 Siliziumatome (in [[110]] der Diamantstruktur) miteinander verbunden sind. Intel plant derzeit (Ende 2019) mit dem Start der Massenfertigung 1,4 nm Strukturbreiten voraussichtlich im Jahre 2029 stattfindet.[3] Im nächsten Skalierungsschritt, dem 1,0-nm-Technologieknoten, sind nur noch etwa 4–5 Siliziumatome miteinander verbunden. Bei diesen Verhältnissen wird klar, dass eine „Pikoelektronik“ (< 100 pm, theoretisch) nie realisiert werden kann, da auch alle anderen Atome des Periodensystems einen doppelten kovalenten Radius im Bereich 130–500 pm aufweisen. Somit können die Strukturbreiten für integrierte Schaltkreise nicht beliebig verkleinert werden.[4] Um die Leistung der Mikrochips bei vergleichbarer TDP weiter zu steigern, müssen neue Konzepte erfunden werden, welche nicht mehr von der materiellen Strukturgröße abhängen.

Historische und aktuelle Entwicklung (Kurzfassend)

Die International Technology Roadmap for Semiconductors (ITRS) schlägt die Standards für Technologieknoten vor, so z. B. auch 2017 die Knoten 2 nm, 1,5 nm und 1 nm. Die kleinsten Strukturbreiten integrierter Schaltkreise, insbesondere von Mikroprozessoren in Serienproduktion, lagen:

Speicherchips

Speicherchips haben einfachere Schaltpläne-Architekturen, so kommt es dass diese in Größe der Technologieknoten den Prozessoren chronologisch meistens leicht voraus sind:

- 2002 bei 90 nm, DRAM von Toshiba (Weltweit erste Massenproduktion integrierter Schaltkreise unter 100 nm)[5]

- 2010 bei 24 nm, NAND-Flash von Toshiba

- 2013 bei 10 nm, NAND-Flash von Samsung

- 2017 bei 7 nm, SRAM von TSMC

Prozessoren

- 2003 bei 90 nm, siehe z. B. den Sony/Toshiba EE+GS (PlayStation 2).

- 2008 bei 45 nm, siehe z. B. den Intel Core 2 Quad Q9300.

- 2013 bei 22 nm, siehe z. B. den Intel Core i7-4960X

- 2014 bei 14 nm, siehe z. B. den Intel Core M-5Y10

- 2017 bei 10 nm, siehe z. B. den Qualcomm MSM8998 Snapdragon 835

- 2018 bei 7 nm, siehe z. B. den Apple A12 Bionic

- 2020 bei 5 nm, siehe z. B. den Apple A14 Bionic oder den Qualcomm Snapdragon 875, beide ab Juni 2020 bei TSMC in der Massenproduktion[6]

- 2021 rechnet Samsung mit der Massenfertigung im 3-nm-Verfahren, dagegen TSMC erst mit 2023 rechnet.

- 2029 plant Intel die Massenfertigung in 1,4 nm zu beginnen, was Ende 2019 auf der IEEE International Electron Devices Meeting angekündigt wurde.

Siehe auch

Literatur

- Charles M. Lieber: The incredible Shrinking Circuit. In: Scientific American. 17, Nr. 3, 2001, S. 58–64.

- Technology Forecast: 2000 – From Atoms to Systems: A perspective on technology. PricewaterhouseCoopers Technology Center, 2000, ISBN 1-891865-03-X.

- Jean-Baptiste Waldner: Nanocomputers & Swarm Intelligence. ISTE, London 2007, ISBN 1-84704-002-0.

- Ulla Burchardt, Thomas Feist, René Röspel, Martin Neumann, Petra Sitte, Hans-Josef Fell: Technikfolgenabschätzung: Innovationsreport – Wettbewerbsfähigkeit der europäischen Wirtschaft im Hinblick auf die EU-Beihilfepolitik – am Beispiel der Nanoelektronik (PDF; 1,5 MB). 3. März 2011, Drucksache 17/4982, ISSN 0722-8333 (Herausgeber: Deutscher Bundestag).

Weblinks

- Peter Grünberg Institut

- Schlüsseltechnologien für Kommunikation und Datenverarbeitung: Nanoelektronik und Photonik, Universität Ulm, 2015 auf YouTube

- Nanotechnologie an der FAU – Das Reinraumlabor, MeinStudium, 2016 auf YouTube

- Nanoelektronik: hocheffiziente Bauelemente für große Datenmengen, Helmholtz-Zentrum Dresden-Rossendorf, 2018 auf YouTube

Einzelnachweise

- Basierend auf der Definition von „National Nanotechnology Initiative“ (NNI, USA) und der Europäischen Kommission, vgl. Peter Russer, Paolo Lugli, Marc-Denis Weitze: Nanoelektronik: Kleiner – schneller – besser. Springer-Verlag, 2014, ISBN 978-3-642-35791-6, S. 22 (eingeschränkte Vorschau in der Google-Buchsuche).

- John Kotz, Paul Treichel, John Townsend: Chemistry and Chemical Reactivity. Cengage Learning, 2008, ISBN 978-0-495-38712-1, S. A-95 (eingeschränkte Vorschau in der Google-Buchsuche – Lösung eines entsprechenden Rechenaufgabe.).

- Michael Eckstein: Nach 10-nm-Debakel: Intels Zehnjahres-Roadmap zum 1,4-nm-Prozessknoten. In: elektronikpraxis.vogel.de. 16. Dezember 2019, abgerufen am 17. Juni 2020.

- Jens D. Billerbeck: „Atome lassen sich nicht verkleinern“. In: https://www.ingenieur.de/. 14. April 2006, abgerufen am 17. Juni 2020.

- Toshiba and Sony Make Major Advances in Semiconductor Process Technologies. In: https://www.toshiba.co.jp/. Toshiba Corporation, 3. Dezember 2002, abgerufen am 1. Juli 2020 (englisch).

- Hannes Brecher: TSMC beginnt mit der Produktion von 5 nm-Chips. In: https://www.notebookcheck.com/. 20. Juni 2020, abgerufen am 23. Juni 2020.