Strukturgröße

Die Strukturgröße oder auch Strukturbreite (englisch process size; siehe auch: Minimale Strukturgröße, engl.: minimum feature size) ist eine Größenangabe der Halbleitertechnik, Mikroelektronik und Nanoelektronik und beschreibt die kleinste realisierte (typisch auch gleich der minimal möglichen) Kantenlänge der bestimmenden Plotter-Einheit. Es handelt sich dabei also um das Maskenmaß, das heißt das Zielmaß. Die Abmessungen der damit erzeugten Strukturen sind durch Unterbelichtung und Diffusion in der Regel etwas kleiner als die für die Maske benutzte Plotter-Einheit.

Bei den kleinsten auf einem Halbleiterträger erzeugten Strukturen handelt es sich üblicherweise um die Gate-Länge eines Metall-Isolator-Halbleiter-Feldeffekttransistors (MISFET). Sie wird in diesem Zusammenhang oft mit der Strukturgröße eines Herstellungsprozesses oder einer Technologie gleichgesetzt, dem sogenannten Technologieknoten, wenn man den Begriff auf das gesamte auf diese Strukturgröße ausgerichtete Herstellungsverfahren bezieht. Da jedoch auch innerhalb eines Technologieknotens die kleinsten Strukturbreiten je nach Produkt um mehrere Prozent schwanken können, ist dieser Zusammenhang nicht korrekt.

Der Begriff wird auch im Bereich der digitalen, optischen Speichermedien verwendet, meist für die Abmessungen der Lands und Pits von optischen Speichermedien wie CD, DVD und Blu-ray Disc. Auch bei der Nanotechnologie, die sich eher in einem physikalisch-technischen Kontext mit Strukturen bis hinauf zu 100 nm beschäftigt, wird der Begriff angewandt.

Bedeutung

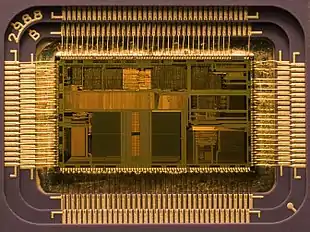

Das geöffnete Chipgehäuse ermöglicht einen Blick auf den eigentlichen Halbleiter-Chip

Wichtige Eigenschaften von integrierten Schaltkreisen korrelieren mit der verwendeten Strukturgröße. Die wichtigsten sind:

- Packungsdichte der Transistoren: steigt quadratisch mit fallender Strukturgröße

- Kompaktheit einer Elementarzelle des ICs: Neben der Verkleinerung der Strukturen sind auch die Elementarzellen an sich kleiner geworden. Eine DRAM-Zelle im Jahr 1990 bestand aus zwei Transistoren und nahm etwa 50 F2 Fläche ein, d. h. 200 µm² bei einer Strukturgröße von 2 µm. Heutzutage besteht sie aus einem Transistor und nimmt 6 F2 Fläche[1] ein, das entspricht ca. 144–128 nm² bei einer Strukturgröße von 22 nm[2].

- Betriebsspannung: fällt mit fallender Strukturgröße

- Maximale Schaltfrequenz: steigt mit fallender Strukturgröße

- Verlustleistung pro Gatter und Schaltvorgang: fällt mit fallender Strukturgröße

- Robustheit betr. ionisierende Strahlung: fällt mit fallender Strukturgröße

- Langzeitkonstanz von Eigenschaften durch Elektromigration: fällt mit fallender Strukturgröße

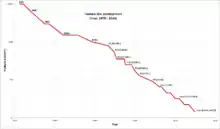

Zusammen mit der Vergrößerung der Wafer-Größe bei der Halbleiterfertigung bildet die Verkleinerung der Strukturgröße die beiden Kernpunkte zur Reduzierung der Produktionskosten, der Erhöhung der Leistungsfähigkeit und der Geschwindigkeit von Halbleiterbausteinen.

Die Strukturgröße ist ein wichtiger Parameter, der zentral vom verwendeten Halbleiterprozess (CMOS, NMOS, TTL etc.) und dem dafür verfügbaren kleinsten bzw. gewählten Transistordesign bestimmt wird. Hierbei sind sowohl die Materialbeschaffenheit des Trägers, meist ein Silizium-Wafer, und der Dotierungen, als auch die eingesetzte Lithographietechnik und damit die erforderlichen Fertigungsparameter wie etwa Luftreinheit und Ähnliches bis hin zur momentanen Verfügbarkeit von Fabrikkapazitäten wichtig. Auch auf den Preis solcher Produktionsleistungen lässt sich daraus in der Regel zurück schließen.

Nicht zuletzt bestimmt die Strukturgröße, wie viele Transistoren auf einen Wafer passen und damit auch, wie viele einzelne Halbleiter typisch daraus gewonnen werden können. Zusammen mit dem logischen Design des Halbleiters ergibt sich also eine Zahl an Chips je Wafer, die maßgeblich in die Chipfläche und somit in den Preis eingeht. So besitzen beispielsweise NOR-Flashs technologiebedingt bei gleicher Strukturgröße geringere Speicherkapazitäten als NAND-Flashs, da ihre Speicherzellen mehr Transistoren und damit Platz auf dem Die erfordern.

Bei sogenannten Die-Shrinks geht es darum, die Strukturgröße unter Beibehaltung der Halbleiterfunktionalität gegen eine kleinere auszutauschen. Ein und dasselbe funktionale Design kann somit in mehreren verschiedenen Strukturgrößen produziert werden. Die kleineren Strukturen weisen oftmals eine ihrer Transistor-Technologie entsprechende geringere Verlustleistung im Ruhezustand und bei Schalthandlung auf, so dass die für Halbleiter typisch erreichbare maximale Taktrate bei kleineren Strukturen für gewöhnlich höher ist. Wird die Die-Größe dagegen beibehalten, dann ergeben sich Möglichkeiten zur Erweiterung von skalierbaren Einheiten, z. B. der Caches eines Prozessors.

Bei kleineren Strukturen muss der jeweilige Hersteller zunächst einige Schritte zur Prozessoptimierung unternehmen um die bis dahin üblichen Ausbeuten wieder zu erreichen. Entsprechend ist ein Umstieg auf eine Technologie mit kleinerer Strukturgröße immer auch mit Kosten und Risiken verbunden. Es wird natürlich versucht, diese durch geeignete Forschungen und Erprobungen bereits im Vorfeld möglichst gering zu halten, um möglichst frühzeitig eine wirtschaftliche Effizienz zu erreichen.

Geschichte

Strukturgrößen wurden traditionell in Mikrometer angegeben. Dies behielt man auch längere Zeit im Submikrometerbereich bei, Strukturgrößen wurden als mit Null beginnender Dezimalbruch angegeben. Letztmals erfolgte dies bei 0,14 µm. Ab 130 nm wechselte man zur übersichtlicheren Angabe in Nanometer.

| Name | Hersteller | Jahr | Technologie-Besonderheiten bzw. -Neuheiten | Knoten |

|---|---|---|---|---|

| 4004-Prozessor | Intel | 1971 | PMOS | 10 µm |

| NMOS-Logik | 6 µm | |||

| HMOS-Halbleiter | 1,5 µm | |||

| i386DX | Intel | 1984 | 1,5 µm | |

| i486DX2-66 mit P24-Kern | Intel | 1992 | 0,8 µm | |

| Pentium P5 | Intel | 1993 | BiCMOS | 0,8 µm |

| Pentium P55C | Intel | 1997 | CMOS | 0,35 µm |

| Athlon (K7) | AMD | 1999 | 0,25…0,18 µm | |

| VIA C3 (C5B-Revision) | VIA | 2001 | 0,15 µm | |

| 256-MBit-DRAM-Speicherchip [3] | Infineon | 2002 | 0,14 µm | |

| Storm-1 (DSP) | SPI | 130 nm | ||

| NEC und TSMC | 2001 | 100 nm | ||

| 2007 | 65 nm | |||

| Intel Core 2 Duo | Intel | 2007 | 45 nm | |

| XTREME (Jenoptik und Ushio, gefördert von Intel) | um 2009 |

Grundlagenforschung Optiken für EUV (13,5 nm) | anfangs: <40 nm 2009: 32 nm später: 13,5 nm | |

| Speicher mit 45 GByte/cm2 [4] | Universität Tokyo | 2004 | Optischer Speicher | 35 nm |

| Intel Core i3/i5/i7 (Sandy Bridge in Planartechnik) |

Intel | 2010 | 32 nm | |

| MIT | 2008[5] | Lithografietechnik | 25 nm | |

| NAND-Flashspeicher | Intel, Micron | 2010[6] | 25 nm | |

| Intel Core i3/i5/i7 (Ivy Bridge in FinFET-Technik) |

Intel | 2012 | 22 nm | |

| NAND-Flashspeicher | Toshiba | 2013[7] | 19 nm | |

| Intel-Skylake-Mikroarchitektur | Intel | 2015 | FinFET | 14 nm |

| AMD Ryzen 3000 (ZEN2) | AMD bei TSMC | 2019 | 7 nm | |

| 5G-Modem (Fusion-Platform)[8] | Qualcomm bei (Samsung?) | 2019 | 10 nm | |

| Snapdragon 8150 (Fusion-Platform)[9] | Qualcomm bei TSMC | 2019 | 7 nm | |

| Prodigy[10] | Tachyum bei (TMSC)? | 2020? | 7 nm | |

| Apple A14 Bionic[11] | Apple bei TSMC | 2020/21? | 5 nm |

Weblinks

- Wettlauf um neue Lithografie-Techniken verschärft sich, heise-Verlag, 2001: Bericht zur SPIE Microlithography conference mit Prognosen zur erwarteten Entwicklung – wurde durch die Realitäten bereits 2007 überholt.

- Sematech nimmt Forschungszentrum für EUV-Lithografie-Lacke in Betrieb, heise-Verlag, 2006: Lackentwicklung für Strukturgrößen bis 13,5 nm; Intel-EUV-Serienproduktion für 2009 geplant

Einzelnachweise

- International Technology Roadmap for Semiconductors 2013. Process Integration, Devices and Structures. 2013, S. 18 (PDF [abgerufen am 21. September 2014]).

- S. Narasimha u. a.: 22nm High-performance SOI technology featuring dual-embedded stressors, Epi-Plate High-K deep-trench embedded DRAM and self-aligned Via 15LM BEOL. In: Electron Devices Meeting (IEDM), 2012 IEEE International. 2012, S. 3.3.1–3.3.4, doi:10.1109/IEDM.2012.6478971.

- Infineon Technologies in Dresden. (PDF) Abgerufen am 6. September 2014.

- Japanische Superdisk speichert 45 GByte/cm2. Abgerufen am 6. September 2014.

- Christof Windeck: MIT-Forscher zeigen Lithografietechnik für 25-nm-Strukturen. Auf: Heise Online. 11. Juli 2008 (Nachrichtenmeldung)

- Intel, Micron Introduce 25-Nanometer NAND – The Smallest, Most Advanced Process Technology in the Semiconductor Industry. Intel News Release, 1. Februar 2010, abgerufen am 1. Juli 2010.

- Toshiba mass produces 19nm NAND modules up to 128GByte. Toshiba News Release, 31. Oktober 2013, abgerufen am 17. Juli 2014.

- Qualcomm kündigt 7-nm-Snapdragon mit 5G an

- Qualcomm kündigt 7-nm-Snapdragon mit 5G an

- Kleiner Supercomputer-Chip soll Intels Xeons schlagen

- Mike Peterson: Apple A14 Bionic announcement hints at „iPhone 12“ performance. In: AppleInsider. 15. September 2020, abgerufen am 1. Oktober 2020.