Intel 8086

Der Intel 8086 ist ein 16-Bit-Mikroprozessor von Intel. Entwickelt 1978, wurde er zum Urvater der 80x86-Familie. Das Design basierte auf Intels 8-Bit-CPUs 8080 und 8085, der Befehlssatz war so konzipiert, dass Assembler-Quellcode für den 8080/8085 leicht automatisch in gültigen 8086-Quellcode umgewandelt werden konnte. Eine direkte Kompatibilität, also die Möglichkeit, die 8080-Programme auch ohne Neuassemblierung ablaufen zu lassen, bestand aber nicht. Wie dem 8080 fehlten dem 8086 einige wesentliche Bausteine wie Interrupt- und DMA-Controller, die als externe Chips dazukamen. Der 8086 unterstützt auch keine Gleitkomma-Operationen, kann jedoch von Haus aus mit einem Intel 8087-Koprozessor zusammenarbeiten, der dann die Gleitkomma-Berechnungen ausführt. Der Intel-8089-Koprozessor bietet erweiterte I/O-Funktionen und dient unter anderem als DMA-Controller. Später erschien die Version 8088 mit auf 8 Bit reduziertem externem Befehls- und Datenbus.

| << Intel 8086 >> | |

|---|---|

Intel D8086 | |

| Produktion: | 1978 bis 1990er |

| Produzenten: | |

| Prozessortakt: | 5 MHz bis 10 MHz |

| Fertigung: | 3 µm, NMOS oder enhanced NMOS |

| Befehlssatz: | x86 (16 Bit) |

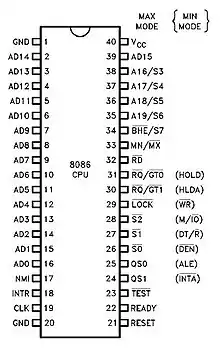

| Sockel: | 40-pin DIP |

Speichersegmentierung

Eine Besonderheit ist die Speichersegmentierung. Mit einem 16-Bit-Adressregister ist es nur möglich, maximal 64 KB Speicher zu adressieren. Um trotzdem mehr möglichen Speicher adressieren zu können, gab Intel dem Prozessor 20 Adressleitungen für 220 Adressen (max. 1 MB Arbeitsspeicher). Um eine Adresse zu speichern, werden zwei Register verwendet: ein Segment- und ein Offsetregister. Die Adresse einer physikalischen Speicherstelle berechnet der Prozessor automatisch, indem er die Segmentadresse × 16 nimmt und die Offsetadresse addiert. So entstehen im Speicher 65.536 um 16 Byte versetzte Adressbereiche (Segmente) zu je 64 KB Größe. Auf diese Weise kann der Chip 1 MB adressieren, wobei innerhalb jedes Segments mit 16-Bit-Adressen gearbeitet werden kann. Da es nur 20 Adressleitungen gibt, erscheinen die untersten 64 KB (-16 Byte) noch einmal „gespiegelt“ am oberen Ende des Adressraums (da es bei der Adressrechnung zu einem Überlauf kommt).

Wenn beispielsweise das Segmentregister die Adresse 1234hex und das Offset-Register die Adresse 5678hex enthält, was meist als 1234:5678 geschrieben wird, dann wird im Speicher auf die Adresse 1234hex × 10hex + 5678hex = 12340hex + 5678hex = 179B8hex zugegriffen.

Vorteil der Speichersegmentierung ist unter anderem eine einfachere Portierbarkeit von Programmen, die nur mit 16-Bit-Adressen arbeiten, und eine höhere Code-Dichte, Nachteil die umständliche Programmierung und die Beschränkung auf ein Mebibyte; andere 16-Bit-Architekturen erlaubten meist einen Adressraum von mindestens 16 MB. Allerdings war 1 MB Ende der 1970er Jahre für einen Mikrocomputer ohnehin viel mehr, als benötigt oder tatsächlich an Speicher eingebaut wurde, auch wegen der hohen Preise für RAM (der IBM-PC hatte zum Beispiel zunächst je nach Variante nur maximal 64 KB Speicher, Heimcomputer aus der gleichen Zeit meist noch deutlich weniger).

Register

Verglichen mit anderen 16-Bit-Prozessoren hat der 8086 nur eine kleine Anzahl an Registern. Für viele Operationen ist oft nur ein bestimmtes Register verwendbar – der 8086 ist damit ein erweiterter Akkumulatorrechner, als Allzweck-Register stehen meist nur vier zur Verfügung. Eine oft genutzte fest einem Register zugewiesene Funktion ist die (Ganzzahl-)Multiplikation: Der Multiplikand muss im Register AX abgelegt werden und danach der Multiplikationsbefehl mit dem Multiplikator als Argument aufgerufen werden. Das Ergebnis erhält man dann in den Registern DX und AX. Durch diese feste Registerbindung ist man häufig gezwungen, Werte auf den Stack oder in den Arbeitsspeicher zu sichern und von dort zu laden, da die Prozessorbefehle häufig vorgeben, welche Register gerade für die Zwischenwerte genutzt werden können. Andere 16-Bit-Prozessoren erlauben dagegen, dass man für jede Operation die zu verwendenden Allzweck-Register auswählt und damit seltener Zwischenergebnisse auf Stack und im Arbeitsspeicher sichern muss (Registermaschine); auch hatten diese Architekturen meist 16 oder mehr Register, während der 8086 (abzüglich der erwähnten Segmentregister) nur vier halbwegs allgemeine und vier speziellere Register unterstützte. Dies ist insofern ein Problem, da Zugriffe auf den Arbeitsspeicher im Vergleich zu Registerzugriffen sehr langsam sind.

Dieses Register-Konzept vererbte der 8086 auf seinen Nachfolger 80286 und auf alle späteren, zur sog. x86-Familie zählenden Prozessoren, jedoch wurde die Zahl der Register im neuen x64-Modus der aktuellen Prozessoren immerhin verdoppelt, zusätzlich sind die Register der aktuellen x86-Generation 64 Bit „breit“.

Betriebsarten

Der 8086 (und auch der 8088) kann in einem Minimum- und einem Maximummodus betrieben werden. Die Wahl erfolgt über den MN/MX-Pin 33. Wird er auf 0 V (Low) geschaltet, so arbeitet der 8086/88 im Maximummodus, bei +5 V (High) im Minimummodus. Im Minimummodus können kompakte einfache Schaltungen realisiert werden; die erforderlichen Steuerleitungen stellt der Prozessor selbst zur Verfügung. Der Maximummodus ist in erster Linie für den Multiprozessorbetrieb bzw. für die Arbeit mit den Koprozessoren 8087 und 8089 vorgesehen.

Hilfsbausteine

Der 8086 hat keinen internen Oszillator. Der erforderliche Takt wird daher extern vom Oszillator-Chip 8284 generiert. Wird der Prozessor im Maximummodus betrieben – was meistens der Fall ist –, werden die erforderlichen Steuerleitungen WR, M/IO, DT/R, DEN, ALE und INTA nicht bereitgestellt, sondern müssen durch den Bus-Controller 8288 bereitgestellt werden. Ist der Prozessor Teil eines Multiprozessorsystems, ist zusätzlich der Bus-Arbiter 8289 erforderlich. Ferner ist zur Abtrennung der Adressen aus dem gemultiplexten Adress-/Datenbus ein Latch erforderlich, zum Beispiel der 8282. Für die ausreichende Ansteuerung der gesamten Bussysteme wie auch im Multiprozessorbetrieb benötigt man bidirektionale Treiber, zum Beispiel den 8286.

Einsatz

Der kompatible, aber mit 8 Bit Datenbus-Busbreite etwas langsamere 8088, der wenig später auf den Markt kam, wurde vor allem im IBM-PC und dessen Nachbauten eingesetzt. Einige Hersteller verwendeten aber auch den 8086, darunter Olivetti im Modell M 24. Seine größte Verbreitung erhielt der Prozessor in dem von dem englischen Computerhersteller Amstrad erfolgreich vertriebenen PC-Clone PC1512 und PC1640. In Deutschland wurden diese Rechner von der Schneider Computer Division unter eigenen Namen vermarktet. Der 8086 kam aber auch z. B. bei einem der ersten Tabletcomputer, dem GRiDPad und bei der Raumsonde Cassini-Huygens zum Einsatz.

Die NASA durchsuchte immer wieder den Restbestände-Markt nach einer bestimmten, damals bereits lange nicht mehr hergestellten Spezialversion des 8086, um das Shuttleprogramm durchführen zu können.[1][2] Diese Version des 8086 ist besonders unempfindlich gegen elektromagnetische Strahlung und wurde nicht nur vom Militär, sondern auch von Herstellern von medizinischen Geräten verwendet.

Architektur

- Adressbus: 20 Bit, byteorientiert (identisch bei 8088)

- Max. adressierbarer Speicher: 1 MB

- interner und externer Datenbus: 16 Bit, byteweise ansprechbar (8088: extern nur 8 Bit breit)

- Verarbeitungsbreite: 16 Bit

- Befehle: ca. 100

- 14 Register:

- vier allgemeine 16-Bit-Register, auch ansprechbar als Low- oder High-Teil zu je 8-Bit:

- AX: Akkumulator, BX: Basis-Register, CX: Count-Register, DX: Daten-Register

- zwei 16-Bit-Pointer-Register:

- SP: Stackpointer, BP: Basepointer

- zwei 16-Bit-Index-Register:

- SI: Source Index, DI: Destination Index

- vier 16-Bit-Segment-Register:

- CS: Codesegment, DS: Datensegment, SS: Stacksegment, ES: Extrasegment

- 16-Bit-Befehlszeiger:

- IP: Instruction Pointer

- 16-Bit-Status-Register mit 9 Flags:

- CF: Übertragflag (engl. carry flag),

- PF: Paritätsflag (engl. parity flag),

- AF: Hilfsübertragsflag (engl. auxiliary carry flag),

- ZF: Nullflag (engl. zero flag),

- SF: Vorzeichenflag (engl. sign flag),

- TF: Einzelschrittflag (engl. trap flag),

- IF: Interrupt-Aktivierungs-Flag (engl. interrupt enable flag),

- DF: Richtungsflag (engl. direction flag),

- OF: Überlaufflag (engl. overflow flag)

Technische Daten

- L1-Cache: nicht vorhanden

- L2-Cache: nicht vorhanden

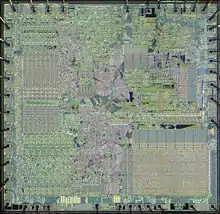

- Anzahl der Transistoren: 29.000

- Bauform: DIL mit 40 Pins

- Betriebsspannung (VCore): +5 V

- Erscheinungsdatum: 1978

- Fertigungstechnik: 3 µm

- Die-Größe: 33 mm2 bei 29.000 Transistoren

- Taktraten:

- 8086: 4,77 MHz (0,33 MIPS)

- 8086-2: 8 MHz (0,66 MIPS)

- 8086-1: 10 MHz (0,75 MIPS)

Derivate und Nachbauten

Der 8086 wurde von verschiedenen Herstellern in Lizenz und in verschiedenen Chipgehäusen gefertigt. In der damaligen UdSSR wurde mit Hilfe des Reverse Engineering eine eigene nicht lizenzierte Version (Klon) entwickelt, die К1810-Reihe[3].

8086-Nachbau KR1810VM86 (kyrillisch КP1810ВМ86) der K1810-Reihe aus der damaligen UdSSR

8086-Nachbau KR1810VM86 (kyrillisch КP1810ВМ86) der K1810-Reihe aus der damaligen UdSSR

Wesentliche Konkurrenten

Außer pin- und funktionsgleichen Nachbauten (vor allem die in CMOS-Technologie hergestellten NEC V20 und V30) sowie der günstigeren, „abgespeckten“ Variante 8088, wurden in Konkurrenzprodukten zum IBM PC gerne der Motorola-68000-Prozessor verwendet, selten der Zilog Z8000, selten der National Semiconductor NS16032. (Sowohl Motorola 68000 als auch NS16032 sind jedoch 32-Bit-Prozessoren.)

Peripheriebausteine

- Intel 8282/8283: 8-Bit-Latch

- Intel 8284: Taktgeber

- Intel 8286/8287: bidirektionaler 8-Bit-Treiber

- Intel 8288: Bus-Controller

- Intel 8289: Bus-Arbiter

Literatur / Datenblätter

- Intel: The 8086 Family User's Manual (PDF; 9,7 MB), Oktober 1979

- Josef Koller: 16 Bit Microcomputer, 1. Auflage, Hofacker Verlag, München 1981, ISBN 3-921682-80-0.

- NEC Electronics (Europe) GmbH, 1982 Catalog, S. 435–446.

- Datenblatt Intel 8086 (PDF-Datei; 380 kB)

- Datenblatt Intel 80C86 (PDF-Datei; 277 kB)

Weblinks

Einzelnachweise

- Heise Online: NASA sucht im Internet nach uralten Chips

- NY Times: For Old Parts, NASA Boldly Goes . . . on eBay

- СЕРИИ К1810. Abgerufen am 14. März 2021 (russisch).

- Harris CMOS Digital Data Book. Abgerufen am 14. März 2021 (englisch, siehe Kapitel 3 "CMOS 80C86 Family").