Intel-Core-Mikroarchitektur

Die Intel-Core-Mikroarchitektur ist eine von Intel entwickelte Mikroarchitektur. Sie basiert auf der älteren Intel-P6-Architektur und löste im Desktop- und Serverbereich die NetBurst-Architektur ab. Die Intel-Core-Mikroarchitektur wurde am 7. März 2006 auf dem Intel Developer Forum offiziell vorgestellt. Die ersten Prozessoren, in der sie verwendet wurden, erhielten den Namen Intel Core 2. Aktuelle Prozessoren basieren auf einer Weiterentwicklung dieser Architektur. Seit 2008 wurde die Architektur nicht mehr Intel Core (Intel Core Solo/Intel Core Duo) bzw. Intel Core 2 genannt, sondern in Intel Core i umgetauft. Die Intel-Nehalem-Mikroarchitektur stellt die erste Generation dieser Intel Core i genannten Prozessoren dar.

| Intel Core (Mikroarchitektur) | |

|---|---|

| Hersteller | Intel |

| Herstellungsprozess | 65 nm (Intel Core) 45 nm (Penryn) |

| Sockel | (µFC-)BGA 956 Socket P |

| L1-Cache | 32+32 KB pro Kern |

| L2-Cache | 256 KB pro Kern |

| Nachfolger | Nehalem Westmere |

Entwicklung

Die am nächsten mit der Intel-Core-Mikroarchitektur verwandten Prozessoren gehören zu den Serien Intel Pentium M und Intel Core, welche auf einer abgeänderten Variante der P6-Architektur basieren. Auf Grundlage dieser Mobilprozessoren wurde in Intels Israel Development Center (IDC) in Haifa die Core-Mikroarchitektur entwickelt. Ein zentrales Merkmal, welches allerdings aus der NetBurst-Architektur eingefügt wurde, ist die 64-Bit-Erweiterung Intel 64.

Technik

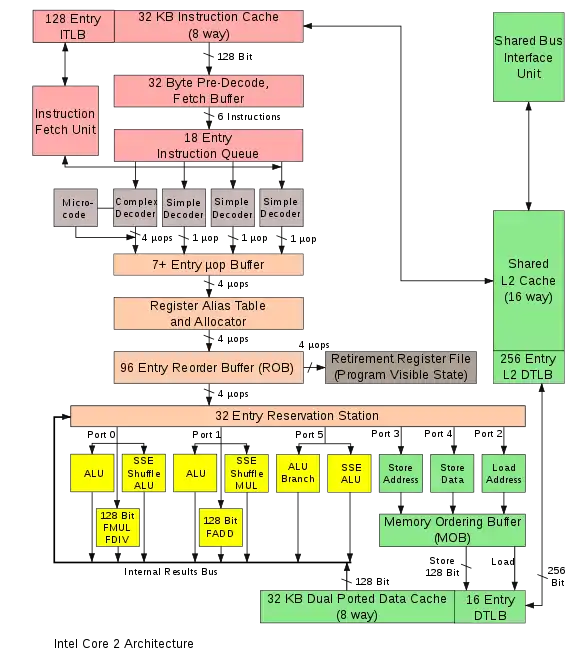

Die Intel-Core-Mikroarchitektur ist mit ihrer relativ kurzen, 14-stufigen Pipeline, im Gegensatz zu den max. 31 Stufen der Netburst-Architektur auf eher moderate Taktraten ausgelegt und erreicht ihre Leistung vor allem aufgrund einer hohen Anzahl von Befehlen pro Taktzyklus (IPC = Instructions per cycle). Daher besitzen Prozessoren mit gleicher Leistung eine deutlich niedrigere Leistungsaufnahme im Vergleich zur NetBurst-Architektur, gegenüber dem Intel Core musste hingegen die Thermal Design Power erhöht werden. Der Großteil der Produkte besitzt mehrere Kerne, jedoch gibt es auch als Celeron oder Core 2 Solo verkaufte Einkernprozessoren.

Merkmale

Die Intel-Core-Mikroarchitektur nutzt ein vierfach superskalares Design, während alle Vorgänger (Intel Pentium M/ Intel Core bzw. NetBurst-Prozessoren) auf einem dreifach superskalaren Design basieren. Intel nennt dieser Erweiterung „Intel Wide Dynamic Execution“. Verbreitert wurde auch der Bus der SSE-Einheiten. Das Design der Vorgänger bot hier lediglich 64 Bit, während durch die neue Architektur 128 Bit möglich sind. Daher können SSE-, SSE2- und SSE3-Befehle in nur einem Taktzyklus verarbeitet werden. Außerdem wurden noch neue SSSE3-Befehle integriert. Dieses Feature beschreibt Intel als „Advanced Digital Media Boost“.

Die von der IA-64- und Netburst-Architektur übernommene Fähigkeit, Daten nicht nur spekulativ im Voraus in den Cache zu laden (Prefetching), sondern auch bereits zu verarbeiten (Memory Disambiguation), wird von Intel „Smart Memory Access“ genannt. Sollte sich die spekulative Ausführung als falsch erweisen, wird das Ergebnis verworfen und neu begonnen. Der L2-Cache kann dabei dynamisch den verschiedenen CPU-Kernen zugewiesen werden („Intel Advanced Smart Cache“). Falls ein CPU-Kern inaktiv sein sollte, wird dem anderen CPU-Kern der gesamte L2-Cache zugewiesen.

Unter dem Namen „Intel Intelligent Power Capability“ wurde ein neues Stromsparkonzept integriert, das im Vergleich zu SpeedStep eine feinere Abstufung besitzt und deswegen effizienter arbeitet.

Penryn

Mit dem Shrink von 65 nm auf 45 nm, das Ende 2007 unter dem Codenamen „Penryn“ geschah, wurde SSE4.1 eingeführt. Für SSE-Befehle wurde zudem die „Super Shuffle Engine“ eingeführt, die vor und nach der Berechnung auszuführende Tätigkeiten beschleunigen soll. Die Divisionseinheit wurde mit dem Radix-16 Divider statt bisherigem Radix-4 Divider ausgestattet. Konkret profitieren davon Befehle, die Divisions- oder Wurzelberechnungen durchführen müssen. Der „Memory Order Buffer“ wurde optimiert, er kann jetzt nicht ausgerichtete Adressen besser verwalten, da nun auch auf diese das Store-Forwarding häufiger angewendet werden kann. Dadurch werden Ladelatenzen minimiert, das Warten auf ein Cache-Update und der Zugriff auf den Cache entfällt in solchen Fällen. Die Intel Virtualization Technology wurde auch im Detail verbessert, und weitere kleine Optimierungen wurden an der Architektur vorgenommen.

Bei Prozessoren für Notebooks wurde das Power-Management um Deep-Power-Down-Modus (C6) erweitert, bei dem alle ausführenden Einheiten des Prozessors und die Caches komplett ausgeschaltet werden. Da sich C6 nicht immer lohnt, wird durch einen Algorithmus entschieden, ob der vom Betriebssystem kommende Befehl zu C6 ausgeführt wird oder ignoriert und stattdessen nur in C4 gewechselt wird.

CPUs mit Intel-Core-Mikroarchitektur

- Intel Celeron (Core)

- Intel Celeron M: ab „Merom-1024“

- Intel Core 2

- Intel Pentium Dual-Core: ab „Allendale-1024“ bzw. „Merom-1024“

- Intel Xeon (Core)

Prozessoren mit dem Namen Intel Core basieren nicht auf der Intel-Core-Mikroarchitektur.