Intel-Sandy-Bridge-Mikroarchitektur

Die Intel-Sandy-Bridge-Mikroarchitektur ist eine von Intel entwickelte Mikroarchitektur, auf deren Basis erste Modelle im Januar 2011 vorgestellt wurden. „Sandy Bridge“ basiert teilweise auf den Vorgängerarchitekturen „Core“ und „Westmere“, wobei einige Elemente noch aus der Netburst-Architektur stammen. Intel selbst verweist auf Sandy-Bridge-Prozessoren als „2nd Generation Intel Core Processors“ und auf Ivy-Bridge-Prozessoren als „3rd Generation Intel Core Processors“.[1]

| Sandy Bridge (Mikroarchitektur) | |

|---|---|

| Hersteller | Intel |

| Herstellungsprozess | 32 nm |

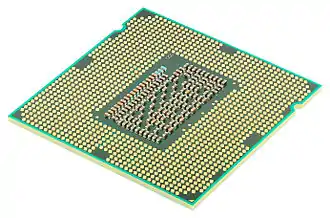

| Sockel | Sockel 1155 |

| L1-Cache | 32+32 KB pro Kern |

| L2-Cache | 256 KB pro Kern |

| Vorgänger | Nehalem (Bloomfield, Lynnfield, Clarksfield) Westmere (Clarkdale, Arrandale, Gulftown) |

| Nachfolger | Haswell (tock) Broadwell (tick) |

Entwicklung

Ursprünglich ist die Sandy-Bridge-Architektur unter dem Codenamen „Gesher“ entwickelt worden und wurde erstmals auf dem Intel Developer Forum 2006 vorgestellt.[2] Auf dem IDF 2007 wurde der Name dann in „Sandy Bridge“ geändert.[3]

Die Sandy-Bridge-Architektur wurde vom selben Entwicklungsteam entwickelt, das bereits die Core-Architektur herausgebracht hatte (Intels Israel Development Center, IDC, in Haifa). Im Vergleich zur Nehalem-Architektur, die von einem anderen Entwicklungsteam stammt, wurde die Pipeline wieder verkürzt, während sie bei der Nehalem-Architektur von 14 auf 16 Pipelinestufen verlängert wurde.

Neuerungen der Sandy-Bridge-Architektur

Aufgrund der weiteren Integration von Komponenten wie dem Grafikprozessor (GPU) und der Auslegung der Architektur für mehr als vier Kerne hat Intel die Architektur modular aufgebaut und sich von der klassischen Crossbar zur Anbindung des Last Level Cache (L3-Cache) verabschiedet. Stattdessen werden die Caches mit Kernen, dem Speichercontroller und der GPU mit einem internen Ringbus verbunden. Dieser Ringbus besteht dabei aus vier Links: einem 256-Bit-Datenring, einem „Request-Ring“ (request = anfordern), einem „Acknowledge-Ring“ (acknowledge = bestätigen) und einem Snoop-Ring (snoop = lauschen, spionieren). Der Ringbus verläuft dabei über dem Cache und nimmt keine zusätzliche Die-Fläche in Anspruch. Bei einem mit 3 GHz getakteten Prozessor gibt Intel die Bandbreite pro Verbindung auf theoretische 96 GB/s an.

Zu den umfassendsten Architekturänderungen gehört auch der Nachfolger der SSE4-Befehlssatzerweiterung: AVX (Advanced Vector Extensions, dt.: fortgeschrittene Vektor-Erweiterungen). Während SSE4 auf 128 Bit breiten Registern rechnet, sind für AVX 256 Bit breite Register nötig. Durch die doppelt so breiten Register können nun bis zu acht Gleitkomma- oder Integer-Operanden in einem Vektor zusammengefasst werden und anschließend mit dem Vektor gewöhnliche arithmetische oder logische Operationen durchgeführt werden.

Aufgrund der Einführung von 256-Bit-Befehlen hat Intel die aus der Netburst-Architektur bekannte „Physical Register File“ (PRF) wieder eingeführt. Während bei der Core- und Nehalem-Architektur die Operanden stets mitgeführt wurden und daher zusätzliche Puffer benötigten, die mit den großen 256-Bit-Befehlen hätten weiter vergrößert werden müssen, kann mit der PRF auf diese zusätzlichen Puffer verzichtet werden, da nun mit einem Pointer (Zeigervariable) auf PFR diese Operanden erreichbar sind.

Die Abarbeitung von 256-Bit-Befehlen geschieht über das Zusammenschalten der Gleitkomma- mit der SIMD-Integer-Pipeline, was mittels zusätzlicher Transistoren erreicht wird, zudem wurden einige Funktionen zwischen den Pipelines getauscht. Dieses Vorgehen erspart das Vergrößern einer Pipeline von 128-Bit-Registern auf 256-Bit-Register, allerdings ist auch der mögliche Durchsatz kleiner. Zudem unterstützt die neue Umsetzung keine Fused-Multiply-Add (FMA) mit 256-Bit-Befehlen.

Als weitere Neuerung ist der sogenannte „Dynamic Turbomode“ bekannt geworden. Zusätzlich zu den Funktionen die aus der Nehalem/Westmere-Architektur bekannt sind, können die Sandy-Bridge-Prozessorkerne kurzfristig über die TDP hinaus ihren Takt anheben, falls der Prozessor vorher unbeschäftigt ("idle") war und damit kurzfristig höher belastet werden kann. Bei Dauerbelastung regelt sich der Prozessor dann wieder auf die vorgeschriebene TDP herunter.

Während die Grafikeinheit beim mobilen Ableger „Arrandale“ der Westmere-Architektur noch per Treiber in speziellen Fällen übertaktet wurde, bindet Intel die GPU bei Sandy Bridge nun mit in den hardwarebasierten Turbo-Modus ein. Wie auch bei der Nehalem/Westmere-Architektur ist eine „Power Control Unit“ verbaut, also ein Mikrocontroller, der die Energieflüsse überwacht und steuert. Die Kerne mit den Caches, die Grafikeinheit und die integrierte North-Bridge (Speicher- und PCIe-Controller, DMI) sind jeweils getrennt an ihre eigene Energieversorgung angebunden und können dynamisch passend zur Auslastung geregelt werden.

Für einige Sandy-Bridge-Modelle stand erstmals die Funktion Intel Quick Sync Video (hardware-basierte Unterstützung von En- und Decodierung von Videos) zur Verfügung. „Quick Sync“ ermöglicht ein schnelles Umwandeln beispielsweise eines DVD-Videos in ein Smartphone-Videoformat.

Chipsatz für Sandy-Bridge-Prozessoren

Zum Betrieb der Sandy-Bridge-Prozessoren ist ein Cougar-Point-Chipsatz der Intel-6-Serie notwendig. Ende Januar 2011 wurde bei diesem im B2-Stepping vorliegenden Chipsatz ein Hardware-Bug entdeckt, der zu einem Produktionsstopp und zunächst zu einer Rückrufaktion von Seiten Intels führte. Die Fertigung des Chipsatzes wurde zum gleichen Zeitpunkt auf eine vom Fehler bereinigte B3-Stepping-Version[4] umgestellt. Später entschied sich Intel, die Chipsätze im B2-Stepping an OEMs weiter zu verkaufen,[5] da nur die vier SATA-3-Gb/s-Ports von dem Problem betroffen sind und bei Nutzung der beiden verbliebenen SATA-6-Gb/s-Ports keine Probleme entstehen. Solche Mainboards könnten dann in Notebooks und Komplettsystemen eingesetzt werden, in denen nur zwei Laufwerke im System verbaut sind. Zudem können noch zusätzliche SATA-6-Gb/s-Ports durch Zusatzchips realisiert werden.

Ivy Bridge

Ivy Bridge wurde am 23. April 2012 vorgestellt. Prozessoren auf Basis von Ivy Bridge werden in einem 22-nm-Fertigungsverfahren hergestellt, das nicht mehr der bislang üblichen Planartechnik entspricht, sondern sogenannte Multigate-Feldeffekttransistoren nutzt. Es bleibt jedoch weitgehend die gleiche Sandy-Bridge-Architektur, zumindest was die Prozessorkerne angeht, denn dort werden nur Detailoptimierungen durchgeführt. Die integrierte Grafik unterstützt hingegen erstmals DirectX 11, OpenGL 3.1 (OpenGL 4.0 seit den 9.17.10.2729-Beta-Treibern)[6] und OpenCL. Zudem ist sie deutlich leistungsfähiger und bekommt ihren eigenen L3-Cache.[7]

Der Nachfolger von Ivy Bridge erschien im Jahr 2013 und trägt den Codenamen Haswell.

Chipsatz für Ivy-Bridge-Prozessoren

Ivy-Bridge-Prozessoren sind grundsätzlich kompatibel zu den Intel-6-Serie-Chipsätzen für die Sandy-Bridge-Prozessoren. Zusätzlich führt Intel mit Ivy Bridge neue Intel-7-Serie Chipsätze mit zusätzlichen Ausstattungsmerkmalen, wie etwa USB-3.0-Schnittstellen, ein. Auf vielen Mainboards mit ursprünglich für Sandy-Bridge entwickelten Chipsätzen konnten aufgrund des gleichen Sockels nach einem Bios-Update Prozessoren der Ivy-Bridge-Generation eingebaut werden. Für die Nutzung von PCI-Express 3.0 ist ein Prozessor der Ivy-Bridge-Reihe erforderlich, da nur Ivy-Bridge-Prozessoren den dafür notwendigen Controller besitzen.

Modelle

Sandy Bridge Duo

- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 3 MiB mit Prozessortakt

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, AVX, SMT. Core i5-CPUs haben zusätzlich AES-Instruktionen, TXT und VT-d aktiviert.

- integrierter Dual-Channel-DDR3-Speichercontroller und PCIe-2.0-Controller mit 16 Lanes

- integrierte GPU

- Sockel 1155, DMI mit 5 GT/s (Vollduplex, max. 20 Gbit/s pro Richtung) und FDI

- Verlustleistung (TDP): 35–65 W

- Erscheinungsdatum: 20. Februar 2011

- Fertigungstechnik: 32 nm

- Die-Größe: 131 mm² bei 504 Millionen Transistoren inkl. HD-2000-GPU und integr. Northbridge, 149 mm² bei 624 Millionen Transistoren inkl. HD-3000-GPU-Kern und integr. Northbridge

- Taktraten: 2,5–3,3 GHz

- Modelle: Intel Core i3-2100 bis Intel Core i5-2390T

Sandy Bridge

- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 6 bis 8 MiB mit Prozessortakt

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, AES-Instruktionen, AVX, TXT. Ausnahme: Alle Prozessoren mit einem K hinter der Modellnummer und der Core i5 2300 ohne TXT und Intel VT-d. Außerdem haben nur die Core i7-CPUs SMT aktiviert.

- integrierter Dual-Channel-DDR3-Speichercontroller und PCIe-2.0-Controller mit 16 Lanes

- integrierte GPU (bei einigen Modellen deaktiviert)

- Sockel 1155, DMI mit 5 GT/s (Vollduplex, max. 20 Gbit/s pro Richtung) und FDI

- Betriebsspannung (VCore): k. A.

- Verlustleistung (TDP): 45–95 W

- Erscheinungsdatum: 9. Januar 2011

- Fertigungstechnik: 32 nm

- Die-Größe: 216 mm² bei 1,16 Milliarden Transistoren (inkl. GPU-Kern und integr. Northbridge)

- Taktraten: 2,3–3,5 GHz

- Modelle: Intel Core i5-2300 bis Intel Core i7-2700K

Sandy Bridge E

Sechskernprozessor (Hexa-Core)

- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 12 bis 15 MiB mit Prozessortakt

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, AES-Instruktionen, AVX, TXT, SMT

- integrierter Quad-Channel-DDR3-Speichercontroller und PCIe-3.0-Controller mit 40 Lanes (offiziell wird nur PCIe 2.0 unterstützt)

- Sockel 2011, DMI mit 5 GT/s (Vollduplex, max. 20 Gbit/s pro Richtung)

- Betriebsspannung (VCore): 0,6–1,35 V

- Verlustleistung (TDP): 130 W

- Erscheinungsdatum: 14. November 2011

- Fertigungstechnik: 32 nm

- Die-Größe: 435 mm² bei 2,27 Milliarden Transistoren (inkl. der deaktivierten Kerne)

- Taktraten: 3,2–3,5 GHz

- Modelle: Intel Core i7-3930K bis Intel Core i7-3970X

Sandy Bridge E (Quad)

- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 10 MiB mit Prozessortakt

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, AES-Instruktionen, AVX, TXT, SMT

- integrierter Quad-Channel-DDR3-Speichercontroller und PCIe-3.0-Controller mit 40 Lanes (offiziell wird nur PCIe 2.0 unterstützt)

- Sockel 2011, DMI mit 5 GT/s (Vollduplex, max. 20 Gbit/s pro Richtung)

- Betriebsspannung (VCore): 0,6–1,35 V

- Verlustleistung (TDP): 130 W

- Erscheinungsdatum: 14. Februar 2012

- Fertigungstechnik: 32 nm

- Die-Größe: 294 mm² bei 1,27 Milliarden Transistoren

- Taktraten: 3,6 GHz

- Modelle: Intel Core i7-3820

Ivy Bridge

- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 6 bis 8 MiB mit Prozessortakt

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, AES-Instruktionen, AVX, TXT. Ausnahme: Alle Prozessoren mit einem K hinter der Modellnummer und der Core i5-3450 ohne TXT und Intel VT-d. Außerdem haben nur die Core i7-CPUs SMT aktiviert.

- integrierter Dual-Channel-DDR3-Speichercontroller und PCIe-3.0-Controller mit 16 Lanes

- integrierte GPU

- Sockel 1155, DMI mit 5 GT/s (Vollduplex, max. 20 Gbit/s pro Richtung) und FDI

- Verlustleistung (TDP): 45–77 W

- Erscheinungsdatum: 23. April 2012

- Fertigungstechnik: 22 nm

- Die-Größe: 160 mm² bei 1,4 Milliarden Transistoren (inkl. iGPU und integr. Northbridge)

- Taktraten: 2,5–3,5 GHz

- Modelle: Intel Core i5-3330 bis Intel Core i7-3770K

Ivy Bridge Duo

- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 3 MiB mit Prozessortakt

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, AES-Instruktionen, AVX, SMT

- integrierter Dual-Channel-DDR3-Speichercontroller und PCIe-3.0-Controller mit 16 Lanes (offiziell wird nur PCIe 2.0 unterstützt)

- integrierte GPU

- Sockel 1155, DMI mit 5 GT/s (Vollduplex, max. 20 Gbit/s pro Richtung) und FDI

- Verlustleistung (TDP): 35 – 55 W

- Erscheinungsdatum: 2. September 2012

- Fertigungstechnik: 22 nm

- Die-Größe: 94 mm² (inkl. iGPU und integr. Northbridge)

- Taktraten: 2,8–3,4 GHz

- Modelle: Intel Core i3-3220T bis Intel Core i3-3240

Sandy Bridge

- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 6 bis 8 MiB mit Prozessortakt

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, AES-Instruktionen, AVX, SMT, TXT. Ausnahme: Core i7-263XQM ohne TXT, Intel VT-dInstruktionen.

- integrierter Dual-Channel-DDR3-Speichercontroller und PCIe-2.0-Controller mit 16 Lanes

- integrierte GPU

- Sockel PGA988 (G2) und Sockel BGA1224, DMI mit 5 GT/s (Vollduplex, max. 20 Gbit/s pro Richtung) und FDI

- Betriebsspannung (VCore):

- Verlustleistung (TDP): 45–55 W

- Erscheinungsdatum: Januar 2011

- Fertigungstechnik: 32 nm

- Die-Größe: 216 mm² bei 1,16 Milliarden Transistoren (inkl. GPU-Kern und integr. Northbridge)

- Taktraten: 2,0–2,7 GHz

- Modelle: Intel Core i7-2630QM bis i7-2960XM Extreme Edition

Sandy Bridge Duo

- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 3 MiB bis 4 MiB mit Prozessortakt

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, AVX, SMT. Ab Core i5-2500-Serie zusätzlich AES-Instruktionen, TXT und VT-d aktiviert.

- integrierter Dual-Channel-DDR3-Speichercontroller und PCIe-2.0-Controller mit 16 Lanes

- integrierte GPU

- Sockel PGA988 (G2) und Sockel BGA1023, DMI mit 5 GT/s (Vollduplex, max. 20 Gbit/s pro Richtung) und FDI

- Betriebsspannung (VCore):

- Verlustleistung (TDP): 17–35 W

- Erscheinungsdatum: März 2011

- Fertigungstechnik: 32 nm

- Die-Größe: 149 mm² bei 624 Millionen Transistoren (inkl. GPU-Kern und integr. Northbridge)

- Taktraten: 1,4–2,8 GHz

- Modelle: Intel Core i3-2310M bis Intel Core i7-2677M

Ivy Bridge

- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 6 bis 8 MiB mit Prozessortakt

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, AES-Instruktionen, AVX, TXT, SMT

- integrierter Dual-Channel-DDR3-Speichercontroller und PCIe-3.0-Controller mit 16 Lanes

- integrierte GPU

- Sockel PGA988 (G2) und Sockel BGA1224, DMI mit 5 GT/s (Vollduplex, max. 20 Gbit/s pro Richtung) und FDI

- Verlustleistung (TDP): 35–55 W

- Erscheinungsdatum: 29. April 2012

- Fertigungstechnik: 22 nm

- Die-Größe: 160 mm² bei 1,4 Milliarden Transistoren (inkl. iGPU und integr. Northbridge)

- Taktraten: 2,1–3,0 GHz

- Modelle: Intel Core i7-3610QM bis Intel Core i7-3940XM

Ivy Bridge Duo

- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 3 MiB bis 4 MiB mit Prozessortakt

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, AES-Instruktionen, AVX, SMT, TXT. Bei Modellen unterhalb des Core i5-3320M und bei Core i7-3517U ist TXT deaktiviert.

- integrierter Dual-Channel-DDR3-Speichercontroller und PCIe-3.0-Controller mit 16 Lanes, bei CPUs mit 17 W TDP auf PCIe-2.0 begrenzt

- integrierte GPU

- Sockel PGA988 (G2) und Sockel BGA1023, DMI mit 5 GT/s (Vollduplex, max. 20 Gbit/s pro Richtung) und FDI

- Verlustleistung (TDP): 17–35 W

- Erscheinungsdatum: 31. Mai 2012

- Fertigungstechnik: 22 nm

- Die-Größe: 118 mm² (inkl. iGPU und integr. Northbridge)

- Taktraten: 1,7–2,9 GHz

- Modelle: Intel Core i3-3110M bis Intel Core i7-3667U

Siehe auch

Weblinks

- Sandy Bridge: Aufbau und Technik. In: ht4u.net

- Intel „Ivy Bridge“: Architektur. In: computerbase.de

Einzelnachweise

- ark.intel.com

- IDF: Roadmap mit Penryn, Nehalem, Gesher. In: computerbase.de, 27. September 2006, abgerufen am 19. Mai 2010

- IDF: „Gesher“ heißt jetzt „Sandy Bridge“. In: computerbase.de, 17. April 2007, abgerufen am 19. Mai 2010

- Intel 6 Series Chipset Specification Update (Memento vom 25. Januar 2011 im Internet Archive) Intel, Februar 2011

- Findet Intels Chipsatz-Albtraum ein baldiges Ende? In: HT4U, 8. Februar 2011

- Intel HD Graphics Driver v2729 with OpenGL 4 Support and New OpenGL Extensions! In: geeks3d.com, 6. Mai 2012, abgerufen am 25. Mai 2012

- Intels "Ivy Bridge" im ausführlichen Test: Neuerungen rund um die iGPU. In: ht4u.net, 23. April 2012, abgerufen am 23. April 2012