Motorola 68000

Der Motorola 68000 ist ein 1979 eingeführter CISC-Prozessor aus der 68000er-Familie von Motorola (später Freescale, heute NXP). Er besitzt intern 32-Bit-Register, einen mit 32 Bit adressierten linearen Adressraum, davon 24 Bit extern verfügbar, acht 32-Bit-Datenregister, neun 32-Bit-Adressregister, ein 16-Bit-Statusregister sowie einen 16-Bit-Datenbus.

Eine Variante ist der Motorola 68008, bei dem der Datenbus auf 8 Bit sowie der Adressbus auf 20 Bit in der DIP-Version (bzw. 22 Bit in der PLCC-Version) reduziert sind. Als verbesserte Version kam der Motorola 68010 auf den Markt, der um Fehler bereinigt wurde und verbesserte Unterstützung von virtuellem Speicher bietet. Ein 68010 mit erweitertem Adressbus von 31 Bit wurde als Motorola 68012 angeboten. Später folgten noch der 68020, 68030, 68040 und 68060.

Die Bezeichnung 68000 stammt laut einer modernen Legende von der Anzahl Transistoren, die der Prozessor besitzt. Tatsächlich ist es jedoch die logische Fortsetzung der Typbezeichnung der älteren 8-Bit-Motorola-Prozessorfamilie Motorola 6800. Die Architektur der 68000-Familie basiert auf Mainframes, wie z. B. IBM360 sowie der LSI11/PDP11 von Digital Equipment, aber mit einem linearen Adressbereich, auf den ohne Verfahren wie Multiplexing, Segmentierung oder Paging direkt zugegriffen werden kann.

Der 68000er (auch 68k genannt) mit 8 MHz Taktfrequenz kam im 64-poligen DIL-Gehäuse (siehe Bild) auf den Markt.

Architektur und Befehlssatz

Die Prozessoren der 68000-Familie zeichnen sich durch die große Anzahl der Register und einen weitgehend orthogonalen Befehlssatz aus, d. h. fast alle Maschinenbefehle lassen sich mit allen Adressierungsarten verwenden. Der Befehlssatz ist folgendermaßen aufgebaut:

- BEFEHL.s <ea1>, <ea2>

Die Prozessoren der 68000-Familie sind sogenannte Zwei-Adress-Maschinen, wobei bei den meisten Befehlen eine variable Datenbreite mit .s = {B,W,L} verwendet werden kann (entspricht 8, 16 oder 32 Bit) und für die beiden Quell- und Ziel-Operanden <ea1> bzw. <ea2> eine der 68000-Adressierungsarten eingesetzt werden kann:

| Schreibweise | Beschreibung | Beispiel |

|---|---|---|

| Dn | Datenregister direkt | CLR.B D0 |

| An | Adressregister direkt | MOVEA.W A0,A1 |

| (An) | Adressregister indirekt | CLR.B (A0) |

| (An)+ | Adressregister indirekt mit Postinkrement | CLR.B (A0)+ |

| −(An) | Adressregister indirekt mit Predekrement | CLR.B −(A0) |

| d16(An) | Adressregister indirekt mit 16 Bit Offset | CLR.B 255(A0) |

| d8(An,Ri.s) | Adressreg. ind. mit 8 Bit Offset und Indexregister | CLR.B $44(A0,D0.L) |

| d16(PC) | PC-relativ mit 16 Bit Offset | CLR.B 22(PC) |

| d8(PC,Ri.s) | PC relativ mit 8 Bit Offset und Indexreg. | CLR.B 10(PC,A1.W) |

| #xxxxxxxx | Konstante (Immediate) | MOVEQ.L #15,D0 |

| $xxxx | Speicherdirekt mit 16-Bit-Adresse (Absolute Short) | CLR.B $8000 |

| $xxxxxxxx | Speicherdirekt mit 32-Bit-Adresse (Absolute Long) | CLR.B $11008000 |

oder die komplexen MC68020/30/40/60-Adressierungsarten:

| Schreibweise | Beschreibung | Beispiel |

|---|---|---|

| (dis1,An,Ri.s*scl) | Adressreg. indirekt mit 16-/32-Bit Offset | MOVE.B ($12345678,A1,A2.L*2),D0 |

| ([dis1,An],Ri.s*scl,dis2) | Doppelt indirekt mit Post-Index | MOVE.W ([5,A2],D0.W,$23456),D1 |

| ([dis1,An,Ri.s*scl],dis2) | Doppelt indirekt mit Pre-Index | MOVE.W ([5,A2,D0.W],$23456),D1 |

| (dis1,PC,Ri.s*scl) | PC-indirekt mit 16- oder 32-Bit Offset | JSR (WEITER,PC) |

| ([dis1,PC],Ri.s*scl,dis2) | PC-relativ,doppelt ind m. Post-Index | JSR ([SPRUNG,PC],D1,2) |

| ([dis1,PC,Ri.s*scl],dis2) | PC-relativ,doppelt ind. m. Pre-Index | MOVE.L ([PARAMETER,PC,D1.W],4),D1 |

Der 68000 hat nur eine 16-Bit-ALU und auch einen 16-Bit-Befehlssatz, der aber sowohl mit 8-, 16- als auch mit 32-Bit-Datentypen umgehen kann (32-Bit-Architektur). Die Typen MC68020/030/040/060 dagegen haben eine 32-Bit-ALU.

Beispiel für ein typisches M68000-Kommando:

| JSR <ea> (Jump to subroutine) |

| Befehlsformat 0100 1110 10mm mrrr |

Das Kommando (Opcode) ist 16 Bit breit. Drei Bits (m) werden für den Adressierungsmodus verwendet, drei weitere Bits für das benutzte (r) Register bzw. eine Distanzadresse (displacement).

0100 1110 1011 1010 wird so zu JSR (d16,PC). Da hier die PC-relative Adressierung mit Distanzadresse (displacement) zur Anwendung kommt, wird das folgende Wort als vorzeichenbehaftete relative Adresse (displacement) verwendet. Andere Kommandos wie MOVEQ #n,Dx sind sogar vollständig in 16 Bit kodiert.

Die Fähigkeit des 68000, bei fast allen Kommandos auch 32 Bit breite Adressen und Daten zu verstehen (die dann natürlich bei einem 16-Bit-Bus in mehreren Zyklen gelesen werden mussten), vereinfachte die Softwareentwicklung ungemein, da es sich quasi um eine 32-Bit-Architektur handelte.

Im Gegensatz z. B. zum Intel 8086 bereitet es keine Probleme, Datensätze über 64 KiB Größe zu adressieren. Wegen der 16-Bit-ALU und des 16-Bit-Datenbusses wird der 68000 oft 16-Bit-Prozessor genannt, er führt jedoch klaglos 32-Bit-Software aus. Wegen der 16-Bit-ALU kostet z. B. eine 32-Bit-Addition die doppelte Zeit. Der Schaltungsblock zur Generierung von Adressen hat jedoch volle 32 Bit, so dass z. B. das Durchsuchen eines Textes mit 8 Bit breiten Zeichen nicht langsamer ist, als es von einem reinen 16-Bitter zu erwarten wäre. Zudem kann der Text ohne Modifikation des Programms länger als 64 KiB sein. 68000-Software ist 32-Bit-Software.

Der Inhalt der oberen 8 Bit eines Adressregisters wird vom 68000 beim Speicherzugriff ignoriert. Dadurch ist es möglich, diese Bits frei zu nutzen, beispielsweise für Meta-Informationen zu einem Zeiger (pointer). Bei späteren Prozessorgenerationen aus der 68000-Familie mit 32 Bit externem Adressbus führt das offensichtlich zu Problemen. Da diese Art der Programmierung aber auf den frühen Macintosh-Rechnern sehr verbreitet war, hatten spätere Macintosh-Versionen mit 68020-Prozessor ohne Memory Management Unit (MMU) einen speziellen Baustein, genannt Address Management Unit (AMU), anstelle der MMU, der die oberen 8 Bit von Adressen optional ausmaskierte, um alte Software in einem 24-Bit-Kompatibilitätsmodus verwenden zu können. Als Prozessor mit Nanocode und Microcode ist der 68000 gewissermaßen auf Hardwareebene durch den Hersteller programmierbar. Das führte zu so interessanten Varianten wie dem 68000-360, der direkt auf dem Chip eine abgespeckte Fassung des IBM-System/360-Befehlssatzes ausführen konnte und für ein kleines 360-Modell von IBM benutzt wurde.

Das längste Kommando des 68k ist 22 Byte lang und ist ein MOVE-Kommando welches Daten von einer Speicherstelle in eine andere kopiert, wo beide Speicherstellen doppelt-indirekt mit 32 bit Displacements adressiert werden.

Varianten

Die erste Variante war der 68008, bei dem nur der Nanocode so verändert wurde, dass der Datenbus nur noch mit 8 Bit Breite angesprochen wurde. Eine weitere Variante war der 68010, der wesentlich besser mit virtuellem Speicher betrieben werden konnte und zudem noch einige Detailverbesserungen aufwies. Ein Ableger des 68010 war der nicht lange verfügbare 68012, der mehr Adressleitungen für größere Speicher (bis zu 2 GiB) zur Verfügung stellte. Später wurden Varianten meist direkt von der ursprünglichen CPU abgeleitet, wie z. B. der 68EC020 vom 68020 (24 statt 32 Adressleitungen) – oder der 68EC040 und der 68LC040 vom 68040 (es fehlten dann entweder die FPU oder die MMU). Ab dem 68020 wurden Schritt für Schritt auch erste 64-Bit-Befehle integriert (für einfache Multiplikationen).

Über drei binär kodierte Interruptleitungen können Interrupts mit sieben unterschiedlichen Prioritäten ausgelöst werden, davon ist die höchste nicht maskierbar. Zusammen mit entsprechenden Peripheriebausteinen sind bis zu 256 vektorisierte Interrupts möglich.

Ferner enthält der Prozessor Steuerleitungen, die signalisieren, ob als Nächstes ein Programmbefehl oder ein Datum geholt wird. Das ermöglicht zwar den Aufbau von Rechnern mit getrenntem Speicher für Programme und Daten; eine Harvard-Architektur ist aber nicht möglich, da die dazu notwendigen getrennten Busse für Programme und Daten hier nicht vorhanden sind.

Motorola MC68008 im PLCC-Gehäuse

Motorola MC68008 im PLCC-Gehäuse Motorola MC68008

Motorola MC68008

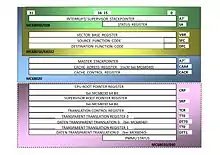

Register

Das Register-Programmier-Modell kann man in User- und Supervisor-Register einteilen gemäß den beiden Modi, welche die 68000-Familie aufweist. Diese User-/Supervisor-Modi bilden zusammen mit den Exceptions (Ausnahmebehandlungen) einen Schutzmechanismus und schützen das System vor Abstürzen. Angezeigt wird der Modus im S-Bit des Statusregisters SR. Im Supervisor-Modus darf man alle, im User-Modus nur bestimmte Ressourcen der CPU verwenden. Daraus erklärt sich auch die Verwendung des Programmier-Modells:

- User Register-Modell: wird vom Anwender-Programmierer bzw. von einem Compiler genutzt

- Supervisor Register-Modell: wird vom System-Programmierer (Betriebssystem) genutzt

In einem Echtzeit Multi-Tasksystem läuft üblicherweise der Betriebssystem-Kern im Supervisor-Modus und die Anwender-Tasks bzw. Programme im User-Modus. Dadurch ist der Kern von den Anwender-Tasks isoliert. Dieser Schutz kann beispielsweise durch den Einsatz einer MMU zusätzlich auf die Hardware ausgeweitet werden, da die CPU den Zustand des S-Bits im Statusregister SR auch hardwaremäßig nach außen gibt.

Verwendung

Bereits zu Beginn der 1980er Jahre fand die CPU, dank optionaler MMU, ihren Weg in die Unix-Welt. Sie wurde in hohen Stückzahlen in die Workstations von Apollo Computer (Apollo), HP (HP 9000-300) und Sun (Sun-1) oder auch von Digital Equipment Corporation (Vax 100) und SGI verbaut.

Mitte der 1980er Jahre folgten dann Personal- und Home-Computer, der erste war Lisa von Apple, die schon bald vom Macintosh (Mac) abgelöst wurde. Er wurde auch im Commodore Amiga, im Atari ST und Sinclair QL (68008) verbaut.

Ende der 1980er und Anfang der 1990er fand er sich dann in Spielkonsolen wie dem Sega Mega Drive oder dem Neo Geo. Auch in Schachcomputern (wie z. B. im Fidelity Mach IV als 68020 mit 20 MHz und Mephisto Amsterdam als 68000 mit 12 MHz) wurde der Prozessor verwendet.

In Taschenrechnern von Texas Instruments wie dem TI-89 (Titanium), TI-92 (Plus) und Voyage 200 findet er heute noch Anwendung. Im Airbus A320 steuert er den Elevator Aileron Computer (ELAC), der Teil des Flugsteuerungs-Systems ist.

Das Haupteinsatzgebiet des Prozessors waren und sind Steuerungsrechner in der Industrie, meist mit einem Echtzeitbetriebssystem wie OS-9 oder pSOS, Nucleus oder Linux68k, wobei Letzteres kein Echtzeitbetriebssystem im eigentlichen Sinne ist. Dieser Einsatz und die große Verbreitung waren nicht zuletzt dank der guten Interruptarchitektur und in Kombination mit dem VMEbus möglich. In hoher Stückzahl fand sich der Prozessor auch in Laserdruckern. Zusätzlich wurde er auf LAN-Karten (Schneider und Koch) und auf SCSI-Controllern (DPD), aber auch in Modems (Zyxel) verwendet. Auch die Automobilindustrie – vornehmlich (Motor-)Steuergeräte – bevorzugte bis zum Erscheinen des PowerPC den Einsatz der MC683xx-Controller-Familie.

Die Hochleistungsmodelle der 68000-Familie sind der 68040 und 68060 (bis 66 bzw. 75 MHz). Da Apple nach dem 68040 auf PowerPC-CPUs wechselte, wurde der 68060 nur noch in Erweiterungskarten für den Amiga und den Atari Falcon 030 (CT60) sowie für spezielle Anwendungen (z. B. in VMEbus-Rechnern, etwa von Motorola, sowie eingebetteten Systemen, wie in BMW-Modellen der 1990er Jahre oder hochleistungsfähigen Schachcomputern) verwendet.

Mittlerweile ist der Ur-68000 weitgehend verschwunden, wird aber noch in Wahlcomputern der Firma Nedap eingesetzt. Motorola fertigt eine Vielzahl von Mikrocontrollern, die vom 68000 abstammen. Die Motorola-Coldfire-Familie (auf 68k basierende Entwicklung) ist weiterhin im Bereich eingebetteter Systeme sehr beliebt und geht bis zum V5 mit 400 MHz; diese Variante findet in HP-Laserdruckern Verwendung. Die DragonBall-Ableger wurden in den Einsteigermodellen der Palm PDAs verwendet und sind in einfachen Handys verbreitet.

Ein prominentes Beispiel für ein Coldfire-basiertes (Amiga-inspiriertes) System war die Metabox-1000-SetTopBox, die allerdings nie auf den Markt gekommen ist.

Weitere Komponenten

Die Prozessoren 68020, 68030, 68040 und 68060 hatten bereits Funktionen integriert, die in anderen Prozessorarchitekturen erst erheblich später eingeführt wurden:

- interne Harvard-Architektur

- Branch Caches / Prediction

- Barrel-Shifter

- Pipelining / Prefetch

- User / Supervisor Mode (auch Protected Mode oder Kernel Mode genannt)

Andere wesentliche Errungenschaften beziehen sich auf die Embedded Controller (Single-Chip) der M68000-Familie, die M683xx-Familie. Dazu gehören z. B. der MC68332, MC68360, MC68376. Diese Typen waren wegweisend mit folgenden Funktionen:

- BDM (Background Debug Mode). Daraus ist der Industriestandard JTAG-Debugger entstanden, da der BDM die JTAG-Leitungen verwendete bzw. sich die Leitungen teilte. Unter der IEEE-ISTO 5001-2003 und unter dem Namen Nexus wurde diese zur Standard-Schnittstelle für Embedded Systeme. Sowohl die physikalische Schnittstelle als auch das Protokoll entspricht dem Motorola BDM.

- Dual Core, wobei die zweite CPU als intelligenter Peripheriecontroller eingesetzt wurde, z. B. beim

MC68332 als TPU – Time Processing Unit oder beim

MC68360 als CPM – Communication Processor Module bzw. QUICC (Quad Integrated Communication Controller). Dieser Controller erlaubte das Verarbeiten aller möglichen seriellen Protokolle. Es ist der Vorgänger des bekannten Power QUICC der Power-Architecture-Familie.

Literatur

- C. Vieillefond: Programmierung des 68000, Sybex Verlag, 1986, ISBN 3-88745-060-4

- Werner Hilf, Anton Nausch: M68000 Familie Teil 1 Grundlagen und Architektur, te-wi (1984), ISBN 3-921803-16-0

- Werner Hilf, Anton Nausch: M68000 Familie Teil 2 Anwendung und Bausteine, te-wi (1984), ISBN 3-921803-30-6

- Werner Hilf: M68000-Grundlagen Band 1, Architektur, Hardware, Befehlssatz, MC68020/30/40, MC68332, Franzis, München 1994, ISBN 3-7723-6333-4

- Werner Hilf: M68000 Anwendungen Band 2, Anwender- und Systemprogrammierung, Coprozessoren, Interfacetechnik, Software auf Diskette, MC68020/30/40, MC68332, Franzis, München 1994, ISBN 3-7723-6303-2

- Werner Hilf: Mikroprozessoren für 32-Bit-Systeme, Architektur, Hardware, Befehlssatz, Markt&Technik, ISBN 3-89090-922-1