Intel i960

Intel i960 (auch Intel 80960) ist ein RISC-basiertes Mikroprozessor-Design des Unternehmens Intel. Es war während der 1990er Jahre als Embedded-Mikrocontroller recht erfolgreich, einige Zeit sogar so sehr, dass es den AMD Am29000 von der Spitze dieses Marktes verdrängte. Trotz dieses Erfolges wurde der Vertrieb des i960 in den späten 1990er Jahren aufgrund eines Vertrages mit der Digital Equipment Corporation, welcher Intel erlaubte, das Design der StrongARM-CPU zu benutzen, eingestellt.

Intel i960 Prozessor im PGA-Gehäuse |

Intel N80960SA im PLCC-Gehäuse. |

Intel GC80960RD66 im BGA-Gehäuse. |

Intel GC80960RN, im BGA-Gehäuse |

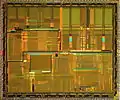

Die eines 80960HD |

Die eines 80960CA |

mylex 3-Kanal-Ultra-SCSI-Raid-Controller mit i960 (GC80960RD66) | |

Vorgeschichte

Das i960-Design kann man als Intels Weiterentwicklung des hauseigenen, zum Scheitern verurteilten iAPX-432-Designs der frühen 1980er Jahre sehen. Die Idee hinter dem iAPX 432 war direkte Unterstützung von „high-level“ Funktionen wie tagged- und protected-Memory oder Garbage-Collection in Hardware. Durch die Komplexität des Befehlssatzes, seine Multi-Chip-Implementierung und andere Designschwächen war der iAPX 432 sehr langsam im Vergleich zu anderen Prozessoren seiner Zeit.

Im Jahr 1984 starteten Intel und Siemens ein gemeinsames Projekt namens BiiN, um ein fehlertolerantes objektorientiertes High-End-Computersystem, das vollständig in Ada programmiert werden sollte, zu entwickeln. Viele der Mitglieder des i432-Teams arbeiteten auch an diesem Projekt. Der anvisierte Markt des BiiN-Systems waren Benutzer von hochverfügbaren Computersystemen wie Banken, Industrie und Kernkraftwerke.

Das Speicherschutzsystem des i432 beeinflusste das Design des BiiN-Systems.

Architektur

Um den Leistungsproblemen des i432 vorzubeugen, wurde der Prozessor im RISC-Design implementiert. Der Speicherbus war 33 Bit breit (ein 32-Bit-Datenwort und ein „Marker Bit“ für den Speicherschutz). In vielen Belangen folgte der i960 dem Berkeley-RISC-Design, beispielsweise in der Verwendung von Registerfenstern, einer implementierungsspezifischen Anzahl von Caches für die „per-subroutine“ Register für schnelle Routinenaufrufe. Anders als der i386, aber wie die meisten anderen 32-Bit-Designs, hatte der i960 einen 32-Bit-Adressraum ohne Speichersegmentierung. Von der i960-Architektur gab es auch eine superskalare Implementierung mit Instruktionen, die simultan auf mehrere Einheiten im Prozessor aufgeteilt wurden.

Sie werden meist in Netzwerkkomponenten, RAID-Systemen, Terminal-Computern oder bildgebenden Geräten wie Druckern eingesetzt. Ausgelegt sind sie auf die schnelle Aufnahme, Verarbeitung und Weitergabe von Daten.

Weblinks

- i960 Processors. www.intel.com, abgerufen am 12. Oktober 2011. (englisch)