NS320xx

Die NS320xx waren eine Familie von 32-Bit-Prozessoren von National Semiconductor, die sich durch einen umfangreichen Befehlssatz auszeichneten.

Entwicklung

Der erste vorgestellte Prozessor der Familie war der NS16032 (später in NS32016 umbenannt), dieser verfügte extern über einen 16 Bit breiten Datenbus und erschien etwa 1979 auf dem Markt. 1984 folgte der NS32032 mit einem komplett 32 Bit breiten Datenbus und erheblich gesteigerter Leistungsfähigkeit. Ebenfalls verfügbar war der NS32008, der mit einem auf 8 Bit reduzierten Datenbus als embedded Prozessor einen Platz im Markt finden sollte, aber wenig Erfolg hatte.

Mit den nachfolgenden NS32332 und NS32532 wurde die Leistungsfähigkeit weiter gesteigert. Der geplante NS32732 erreichte dann allerdings nie den Markt. Teile der Entwicklung für den NS32732 wurden dann für spezialisierte Prozessoren verwendet, die auf die Steuerung von Laserdruckern zugeschnitten waren. Mittlerweile ist die NS32000-Familie komplett eingestellt worden.

| Typ | Einführungsjahr | Taktfrequenzen | Gehäuse | Technologie | Beschreibung | |

|---|---|---|---|---|---|---|

| NS32008 | 6 MHz 8 MHz 10 MHz | DIP-48 | XMOS/CMOS |

| ||

| NS32016 | Ende 1970er | 6 MHz 8 MHz 10 MHz | DIP-48 |

| |

| NS32032 | 1984 | 6 MHz 8 MHz 10 MHz | CLCC-68 | XMOS/CMOS | |

| NS32132 | 6 MHz 8 MHz 10 MHz | LCC-68 | XMOS/CMOS |

| ||

| NS32332 | 1985 | 10 MHz 12 MHz 15 MHz | PGA-84 | XMOS/CMOS |

| |

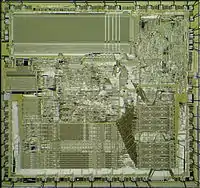

| NS32532 | 1987 | 20 MHz 25 MHz 30 MHz | PGA-175 | 1,25 µm CMOS |

|

| NS32081 | 6 MHz 8 MHz 10 MHz 15 MHz | DIP-24 |

| ||

| NS32381 | 15 MHz 20 MHz 25 MHz 30 MHz | PGA-68 PLCC-68 | CMOS |

|

Architektur und Befehlssatz

Bemerkenswert an den NS32xxx war die von Anfang an komplett auf 32 Bit abgestellte Architektur. Zwischen den verschiedenen Generationen der Prozessoren gab es nur minimale Unterschiede im Befehlssatz. Die zunächst als Coprozessoren realisierten Funktionen MMU und FPU wurden bei nachfolgenden Chipgenerationen in den Prozessor integriert, ohne dass dazu nennenswerte Anpassungen der Software nötig wurden.

Der Befehlssatz war sehr umfangreich, ebenso die Adressierungsarten. Vielfältige Kombinationen von Index- und Offsetregistern erlaubten den direkten Zugriff auf komplexe Datenstrukturen mit einem einzelnen Befehl. Alle Befehle konnten für jede ihrer Datenquell- oder -zieladressen jegliche Adressierungsart oder Register verwenden und viele Befehle konnten mit zwei Quell- und einer Zieladresse arbeiten. Vom Standpunkt der Symmetrie und Orthogonalität dürfte der Befehlssatz der NS320xx-Familie den Design-Höhepunkt dessen darstellen, was als CISC-CPU entworfen wurde.

Weblinks

- Datenbuch der NS32000-Familie (Stand 1986) (PDF-Datei; 85,50 MB)

- NS32532 (PDF-Datei; 1,10 MB)

- NS32C032 (PDF-Datei; 803 kB)

- NS32381 (PDF-Datei; 381 kB)