AMD K10

AMD K10 (auch bekannt als „AMD Next Generation Processor Technology“ oder „Stars“) ist der Codename einer Mikroarchitektur für Mikroprozessoren von AMD, die die K8- und K9-Generation ergänzt und mittelfristig ersetzt hat. Die K10-Mikroarchitektur basiert weiterhin auf der bereits seit längerem verwendeten AMD64-Mikroarchitektur.

Die K10-Mikroarchitektur wurde früher irrtümlich als AMD K8L bezeichnet, dies ist aber der Codename einer stromsparenden Variante der K8-Mikroarchitektur.[1][2]

Technisches

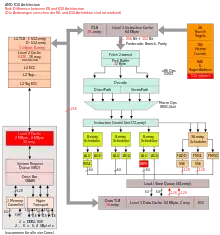

Die K10-Mikroarchitektur ist von Grund auf als Mehrkernprozessor konzipiert.

Auf einem Die wurden bei der Fertigung im 65-nm-Prozess bis zu vier Rechenkerne mit ihren dedizierten (d. h. fest zugeordneten) Caches, bis zu zwei Speichercontroller, die Crossbar und ein von allen Kernen gemeinsam genutzter, 2 MiB großer L3-Cache untergebracht.[1][2][3][4]

Mit der Umstellung der Fertigung auf 45 nm wurden inzwischen bis zu sechs Kerne realisiert und der L3-Cache ist auf bis zu 6 MB angewachsen. Gleichzeitig gibt es nun aber auch Modelle ohne L3-Cache.

45-nm-CPUs mit dem L3-Cache schneiden bei IPC (Instructions per Cycle) besser als ihre 65-nm-Vorfahren ab, während CPUs ohne L3-Cache im Durchschnitt eine kleinere IPC haben.

Im Vergleich zum K9 musste die Crossbar erweitert werden, um weitere Kerne ansprechen zu können.[4]

Die Speichercontroller mussten an die veränderte Cache-Hierarchie angepasst und optimiert werden.

Durch den gemeinsamen L3-Cache können die Kerne im Normalfall ohne Umweg über den relativ langsamen Hauptspeicher miteinander kommunizieren. Ein Umweg ist bei diesen Prozessoren nur dann nötig, wenn der gemeinsame Cache nicht ausreicht oder die Daten aus anderen Gründen bereits in den Hauptspeicher ausgelagert wurden.

Eine überarbeitete Gleitkommaeinheit[1][4] soll den Gleitkommadurchsatz stark erhöhen. Weiterhin sind erweiterte Stromspartechniken mit getrennten Versorgungsleitungen für die einzelnen Prozessorkerne und den Speichercontroller („split power planes“) sowie eine schnellere HyperTransport-Anbindung (Version 3.0)[1][2] auf neueren Mainboards verfügbar. Ausgereift sind die erweiterten Stromspartechniken allerdings erst bei den 45-nm-Modellen, die 65-nm-Modelle konnten im Idle im Vergleich zur K9-Generation nicht überzeugen.

Aufgrund der umfangreichen Änderungen an den Prozessorschnittstellen und der Spannungsversorgung wurden für die K10-Generation neue Prozessorsockel eingeführt. Für Mainboards mit einem Prozessor ist dies der Sockel AM2+, beziehungsweise der Sockel AM3 sofern man DDR3 als Arbeitsspeicher verwenden möchte und es sich um eine neuere 45-nm-CPU handelt. Allerdings besteht weiterhin die eingeschränkte Möglichkeit, die neue Generation mit reduziertem Funktions- und eventuell Leistungsumfang (z. B. höherer Stromverbrauch[4]) auch in den älteren Prozessorsockeln Sockel AM2 und Sockel F zu nutzen, sofern ein Bios-Update vom Mainboardhersteller bereitgestellt wurde.

Unterschiede zur K8-Architektur:

- Erweiterte Instruction Queue: Die Instruction Queue (Befehlswarteschlange) dient zum vorausschauenden Speichern der Befehle. Statt 16 Byte pro Taktzyklus sind nun 32 Byte pro Taktzyklus möglich.

- Verbesserung der Sprungvorhersage: Erweiterte Sprungvorhersage (Advanced Branch Prediction) mit nun 512 Einträgen und Verdopplung des Return Stacks.

- Sideband Stack Optimizer: Dieser ist neu hinzugekommen und führt Stack-Optimierungen bei POP/PUSH-Operationen durch.

- Verbesserung des TLB: Der Translation Lookaside Buffer (TLB) unterstützt jetzt 1 GiB große Pages. Ein Prozessorkern mit K10-Architektur adressiert den Speicher jetzt mit 48 Bit gegenüber 40 Bit beim K8. Der adressierbare Speicherbereich beträgt jetzt bis zu 256 TiB. Laut AMD soll sich dadurch die Arbeitsgeschwindigkeit bei großen Datenbanken und virtuellen Umgebungen erhöhen.

- Einführung von SSE4a beziehungsweise SSE128: Pro Taktzyklus und Kern ist das Einlesen von zwei 128-Bit-SSE-Befehlen möglich. Damit sind nun bis zu vier Gleitkomma-Operationen mit doppelter Genauigkeit pro Taktzyklus möglich. Bei der K8-Architektur ist der SSE-Pfad „nur“ 64 Bit breit. Außerdem existieren neue SSE4a-Befehle: EXTRQ, INSERTQ, MOVNTSD, MOVNTSS. Weiterhin werden die SSE-Befehle für Bitmanipulation erweitert: LZCNT, POPCNT.

- Unabhängiger Speicher-Controller: Durch einen unabhängigen Speicher-Controller sind mehr DRAM-Bänke möglich, es kommt zu weniger Page-Konflikten und es sind größere Burst-Längen möglich. Das Write Bursting soll mehrere Schreib- und Lesezugriffe auf den Speicher bündeln und in einem Durchgang ausführen. Dies soll den effektiven Speicherdurchsatz erhöhen. Im Gegensatz zum K8 und K9 kann der K10 die beiden Speicherkanäle wahlweise auch unabhängig ansteuern („unganged“ Modus). Somit kann die CPU gleichzeitig lesend und schreibend auf den Speicher zugreifen.

- L2-Cache: Die Datenanbindung zwischen Prozessorkern und L2-Cache wurde von 128 Bit auf 256 Bit erweitert.

- Shared L3-Cache: Alle Prozessorkerne können auf diesen gemeinsamen Cache zugreifen.

Namensgebung

Die Desktop-Prozessoren der K10-Generation (AMD Family 10h Processor) werden unter drei statt bisher zwei Markennamen vertrieben. Die Modelle mit einem L3-Cache werden unter dem neuen Produktnamen Phenom vermarktet, solche ohne L3-Cache als Athlon. Darüber hinaus basiert wie zuletzt schon beim AMD Athlon X2 das Bezeichnungssystem nicht mehr auf dem Quantispeed-Rating, sondern auf einer strukturierten Typennummer, ähnlich dem AMD Opteron.

Die erste Phenom-Serie mit vierstelligen Modellnummern wurde Ende November 2007 vorgestellt (damals noch unter dem Namen AMD Phenom ohne den Zusatz X4). Ende März 2008 folgten dann die Dreikernprozessoren mit dem Namen Phenom X3, im Oktober 2008 darauf basierende Athlon-Modelle.

Anfang 2009 wurde der AMD Phenom II und wenig später der AMD Athlon II vorgestellt. Diese tragen dreistellige Modellnummern und sind in einem moderneren Fertigungsprozess hergestellt, wodurch die Stromaufnahme deutlich sinkt und wesentlich höhere Taktraten möglich wurden.

Im Serverbereich wird der erfolgreiche Produktname AMD Opteron beibehalten, erste Produkte mit dem Vierkernprozessor „Barcelona“ wurden am 10. September 2007 auf den Markt gebracht.

Erste Prozessoren mit einem integrierten Grafikprozessor, sogenannte APUs (AMD Family 12h Processor), haben ebenfalls Prozessorkerne auf Basis der K10-Architektur. Diese CPUs/APUs werden unter dem Konzept AMD Fusion zusammengefasst, führen jedoch keine Marketingnamen in der Prozessorbezeichnung. Die APUs werden lediglich in Serien wie AMD A4-, A6-, A8- oder A10-Serie eingeteilt.

Prozessoren der K10-Mikroarchitektur

Folgende Prozessorfamilien von AMD basieren auf der K10-Mikroarchitektur:

- AMD Opteron (K10)

- AMD Phenom II

- AMD Phenom

- AMD Athlon II (nur die Ausführungen für Sockel AM2(+), AM3 und FM1)

- AMD Athlon X2 mit Kuma-Kern

- AMD Turion II

- AMD V-Serie

- AMD Sempron (nur die Ausführungen für Sockel AM3)

- AMD A8-, A6-, A4- oder E2-Serie, Codename Llano

Siehe auch

Weblinks

Einzelnachweise

- Simonnet Isaïe - Trouffman: Interview du Nouvel AMD. 28. Februar 2007, archiviert vom Original am 12. Juli 2009; abgerufen am 1. Januar 2014 (englisch, Video-Interview mit Giuseppe Amato (Technischer Direktor von AMD: Verkauf und Marketing EMEA) vom Februar 2007 (nicht mehr verfügbar)).

- AMD: Im Barcelona steckt K10. heise online, April 2007.

- AMD-Roadmap bis 2008, computerbase.de

- AMDs K10: Dreistufige Cache-Architektur des Barecelona-Cores vorgestellt. April 2007.