Translation Lookaside Buffer

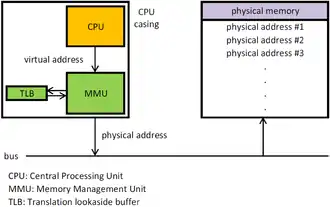

Der Begriff Übersetzungspuffer oder englisch Translation Lookaside Buffer (TLB, vgl. auch Cache) bezeichnet eine funktionale Einheit der Speicherverwaltung von selbst nachladenden Speicherverwaltungseinheiten (MMU).

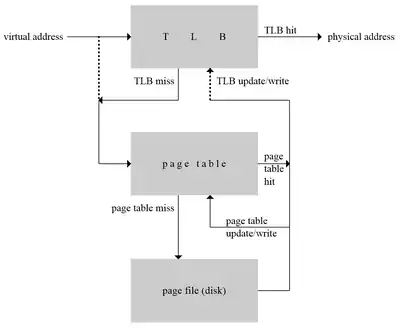

Wenn virtueller Speicher verwendet wird, muss zu den virtuellen Adressen die jeweils zugehörige physische Adresse ermittelt werden. Dabei wird die virtuelle oder logische Adresse beim x86 in meist drei Arbeitsschritten mit Hilfe der Segment- und der meist baumartig organisierten Seitentabelle zur physischen Adresse umgesetzt, andere Prozessoren (ARM, PowerPC, MIPS etc.) arbeiten ähnlich. Da diese Arbeitsschritte verhältnismäßig zeitintensiv sind, werden die zuletzt ermittelten Werte für die Adresse der physischen Speicherseite im TLB zwischengespeichert, wodurch erneute Zugriffe auf Adressen in dieser Seite nicht aufwändig neu ermittelt werden müssen, sondern aus dieser Liste entnommen werden können. Der TLB kann eine begrenzte Menge dieser Referenzen halten (üblicherweise nicht mehr als 1024 Einträge) und kann dadurch die Ausführung von Speicherzugriffen deutlich beschleunigen. Dies wird über assoziative Ordnungsregister realisiert, die parallele Zugriffe erlauben. Durch seinen Aufbau ist der TLB pro Eintrag vergleichsweise teuer gegenüber anderen flüchtigen Speichern wie z. B. RAM.

Einzelnachweise

- Andrew S. Tanenbaum: Moderne Betriebssysteme. 2., überarbeitete Auflage. Pearson Studium, 2003, ISBN 3-8273-7019-1.