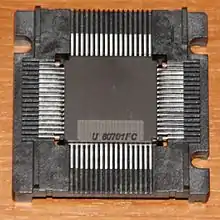

MME U80701

Der U80701 ist ein Nachbau des Mikroprozessors vom Typ MicroVAX 78032 der Digital Equipment Corporation (DEC), der mittels Reverse Engineering entwickelt wurde. Er war der erste in der Deutschen Demokratischen Republik (DDR) hergestellte 32-Bit-Prozessor und wurde entwickelt, um die damals führende Rechnerlinie von Digital Equipment Corporation, speziell der MicroVAX II, in der DDR verfügbar zu machen. Der zum U80700-Schaltkreissystem gehörende Prozessor wurde am 14. August 1989 offiziell vorgestellt. Das Entwicklerkollektiv des Schaltkreissystems wurde am 6. Oktober 1989 mit dem Nationalpreis der DDR I. Klasse für Wissenschaft und Technik ausgezeichnet.

Der Mikroprozessor sollte im Robotron-Arbeitsplatzrechner K 1820, einem Nachbau der MicroVAX II, verwendet werden.[1] Von diesem System wurden 10 Muster gebaut.[2] Auf der Leipziger Frühjahrsmesse 1990 wurde der Mikroprozessor in einer Vitrine des VEB Mikroelektronik „Karl-Marx“ Erfurt ausgestellt. Seitens der Sowjetunion lag Interesse an dem Schaltkreis wie auch am K 1820 vor.[3] Der Prozessor U80701 wurde nicht mehr in Serienproduktion gefertigt. Ab 1995 sollte ein Mikroprozessorsystem U80900 nach dem Vorbild CVAX 78034 für das Nachfolgemodell K 1830 (entsprechend MicroVAX III) das U80700-System ablösen.[4]

Architektur

Die CPU war in einem 68-poligen FlatPack-Plast- oder Keramikgehäuse untergebracht. Die integrierte Speicherverwaltungseinheit (MMU) konnte bis zu 16 MB physikalischen sowie bis zu 4 Gigabyte virtuellen Speicher adressieren und unterstützte einen 512 Byte seitenorientierten Schutzmechanismus sowie eine Verwaltung der Zugriffsrechte.[5]

Die Programmierung erfolgte über 175 Maschinenbefehle, 16 32-Bit-breite allgemeine sowie 20 Prozessor- beziehungsweise interne Register. Die CPU hatte einen 62,4 KB großen ROM mit integriertem 8-Byte-Prefetch-Stack. Das ROM enthielt ein Programm zur Ablaufsteuerung. Adress- und Datenbus belegten dieselben Pins, deswegen wurde hier das Multiplexverfahren verwendet. Des Weiteren war es möglich, die CPU durch eine zusätzliche Gleitkommaeinheit zu erweitern.

Zum U80700-Prozessorsystem gehörten folgende Schaltkreise:

- U80701: Hauptprozessor (CPU)

- U80702: Reed-Solomon-Generator (RSG)

- U80703: Gleitkommaprozessor (FPU)

- U80707: DIGITAL Link asynchronous receiver/transmitter (DLART)

- U80709: CPU-Interface-Gate-Array (CIGA)

- U80711: Bus-Interface-Gate-Array (BIGA)

Die einzelnen Bestandteile des U80700-Schaltkreissystems wurden unter Leitung des Kombinats Mikroelektronik Erfurt in arbeitsteiliger Zusammenarbeit mit den Kombinaten Robotron und Carl-Zeiss Jena (Zentrum Mikroelektronik Dresden) sowie dem Zentralinstitut für Kybernetik und Informationsprozesse Berlin der Akademie der Wissenschaften der DDR entwickelt. So wurde beispielsweise Robotron-Elektronik Dresden (Fachgebiet E9 und E5) mit der Entwicklung der U80702, U80703 und U80707 bis hin zu pflichtenheftgemäßen Mustern beauftragt.[6]

Daten

| Hersteller: | VEB Mikroelektronik „Karl Marx“ Erfurt |

| Bezeichnung: | U 80701 FC |

| Adressbus: | 32 Bit intern/extern |

| Datenbus: | 32 Bit intern/extern |

| Entwicklungsbeginn: | 1986 |

| nicht funktionierende Muster : | 1988 |

| erste funktionsfähige Muster: | 1989 |

| Technologie: | nSG (NMOS-Silizium-Gate-Technik) |

| Transistoranzahl: | zirka 130.000 |

| Chipfläche: | 85 mm² |

| Taktfrequenz: | effektiv 5 MHz (abgeleitet aus 40 MHz) |

| Verarbeitungsgeschwindigkeit K 1820: | 0,9 MIPS |

| MMU: | integriert |

| Gehäuse: | PLCC-68 laut Quelle #3, auch CQFP-68 bekannt (s. Fotos) |

| Bezeichnung | Ein-/Ausgang | Beschreibung |

|---|---|---|

| CLK1 | Eingang | Eingangstakt |

| CLK0 | Ausgang | Taktausgabe der Normalfrequenz |

| RESET# | Eingang | RESET der CPU |

| BM0..BM3 | Ausgänge | Byte-Maske |

| DAL0..DAL31 | Ein-/Ausgänge | gemultiplexter Daten-/Adressbus |

| AS# | Ausgang, Tristate | Adress strobe |

| DS# | Ausgang, Tristate | Data strobe |

| DBE# | Ausgang, Tristate | Data buffer enable |

| WR# | Ausgang, Tristate | Write |

| EPS# | Ausgang | External processor strobe |

| CS0, CS1 | Ausgänge, Tristate | Bus cycle status |

| CS2 | Ein-/Ausgang, Tristate | Bus cycle status |

| RDY# | Eingang | Ready |

| ERR# | Eingang | Error |

| DMR# | Eingang | DMA request |

| DMG# | Ausgang | DMA grant |

| HALT# | Eingang | Halt-Interrupt-Anforderung |

| INTTIM# | Eingang | Timer-Interrupt-Anforderung |

| PWRFL# | Eingang | Power-Fail-Interrupt-Anforderung |

| IRQ0#…IRQ3# | Eingänge | Interrupt-Anforderung für Standard-I/O-Interrupts |

| TEST | Eingang | Testeingang für Bauelemente-Hersteller |

| UCCX | – | Betriebsspannung zur Versorgung der Pinlogik des Daten-/Adressbusses |

| USSX | – | Bezugspotential für UCCX |

| UCCI | – | Betriebsspannung für Schaltkreislogik |

| USSI | – | Bezugspotential für UCCI |

| UBB | – | Bulkspannung, intern generiert |

Quellen

- Funkamateur. 38, H. 10, 1989, S. 473 (Bild #2).

- Klaus Krakat: DDR-Kombinat entwickelt die erste eigene 32-Bit-CPU. Computerwoche Nr. 41, 6. Oktober 1989.

- Mikroprozessortechnik, 11/1989, S. 322, Erster 32-Bit-Mikroprozessor aus Erfurt ermöglicht neue Rechnergeneration von Robotron

- Applikationszentrum Elektronik: Mikroelektronik Gesamtübersicht. (PDF; 1,1 MB) Info-Verlag electronic, Berlin 1990, S. 234–236.

- Autorenkollektiv: Technisches Handbuch ZVE KAC20. VEB Robotron-Elektronik Dresden, Dezember 1989.

Weblinks

- Bild von Prototypen U80701 und U80703 Bild von Ulrich Zander

- Vergleich Chip-Fotos vom DEC 78032 und U80701

- Sowjetisches, microVAX II-kompatibles Mainboard M10 mit U80701FC

- DEC's first single chip VAX microprocessor 78032 (DC333) at The Computer History Simulation Project

- Könau, St.: Feier für den falschen Chip. Mitteldeutsche Zeitung, 8. Januar 2010, Artikel zur Übergabe des U80701 an Erich Honecker

- Bilder aus dem Bundesarchiv zur Übergabe des U80701 an Erich Honecker

Einzelnachweise

- Pflichtenheft Arbeitsstation 32 bit K 1820 auf Basis Mikroprozessorfamilie MP 700. VVS d 063–247/89, VEB Robotron-Elektronik Dresden, März 1989, Sächsisches Hauptstaatsarchiv Dresden 11594-1361/1-2 (PDF-Datei 4,8 MB).

- Dieter Walter: Geschichte des VEB Robotron-Elektronik Dresden. Dresden 2006, S. 40–41. (PDF-Datei; 1,1 MB)

- W. E. Schlegel: Messebericht LFM 1990. In: radio fernsehen elektronik. Nr. 6, 1990, ISSN 1436-1574, S. 345.

- Autorenkollektiv: Konzeption zur Entwicklung der der Rechentechnik bis zum Jahre 2000. 1. Fassung. VVS d 063–430/89, VEB Kombinat Robotron, Dresden, 15. September 1989 (PDF-Datei 11,7 MB)

- Applikationszentrum Elektronik: Mikroelektronik Gesamtübersicht. (PDF; 1,1 MB) Info-Verlag electronic, Berlin 1990, S. 236.

- Pflichtenhefte U80702, U80703, U80707. VVS d 063–284/89, VVS d 063–267/89, VVS d 063–270/89, VEB Robotron-Elektronik Dresden, Februar 1989, Sächsisches Hauptstaatsarchiv Dresden 11594-1361/1-2