NMOS-Logik

Die NMOS-Logik (von englisch N-type metal-oxide-semiconductor) ist eine Halbleitertechnik, welche bei digitalen, integrierten Schaltungen Anwendung findet und zur Realisierung von Logikschaltungen dient. Als Besonderheit werden dabei ausschließlich so genannte n-Kanal-Metall-Oxid-Halbleiter-Feldeffekttransistoren (n-Kanal-MOSFET) verwendet.

Die NMOS-Logik wurde in den 1970er bis Ende der 1980er Jahre zur Realisierung von digitalen Logikschaltungen, wie sie beispielsweise in Mikroprozessoren vorkommen, verwendet. Sie findet heute, bis auf Nischenanwendungen, keine Anwendung mehr. Sie wurde fast vollständig durch die CMOS-Logik (geringere Verlustleistung) ersetzt.

Aufbau

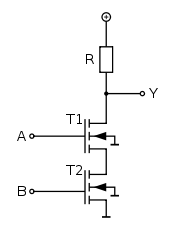

Ersatzschaltbild des NAND-Gatters mit Lastwiderstand |

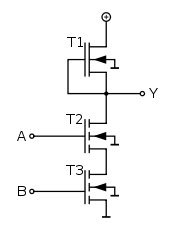

NAND-Gatter in NMOS mit selbstleitendem Lasttransistor T1 |

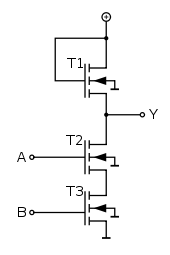

NAND-Gatter in NMOS mit selbstsperrendem Lasttransistor T1 |

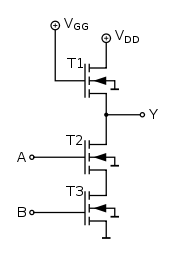

NAND-Gatter in NMOS mit selbstsperrendem Lasttransistor T1 mit UGG = Uth+UDD |

Der Aufbau der NMOS-Logik soll an einem einfachen NAND-Gatter verdeutlicht werden. Nebenstehend ist die Ersatzschaltung eines NAND-Gatters mit den beiden Eingängen A und B und dem Ausgang Y dargestellt. Der Lastwiderstand R hat den Nachteil, dass dieser auf integrierten Schaltkreisen (IC) sehr viel Raum benötigt. In der ersten Ausführungsform von NMOS wurde jener Lastwiderstand durch einen selbstsperrenden n-Kanal-FET ersetzt, womit in der Schaltung ausschließlich selbstsperrende n-Kanal-MOSFETs notwendig sind. Dies hatte den Vorteil, dass fertigungstechnisch weniger Prozessschritte bei der Herstellung des IC notwendig sind. Nachteilig sind die dafür notwendigen zwei Versorgungsspannungen.

Eine Verbesserung ergibt sich, wenn der obere Lasttransistor durch einen selbstleitenden n-Kanal-MOSFET ersetzt wird, wie in nebenstehender Abbildung dargestellt. Dies stellt auch das übliche Schaltprinzip von NMOS-Logikschaltungen dar. Damit kann mit nur einer Versorgungsspannung und geringeren Verlusten ausgekommen werden, nachteilig ist die kompliziertere Fertigung, da der selbstleitende Lasttransistor T1 mindestens einen Prozessschritt mehr und mehr Chipfläche als der Schalttransistor beansprucht.

Der Lasttransistor fungiert bei NMOS angenähert als Konstantstromquelle, so dass der Querstrom geringer als bei einem im Wert konstanten Lastwiderstand R ist. Wird der selbstleitende Lasttransistor T1 mit der niederohmigen Drain/Source-Diffusion realisiert, reichen für die Herstellung des NAND-Gatters vier Masken aus. Soll die Stufe hochohmig realisiert werden, werden mindestens fünf Masken benötigt.

Im Gegensatz zu der leichter zu fertigenden Vorläuferlogik, der PMOS-Logik welche nur mit p-Kanal-MOSFETs arbeitet, haben die eingesetzten n-Kanal-MOSFETs bei NMOS den Vorteil, dass als Ladungsträger innerhalb des Feldeffekttransistor nur negative Ladungsträger in Form von Elektronen auftreten. Elektronen haben im Halbleiter eine höhere Beweglichkeit als die bei den p-Kanal-MOSFETs am Ladungstransport beteiligten positiv geladenen Defektelektronen („Löcher“). Der Vorteil ist eine höhere Schaltfrequenz, welche mit NMOS-Gattern gegenüber vergleichbaren PMOS-Gattern erzielt werden kann.

Aufgrund der Fortschritte in den Herstellungsverfahren ist dieser Vorteil von NMOS allerdings nebensächlich geworden, und bei CMOS wird eine Kombination von selbstsperrenden p-Kanal- und n-Kanal-MOSFETs mit wesentlich geringeren Querströmen als bei NMOS eingesetzt. NMOS weist gegenüber CMOS folgende Nachteile auf:

- Der Flächenbedarf ist größer, es sei denn, es wird ein hoher Stromverbrauch akzeptiert.

- Ein NMOS-Gatter weist im statischen Betriebsfall bei logisch-0 am Ausgang einen vergleichsweise großen Querstrom auf.

Eine Erweiterung von NMOS, mit kleineren Strukturgrößen und höherer Packungsdichte, wird auch als HMOS bezeichnet.

Literatur

- Jerry C. Whitaker: Microelectronics. 2. Auflage. CRC Press, 2005, ISBN 0-8493-3391-1.

- M. Glesner et al.: Vorlesungsskriptum - VLSI Design of Integrated Circuits. Darmstadt University of Technology (pub.ro [PDF]).

- Christian Clemen: NMOS-Inverter. In: Vorlesungsskriptum: Grundlagen der Mikroelektronik (WS 2000/2001). Fachhochschule Augsburg, 2000 (PDF).