Streaming SIMD Extensions

Die Streaming SIMD Extensions (SSE), früher auch Internet SIMD Streaming Extensions (ISSE) ist eine von Intel entwickelte Befehlssatzerweiterung der x86-Architektur, die mit der Einführung des Pentium-III-(Katmai)-Prozessors 1999 vorgestellt wurde und deshalb anfangs den Namen Katmai New Instructions (KNI) trug. Zweck ist es, Programme durch Parallelisierung auf Instruktionslevel zu beschleunigen, genannt SIMD.

Konzept

Im Gegensatz zu der vorher veröffentlichten MMX-Befehlssatzerweiterung wurde SSE speziell für Gleitkommazahl-Datentypen entwickelt, außerdem wurden eigene und doppelt so breite 128-Bit-Register implementiert, beides häufig bemängelte Schwächen des MMX-Instruktionssatzes. Intel entschied sich auch dafür, den SSE-Instruktionssatz völlig neuzuentwickeln und nicht kompatibel zu dem bereits 1998 von Konkurrent AMD veröffentlichten 3DNow-Instruktionen zu machen, welche einen vergleichbaren Zweck erfüllten. Dieser Schritt war langfristig erfolgreich, SSE setzte sich gegenüber 3DNow durch und AMD unterstützte später ebenfalls nur noch SSE und ließ die 3DNow-Unterstützung auslaufen.[1]

Obwohl anfänglich im Namen (ISSE) ausdrücklich erwähnt, hat diese Technik direkt nichts mit dem Internet zu tun; vielmehr diente der Verweis der besseren Vermarktung (Intel warb bei Einführung des Pentium III u. a. damit, dass das Internetsurfen schneller bzw. generell aufregender werden würde). Nach kurzer Zeit ließ Intel das „I“ wegfallen, so dass man heute nur noch von SSE spricht.

SSE-Weiterentwicklung

Der seit geraumer Zeit existierende Wettkampf zwischen AMD und Intel über die Definitionshoheit bei der Weiterentwicklung der x86-Architektur führte seit ca. SSE3 zu inkompatiblen Erweiterungen von SSE.[2]

SSE2, SSE3, SSSE3, SSE4, SSE4a und SSE5 sind jüngere Erweiterungen bzw. Erweiterungsvorschläge von SSE sowohl von AMD als auch von Intel. Inzwischen existieren mit den Advanced Vector Extensions, XOP und CVT16 noch weitere Entwicklungszweige.

Technischer Aufbau

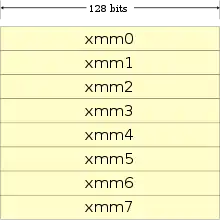

Die SSE-Befehlssatzerweiterung umfasste ursprünglich 70 Instruktionen und 8 neue Register (XMM0 bis XMM7), später wurden im Zuge der Weiterentwicklung sowohl Registeranzahl als auch Befehlsanzahl vergrößert.

Wie AMDs 3DNow-Erweiterungen ist auch SSE primär für Gleitkommaoperationen ausgelegt. Intel führte allerdings mit dem Pentium III neue 128 Bit breite Register ein, so dass mit SSE-Befehlen doppelt so viele Daten auf einmal parallel verarbeitet werden können, wie mit dem auf 64-Bit-Registern basierenden 3DNow. Das ging bei den damaligen Prozessoren jedoch nicht mit höherem Berechnungsdurchsatz einher, da die 128-Bit-SSE-Befehle intern in je zwei 64-Bit-SSE-Micro-Ops zerlegt wurden, weil die internen Ausführungseinheiten und ihre Datenpfade nur 64 Bit breit waren.[3]

Bei aktuellen 64-Bit-Prozessoren, wie etwa den auf der Core-Mikroarchitektur basierenden werden die 128 Bit breiten SSE-Register tatsächlich in einem Schritt verarbeitet. Auch wurde die Anzahl der SSE-Register auf 16 erhöht, wobei die neu eingeführten analog zu dem bisherigen Namensschema als XMM8 bis XMM15 bezeichnet werden.

Unterstützung in den CPUs

Da SSE eine der ersten SIMD-Erweiterungen der x86-Architektur war und bereits im Jahr 1999 auf den Markt kam, besitzen praktisch alle x86-CPUs seit etwa Mitte der 2000er Jahre SSE.

Beispielsweise unterstützte AMD ab dem Athlon einen Teil der im SSE-Befehlssatz enthaltenen Befehle (unter anderem diejenigen, welche mit 64-Bit-Registern arbeiten). Hier spricht man auch von einer Erweiterung von MMX. Seit dem Athlon-XP-Prozessor wird SSE vollständig unterstützt, in der Folge so weitgehend, dass sogar die eigene Erweiterung 3DNow aufgegeben wurde.

Nachfolgend eine Übersicht, ab welcher CPU-Familie die jeweiligen Hersteller SSE integriert haben:

- AMD: ab Athlon XP komplett, beim Athlon und Duron (seit Prozessorkern Morgan) nur teilweise

- Centaur Technology: beim C3 mit Prozessorkern Nehemiah

- Intel: ab Pentium III, beim Celeron mit Prozessorkern Coppermine

- Transmeta: ab Efficeon

Einzelnachweise

- 3DNow! Instructions are Being Deprecated (Memento des Originals vom 9. November 2013 im Internet Archive) Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis. (englisch)

- Agner Fog: Stop the instruction set war (englisch) agner.org. 5. Dezember 2009. Abgerufen am 12. Mai 2012.

- Jon Stokes: Into the Core: Intel's next-generation microarchitecture (englisch) arstechnica.com. 5. April 2006. Archiviert vom Original am 1. April 2007. Abgerufen am 12. Mai 2012.