Complementary metal-oxide-semiconductor

Complementary metal-oxide-semiconductor (engl.; „komplementärer / sich ergänzender Metall-Oxid-Halbleiter“), Abk. CMOS, ist eine Bezeichnung für Halbleiterbauelemente, bei denen sowohl p-Kanal- als auch n-Kanal-MOSFETs auf einem gemeinsamen Substrat verwendet werden.

Unter CMOS-Technik versteht man

- sowohl den verwendeten Halbleiterprozess, der zur Realisierung von integrierten digitalen wie analogen Schaltungen (ICs) verwendet wird,

- als auch eine Logikfamilie, die 4000er-Serie.

Auch viele nachfolgende Logikfamilien basieren auf der CMOS-Technik. Die Technik wurde 1963 von Frank Wanlass beim Halbleiterhersteller Fairchild Semiconductor entwickelt und auch patentiert.[1][2] CMOS-Prozesse sind heutzutage die meistgenutzten für die Herstellung von Logikfamilien-Bausteinen.

Technik

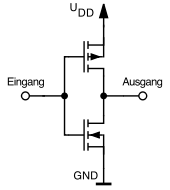

Das Grundprinzip der CMOS-Technik in der Digitaltechnik ist die Kombination von p-Kanal- und n-Kanal-Feldeffekttransistoren. Dabei wird die gewünschte Logikoperation zum einen in p-Kanal-Technik (als Pull-Up-Pfad) und zum anderen in n-Kanal-Technik (als Pull-Down-Pfad) entwickelt und in einem Schaltkreis zusammengeführt. Durch die gleiche Steuerspannung jeweils zweier komplementärer Transistoren (einmal n-Kanal, einmal p-Kanal) sperrt immer genau einer, und der andere ist leitend. Eine niedrige Spannung von ca. 0 V am Eingang (E) des Inverters entspricht dabei der logischen „0“. Sie sorgt dafür, dass nur die p-Kanal-Komponente Strom leitet und somit die Versorgungsspannung mit dem Ausgang (A) verbunden ist. Die logische „1“ entspricht einer höheren positiven Spannung (bei modernen Schaltkreisen > 1 V) und bewirkt, dass nur die n-Kanal-Komponente leitet und somit die Masse mit dem Ausgang verbunden ist.

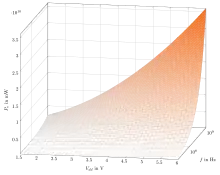

Im Vergleich zur NMOS-Logik muss zwar immer die doppelte Anzahl von Transistoren auf einen Chip aufgebracht werden, da der Arbeitswiderstand der NMOS-Realisierung in CMOS durch einen PMOS-Transistor ersetzt wird. Der PMOS-Transistor lässt sich aber leichter in ICs integrieren als ein Widerstand. Ein Widerstand produziert zudem unerwünschte Wärme, solange der Transistor leitend ist. Da auf Widerstände in der CMOS-Technik im Gegensatz zur NMOS-Technik verzichtet werden kann, entsteht ein Vorteil: Der Strom (von der Versorgungsspannung zur Masse) fließt nur im Umschaltmoment. (Bei der NMOS-Realisierung besteht das Problem, dass sich im leitenden Zustand „die starke Null“ (0) von unten gegenüber „der schwachen Eins“ (H) von oben durchsetzen muss (vgl. IEEE 1164) und dadurch fortlaufend ein Strom von oben fließt, solange der Transistor leitend bleibt.) Die Stromaufnahme bzw. die Verlustleistung ist also – abgesehen vom wesentlich kleineren Kriechstrom – nur von der Umschalthäufigkeit (Taktfrequenz) und dem Störabstand abhängig. Aus diesem Grund werden die meisten binären integrierten Schaltungen (Prozessoren, Arbeitsspeicher) zurzeit mit dieser Technik hergestellt. Die Verlustleistung ist darüber hinaus linear von der Taktfrequenz und quadratisch vom Störabstand abhängig (siehe Grafik).

Bei analogen Anwendungen werden die hohe Integrierbarkeit und die kapazitive Steuerung genutzt, die die MOSFETs ermöglichen. Durch das Einsparen der Widerstände und die Benutzung von aktiven Lasten (Stromspiegel als Quellen oder Senken) können Rauschabhängigkeiten und andere unerwünschte Effekte auf ein Minimum reduziert werden. Durch die große Frequenz-Bandbreite der Bauteile bei hohen Integrationen können sehr breitbandige Schaltkreise erstellt werden.

Eigenschaften

Die Verlustleistung im Ruhezustand beträgt üblicherweise ca. 10 nW, die Verlustleistung beim Schalten liegt frequenz- und betriebsspannungsabhängig je nach Bautyp bei Standardbaureihen bei ca. 1 mW/MHz (integrierte Gatter: ca. 10 µW/MHz).

Im Gegensatz zu Logikbausteinen der TTL-Familie, die nur mit 5 V arbeiten, liegt die typische Betriebsspannung zwischen 0,75 und 15 V.

CMOS-Eingänge sind empfindlich gegenüber statischen Aufladungen und Überspannungen, weshalb vor CMOS-Eingänge, wenn technisch möglich, ein- oder zweistufige Schutzschaltungen gesetzt werden. Zum Beispiel werden Dioden gegen die beiden Betriebsspannungen oder spezielle Schutzschaltungen wie GgNMOS vorgesehen. Weiterhin besteht bei CMOS-Schaltungen und bei Überspannungen an den Eingängen das Problem des sogenannten „Latch-Ups“.

Spezielle Arten

HC/HCT-CMOS

Unter HC-CMOS-Technik (H steht für High Speed) versteht man die Weiterentwicklung der CMOS-4000-Logikfamilie, um die Geschwindigkeit der LS-TTL-Familie zu erreichen. HC-Eingänge sind allerdings nicht voll kompatibel zu TTL-Ausgangspegeln. Daher wurde die HCT-CMOS-Technik entwickelt, bei der die CMOS-Transistorstruktur an die Ausgangsspannungspegel der TTL-Familie bei voller Pin-Kompatibilität zu diesen angepasst wurde.[3] Ein Mischen von TTL-Schaltkreisen mit HCT-CMOS-Schaltkreisen innerhalb einer Schaltung ist damit uneingeschränkt möglich.

BiCMOS

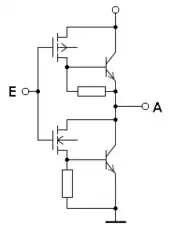

Unter der BiCMOS-Technik versteht man eine Schaltungstechnik, bei der Feldeffekttransistoren mit Bipolartransistoren kombiniert werden. Dabei werden sowohl der Eingang als auch die logische Verknüpfung in CMOS-Technik realisiert – mit den entsprechenden Vorteilen. Für die Ausgangsstufe werden aber Bipolartransistoren eingesetzt. Dies bringt eine hohe Stromtreiberfähigkeit mit sich und eine geringe Abhängigkeit von der kapazitiven Last. Dafür werden in Logikschaltkreisen üblicherweise zwei weitere Transistoren und zwei Widerstände in der Schaltung benötigt. Das Eingangsverhalten entspricht einem CMOS-Schaltkreis, das Ausgabeverhalten einem TTL-Schaltkreis.

Mit BiCMOS gelingt es weiterhin, Logikschaltungen mit leistungselektronischen Schaltungsteilen auf einem Chip zu vereinen. Beispiele sind Schaltregler, die direkt an der gleichgerichteten Netzspannung betrieben werden können.

Anwendungsgebiete

Die CMOS-Technik eignet sich durch ihren geringen Leistungsbedarf besonders für die Herstellung von integrierten Schaltungen. Diese finden Verwendung in allen Bereichen der Elektronik, zum Beispiel Digitaluhren oder in der Kfz-Elektronik. Außerdem werden mit ihr Speicherelemente, Mikroprozessoren und Sensoren (zum Beispiel Fotodetektoren in Form von CMOS-Sensoren für die Digitalfotografie oder Spektroskopie) gefertigt.

Auch bei analogen Anwendungen wird die CMOS-Technik eingesetzt. So sind CMOS-Operationsverstärker erhältlich, die sich durch einen extrem hohen Eingangswiderstand und geringe Versorgungsspannung auszeichnen.[4]

Siehe auch

Einzelnachweise

- Frank Wanlass, Chih-Tang Sah: Nanowatt logic using field-effect metal-oxide semiconductor triodes. In: 1963 IEEE International Solid-State Circuits Conference (February 20, 1963). Digest of Technical Papers. Vol. 6, 1963.

- Patent US3356858: Low stand-by power complementary field effect circuitry. Angemeldet am 18. Juni 1963, Erfinder: Frank M. Wanlass.

- An Introduction to and Comparison of 74HCT TTL Compatible CMOS Logic (Memento des Originals vom 24. September 2013 im Internet Archive) Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis. (PDF; 85 kB) Abgerufen am 5. März 2013

- László Palotas: Elektronik für Ingenieure. Vieweg+Teubner Verlag, 2003, ISBN 3-528-03915-9, S. 317 ff.