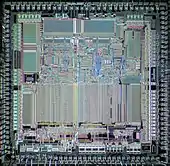

Motorola 68020

Der Motorola 68020 ist der erste echte 32-Bit-Mikroprozessor der Motorola 68000er-Familie. Er kam 1984 auf den Markt und besteht aus zirka 190.000 Transistoren.

Architektur

Im Gegensatz zum 68000er, der zwar wie eine 32-Bit-CPU programmiert werden kann, intern aber nur eine 16-Bit-ALU besitzt und die 32-Bit-Befehle aus mehreren 16-Bit-Schritten zusammensetzt, und auch nur über einen 16-Bit-Datenbus verfügt, besitzt der 68020 einen 32-Bit-Datenbus und eine 32-Bit-ALU, was ihm einen enormen Geschwindigkeitsvorteil gegenüber den älteren Vertretern der 68000er-Familie beschert.

Während der 68000er zur Multiplikation nur zwei 16-Bit-Datenworte zu einem 32-Bit-Datenwort multiplizieren kann, kann die ALU des 68020 auch zwei 32-Bit-Datenworte zu einem 64-Bit-Datenwort multiplizieren. Analoges gilt für die Division.

Da es im 68020 auch ein Koprozessor-Interface mit passender FPU (MC68881, später MC68882) und passender MMU (MC68851) gab, wurde der Befehlssatz um Gleitkomma-Befehle und MMU-Befehle erweitert. Für erstere wurden vorher als per Trap zu behandelnde Befehle des 68000er-Befehlssatzes verwendet, so dass man entsprechenden Code auch mit einer FPU-Emulation auf einem 68000 ausführen konnte (allerdings unter erheblich verringerter Ablaufgeschwindigkeit). Die CPU dekodierte die für FPU und MMU gedachten Befehle im Mikrocode und leitete diese dann an die entsprechenden Bausteine über die Koprozessor-Schnittstelle weiter. Um die Anzahl benötigter Leitungen gering zu halten, „lauschte“ die FPU am Datenbus und konnte diesen für Speicheroperationen auch direkt ansteuern, die MMU war in das Speicherinterface bei den Adressleitungen zwischen die CPU und den Speichercontroller geschaltet und modifizierte die von der CPU herausgegebenen Adressen (dadurch verlangsamten sich beim Einsatz der MMU die Speicherzugriffe, was erst durch die integrierte MMU des MC68030 verbessert wurde).

Zusätzlich zur Vergrößerung der ALU erhielt der 68020 aber auch eine aufwendigere Adressierungseinheit bzw. Adressgenerator, der ihm insbesondere für die damalige Zeit (Ende der 1980er Jahre) äußerst komplexe Adressierungsarten beschert.

So kann die effektive Adresse zum Lesen eines Datenworts aus dem Arbeitsspeicher wie folgt gebildet werden: Inhalt eines Registers addiert mit Konstante ergibt eine Adresse, an der ein Datenwort gelesen wird, zu dem eine weitere Konstante und ein wahlweise um 0, 1, 2 oder 3 Bits verschobenes Register addiert werden. Das Ergebnis ist die Adresse, an der dann tatsächlich gelesen wird. Syntax: [(bd, An.x), od, Rn.x*sc]

Solche Adressierungsarten erweisen sich insbesondere beim Verfolgen von Pointern auf Strukturen in Vektoren als äußerst nützlich.

Diese sehr komplexe Adressierungsarten mit Bezeichnungen wie „indirekt indizierte Adressierung“ stellten den Höhepunkt der Architektur von CISC-Prozessoren dar, gleichzeitig aber auch deren Wendepunkt: Diese Adressierungsarten benötigen sehr viel Mikrocode und Taktzyklen (es musste ja zunächst eine erste Adresse gebildet werden, die dann für einen Speicherzugriff auf die Basisadresse genutzt wurde, bevor dann der dort gelesene Wert um den ggf. bitverschobenen Wert des Indexregisters verändert werden konnte, um die für den Zugriff benötigte Adresse zu bilden), um ausgeführt zu werden. Gleichzeitig wurden sie von fast keinem Compilerhersteller rasch genug implementiert, um effektiv von Nutzen zu sein. Code, der diese Adressierungsarten nutzte, war auf älteren 68000er-Prozessoren nicht ausführbar und gleichzeitig sehr schwer zu debuggen (man hatte ja kein Register mehr, in das man hineinschauen und den tatsächlich für den Speicherzugriff verwendeten Adresswert überprüfen konnte). Entsprechend begannen fast zeitgleich Entwicklungen an RISC-Architekturen, die mit wesentlich weniger Befehlen und Adressierungsarten auskamen. Erst die Entwicklung von mehrschichtigen Cache-Systemen mit effektiver Verwaltung brachte Ende der 1990er Jahre die CISC-Prozessoren wieder in Vorteil gegenüber ihren Gegenspielern aus RISC-Familien.

Gegenüber dem Vorgänger MC68010 kam noch ein Level-1-Befehlscache von 256 Bytes dazu.

Beim MC68020 ist der Adressbus 32 Bit groß, so dass insgesamt 4 GiB Speicher adressiert werden können. Der MC68EC020 besitzt einen reduzierten Adressbus von 24 Bit, womit nur 16 MiB Speicher adressierbar sind.

Verwendung

Bekannte Computersysteme, in denen Motorola-68020-Prozessoren zum Einsatz kamen, sind der Apple Macintosh II, die Sun-Workstations der 3er-Serie, der Amiga 1200 und das Amiga CD³², letztere beide mit MC68EC020-Prozessor mit ca. 14 MHz, und die Steuerungs-Ausgleichsrechner des Eurofighter, ohne die dieser nicht stabil in der Luft gehalten werden könnte.

Nachfolger

Der Nachfolger des MC68020 ist der Motorola 68030. Die größte Änderung bestand darin, die MMU mit in den Chip aufzunehmen, so dass die Verzögerung beim Buszugriff durch die MMU entfiel. Der Nach-Nachfolger Motorola 68040 integrierte dann auch die FPU in den Hauptprozessor.

Weblinks

- Motorola MC68020 Product Summary Page

- Motorola 68020-Prozessoren: Bilder und Beschreibungen auf cpu-collection.de