VMEbus

Der VMEbus (Versa Module Eurocard-bus), auch VME-Bus oder VME-Bussystem genannt, ist ein Multi-User-Bussystem für die Steuerungstechnik, das 1981 ursprünglich für die Motorola-Prozessorfamilie 68000 entwickelt wurde. Gegenwärtig unterstützt der VMEbus nahezu alle Prozessoren, z. B. Intel x86, HP PA-RISC, Motorola 88000 und PowerPC. Er wurde von der IEC als ANSI/IEEE 1014–1987 standardisiert.

Die Ursprungsvariante verfügte über einen 16-Bit Datenbus und 24-Bit Adressbus, für die später diverse Erweiterungen entwickelt wurden. Mit der aktuellen VME64 Version stehen 64 Bit Busbreite zur Verfügung. Verwendet wird der VMEbus unter anderem in der Luft- und Raumfahrt, der Computer der ISS basiert z. B. auf dem VMEbus, wenngleich auch in anderer Bauform.

Der Bus ist ein Backplanebus (Rückwandbus ohne eigene elektronische Bauteile) für 19″-Einschubgehäuse.

Entworfen wurde der VMEbus von einem Konsortium um die Unternehmen Motorola und Philips. Unternehmen, die VMEbus-Bauteile entwickeln und vertreiben sind in der VITA (VMEbus International Trade Association) organisiert, Anwender haben sich ebenfalls in Organisationen zusammengeschlossen.

In Konkurrenz zum VMEbus hat das Unternehmen Intel einen vergleichbaren Bus auf der Basis der 80x86-Prozessoren unter der Bezeichnung Multibus II auf den Markt gebracht, der aber bei weitem nicht so erfolgreich wurde wie der VMEbus und seine Weiterentwicklungen.

Anschlüsse

Steckverbindungen

Die Platinen und Baugruppen (Einschübe) werden mit Steckverbindern nach DIN 41612 und IEC 603-2 auf dem VMEbus aufgesteckt. Diese haben 3 Reihen mit je 32 Kontakten, also 96 Kontakten je Steckverbinder. Je nach Ausbaustufe werden die Anschlüsse P1, P2 und P3 (neueste Erweiterung – nur im VXI-Bus) belegt.

Allgemeines zu den Anschlüssen

Auf dem Anschluss P1 sind die Bus- und Interruptsteuerung, die Datenbusleitungen D00 bis D15 und Adressbusleitungen A01 bis A23 untergebracht.

Der Anschluss P2 enthält in der mittleren Reihe (Reihe B) die Datenbusleitungen D16 bis D31 und die Adressbusleitungen A24 bis A31. Die Reihen A und C sind im VMEbus nicht definiert, diese sind unbelegt, vom Benutzer definiert belegt oder durch einen Subbus verwendet. Als Subbusse sind der VMX oder VSB definiert.

Der Anschluss P3 enthält die Erweiterungen des VXI-Busses.

Anschlussbelegung an P1

| ## | Reihe A | Reihe B | Reihe C |

|---|---|---|---|

| 01 | D00 | /BBSY | D08 |

| 02 | D01 | /BCLR | D09 |

| 03 | D02 | /ACFAIL | D10 |

| 04 | D03 | /BG0IN | D11 |

| 05 | D04 | /BG0OUT | D12 |

| 06 | D05 | /BG1IN | D13 |

| 07 | D06 | /BG1OUT | D14 |

| 08 | D07 | /BG2IN | D15 |

| 09 | GND | /BG2OUT | GND |

| 10 | SYSCLK | /BG3IN | /SYSFAIL |

| 11 | GND | /BG3OUT | /BERR |

| 12 | DS1 | /BR0 | /SYSRESET |

| 13 | DS0 | /BR1 | /LWORD |

| 14 | /WRITE | /BR2 | AM5 |

| 15 | GND | /BR3 | A23 |

| 16 | /DTACK | AM0 | A22 |

| 17 | GND | AM1 | A21 |

| 18 | /AS | AM2 | A20 |

| 19 | GND | AM3 | A19 |

| 20 | /IACK | GND | A18 |

| 21 | /IACKIN | SERCLK | A17 |

| 22 | /IACKOUT | SERDAT | A16 |

| 23 | AM4 | GND | A15 |

| 24 | A07 | /IRQ7 | A14 |

| 25 | A06 | /IRQ6 | A13 |

| 26 | A05 | /IRQ5 | A12 |

| 27 | A04 | /IRQ4 | A11 |

| 28 | A03 | /IRQ3 | A10 |

| 29 | A02 | /IRQ2 | A09 |

| 30 | A01 | /IRQ1 | A08 |

| 31 | −12V | +5V (Batt) | +12V |

| 32 | +5V | +5V | +5V |

Legende

| Befehl | Bezeichnung |

|---|---|

| D00 – D15 | Datenbusleitungen |

| A01 – A23 | Adressbusleitungen |

| AM0 – AM5 | Adressmodifizierer |

| /BR0 – BR3 | Busanforderungen |

| /BG0IN – /BG3IN | Busfreigaben (Eingang) |

| /BG0OUT – /BG3OUT | Busfreigaben (Ausgang) |

| /IRQ1 – /IRQ7 | Interrupt-Anforderungen |

| /IACK | Interrupt-Bestätigung |

| /IACKIN | Interrupt-Bestätigung (Eingang) |

| /IACKOUT | Interrupt-Bestätigung (Ausgang) |

| /ACFAIL | Störung im Netz (Spannung) |

| /BERR | Busfehler |

| /SYSFAIL | Systemfehler |

| /SYSRESET | Systemreset |

| SYSCLK | Systemtakt 16 MHz (nicht für Bussteuerung erforderlich) |

| /LWORD | Langwort-Übertragung |

| /BBSY | Bus belegt |

| /BCLR | Aufforderung zur Busfreigabe |

| /WRITE | Schreibzyklus |

| /DS0 – /DS1 | Datenbusselektion |

| SERCLK | Serieller Bus (Takt) |

| /SERDAT | Serieller Bus (Daten) |

| GND | Masse |

| +5V | Versorgungsspannung 5 Volt |

| +5V (Batt) | Versorgungsspannung 5 Volt aus Batterie |

| +12V | Versorgungsspannung 12 Volt |

| −12V | Versorgungsspannung −12 Volt |

Bussteuerleitungen

Die Bussteuerungsleitungen dienen zur Belegung und Freigabe im Datenbus. Hierzu gehören die Leitungen /BR0 bis /BR3, sie sind die Busanforderungen (Busrequest), sie sind L-aktiv. Jeder Einschub kann eine Busanforderung starten, in dem die entsprechende Leitung auf L gesetzt wird.

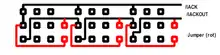

Die Leitungen /BG0OUT bis /BG3OUT sind die Busfreigaben (Bus Grant) als Ausgänge, /BG0IN bis /BG3IN analog dazu die Eingänge. Diese Leitungen sind so beschaltet, dass ein Ausgang /BGxOUT jeweils an den nächsten Einschub an den Eingang /BGxIN weitergeleitet wird. Diese Daisy-Chain-Beschaltung ermöglicht die Weitergabe der Freigabe an den nächsten Einschub. Nicht belegte Einschübe müssen mit Jumpern gebrückt werden, da die Weitergabekette sonst unterbrochen ist. Mit dieser Technik wird erreicht, dass die vier Busanforderungen von beliebig vielen Einschüben genutzt werden können, dies führt allerdings zu dem Nebeneffekt, dass Einschübe weiter links eine höhere Zuteilungswahrscheinlichkeit haben.

Wenn ein Einschub den Bus belegt, dann zeigt er es durch ein L auf der Leitung /BBSY (Bus Busy) an. Das Gegenstück dazu ist die Leitung /BCLR, die vom Arbiter angesteuert wird und mit einem L den Einschub auffordert, den Bus wieder freizugeben, die Übertragung zu beenden.

Mit der Leitung /DTACK (Data Acknowledge) wird mit L angezeigt, dass ein Datenbustransfer erfolgreich war. Mit einem L auf der Leitung /BERR wird das Fehlschlagen der Übertragung angezeigt.

Die Leitungen DS0 und DS1 legen zusammen mit LWORD und (in Grenzen) AD01 fest, welche Datengruppen eines 8-, 16- oder 32-Bit-Worts sich auf welchen Datenleitungen befinden. Diese etwas unübersichtliche Methode machte es möglich, Datengruppen auf unterschiedlichen Busbreiten und in unterschiedlichen Adressräumen zu übertragen.

Zusätzlich dienen die Leitungen AM0 bis AM6 der Zuordnung von Adressräumen und Übertragungsarten. Dabei wird zwischen 16-, 24- und 32-Bit Adressräumen, zwischen Block- und Byte/Wort-Übertragung, zwischen Daten- und Programmübertragung, mit oder ohne Privileg unterschieden.

Interruptleitungen

Die Interruptanforderungen erfolgen über die Leitungen IRQ1 bis IRQ7. Anders als bei der Arbitierung kann die Interruptsteuerung auch von anderen als dem ersten Einschub behandelt werden. Hierzu ist eine Leitung IACK (Interrupt Acknowledge) als Ausgang durchgeführt, die vor dem ersten Einschub zum IACKIN wird, die dann wie bei der Buszuweisung immer über IACKIN und IACKOUT weitergegeben wird. In der Zeichnung rot sind die Anschlüsse, die bei fehlendem Einschub durch einen Jumper überbrückt werden. Es sind nur 3 der 20 möglichen Einschübe eingezeichnet, die Reihe würde sich so immer fortsetzen. Es gibt nur einen solchen IACK-Kanal, die Nummer des Interrupts, der gerade behandelt wird, wird in den Adressbits A1 bis A3 übertragen.

Arbeitsweise

Interrupt- und Bussteuerung machen einen Arbiter erforderlich, der die Interrupt- und Bus-Anforderungen regelt. In der Regel ist der Arbiter im ersten Steckplatz angeordnet.

Interrupts

Der VMEbus hat sieben IRQ-Leitungen, die unterschiedliche Priorität haben. Jeder Interrupt kann aber von beliebig vielen Platinen genutzt werden, da der Interruptvektor nicht durch die IRQ-Leitung bestimmt wird, die anfordernde Platine gibt den Interruptvektor selbst an. Im Einzelnen erfolgt eine Interruptanforderung so, dass im ersten Schritt die anfordernde Einheit den Interrupt Request (einen von IRQ1 bis IRQ7) auf L setzt. Die Einheit, die für die Interruptbehandlung zuständig ist, holt sich mit höchster Priorität den Zugriff auf den Bus, falls sie diesen nicht ohnehin hat. Die Einheit sendet dann auf A01 bis A03 die Nummer des Interrupt Requests, der bearbeitet werden soll und ein L auf der Leitung /IACK. Das Signal wird dann über /IACKIN und /IACKOUT von links nach rechts von einem Einschub zum nächsten weitergeleitet, die erste Einheit, die diese Anforderungs gestellt hat, sendet auf dem Datenbus auf D00 bis D07 den eigentlichen Interruptvektor (00h bis FFh) zurück. Dieser Interruptvektor wird dann abgearbeitet.

Der große Vorteil dieses Verfahrens, das erst einmal unnötig kompliziert anmutet, liegt darin, dass sich viele Einheiten die IRQ-Leitungen teilen können, ohne dadurch Interrupt-Konflikte zu provozieren, so wie es im ISA-, VLB- und auch im PCI-Bus immer wieder passiert. Dabei ist zu beachten, dass der VMEbus historisch vor den eben genannten Bussystemen entwickelt und im Markt eingeführt wurde.

Bussteuerung

Der VMEbus ist ein Multimaster-Bus, das bedeutet, dass mehrere Busmaster den Bus belegen können. Auch hier wird wieder mit Prioritäten gearbeitet, es stehen vier BRQ-Leitungen zur Verfügung, die streng prioritär belegt sind oder im Round-Robin-Verfahren mit rotierenden Prioritäten arbeiten. Mit letzterem wird ein Fairness-Verfahren betrieben, länger wartende Einheiten werden bevorzugt. Üblicher ist aber das reine prioritäre Verfahren.

Der Arbiter zur Buszuteilung sitzt in der Regel auf der ersten Einschubposition, weil es keine gemeinsame BGx-Leitung gibt. Ein Arbiter, der an anderer Stelle sitzt kann nur noch die Einheiten steuern, die rechts von ihm eingebaut sind. Damit wären die Steckplätze links davon verloren.

VMSbus und VMXbus

Der VMXBus (VME Extended bus) spezifiziert die Anbindung eines Speichers. Der Datenpfad zu diesem ist 32 Bit breit, eine Adresse umfasst 24 Bit, die im Multiplex als zwei 12 Bit breite Worte übertragen wird. Ein Flachbandkabel realisiert die Verbindung zwischen zwei Karten.

Über den VMSbus (VME Serial bus) werden Nachrichten mit 200 bis 400 MByte/s übermittelt.[1]

Anwendungen

Weblinks

- VITA (englisch)

- Virtuelles Unternehmensmuseum (u. a. VMEbus-Maschinen gewidmet)

Einzelnachweise

- Thomas Flik: Mikroprozessortechnik. 2001, ISBN 3-540-42042-8