GgNMOS

Unter der Bezeichnung ggNMOS, für englisch gate-ground-NMOS oder auch englisch grounded gate NMOS, wird in der Mikroelektronik eine übliche Schutzschaltung verstanden, welche die schädlichen Auswirkungen von äußeren elektrostatischen Entladungen (ESD) in integrierten Schaltungen (IC) limitiert.[1][2] Die Bezeichnung leitet sich von dem als Schutzelement eingesetzten N-Kanal Metall-Oxid-Halbleiter-Feldeffekttransistor (N-MOSFET, NMOS) ab, der direkt am Die an jeden extern zugänglichen Anschlusspin vorgesehen wird. Die bei ESD auftretende hohe elektrische Spannung wird dabei durch den ggNMOS gegen das Bezugspotential abgeleitet und so unschädlich macht. Ohne Schutzelement würde es durch die Entladung zu irreversiblen Schäden und Zerstörungen im Inneren der integrierten Schaltungen kommen.

Aufbau

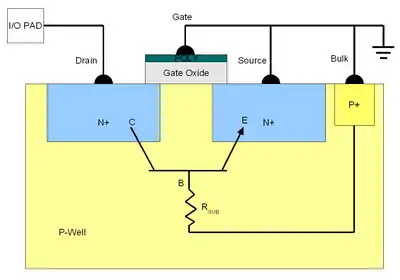

Der N-MOSFET ist in dieser Schaltung, wie in nebenstehender vereinfachter Schnittdarstellung dargestellt, so geschaltet, dass sein Source- und Gate-Anschluss mit Massepontial verbunden sind. Der Drain-Anschluss wird mit dem zu schützten Anschlusspin der integrierten Schaltung verbunden. Da sich Gate und Source auf gleichen Massepotential befinden, ist der ggNMOS im Normalbetrieb gesperrt, der unter dem Gateoxyd liegenden N-Kanal ist hochohmig und hat damit keinen Einfluss auf die integrierte Schaltung und deren Funktion.

Zusätzlich zu den namensgebenden N-MOSFET bildet sich durch den Aufbau der Dotierungsbereiche, n- und p-dotierte Bereiche im Halbleiter, im p-Substrat des Halbleiters ein parasitärer Bipolartransistor (NPN). Der Basisanschluss (B) ist mit dem p-Substrat des Halbleiters verbunden, der Kollektor-Anschluss mit dem Drain-Anschluss und der Emitter mit dem Source-Anschluss. Kommt es zu einem ESD mit entsprechend hoher Spannung kommt es in Folge an dem Bipolartransistor in der Kollektor-Basis-Strecke zu einem reversiblen Lawinendurchbruch. Dieser Strom durch die Basis bewirkt am parasitären Basiswiderstand, in der Skizze mit RSUB markiert und primär gebildet durch den Widerstand im p-Halbleitersubstrat, einen Spannungsabfall, welcher den Bipolartransistor in der Strecke Kollektor-Emitter öffnet und die elektrostatische Ladung gegen das Bezugspotential ableitet.[1] Diese Schutzfunktion ist auch im spannungslosen Zustand der integrierten Schaltung, beispielsweise bei der Lagerung oder Bestückung, gegeben.

Die eigentliche Schutzfunktion ergibt sich beim ggNMOS damit nicht direkt durch den bei der Produktion mit Standardfertigungsverfahren im Halbleitersubstrat hergestellten N-Kanal MOSFET, sondern es wird durch den Aufbau der MOSFET-Struktur im Halbleiterkristall zusätzlich ein parasitärer Bipolartransistor realisiert, welcher das eigentliche Schutzelement darstellt. Bei größeren integrierten Schaltungen mit einigen 100 Anschlusspins nehmen dieses Schutzelemente einen wesentlichen Teil der Chipfläche ein: Denn es ist dabei für jeden Anschlusspin ein eigener ggNMOS am Halbleiterchip mit einer Strukturgröße von ca. 800 µm vorzusehen.[1] Die Größe ergibt sich aus dem Umstand, dass im Rahmen der üblichen ESD-Simulationsmodelle durch die Entladung der ggNMOS nicht dauerhaft zerstört werden darf.

Einzelnachweise

- Oleg Semenov, Hossein Sarbishaei, Manoj Sachdev: ESD Protection Device and Circuit Design for Advanced CMOS Technologies. Springer Science & Business Media, 2008, ISBN 978-1-4020-8301-3, Kapitel 5.2.2: MOSFET-Based ESD Clamps, S. 122 ff.

- Yong-Seo Koo, Kwangsoo Kim, Shihong Park, Kwidong Kim, and Jong-Kee Kwon: Design of Gate-Ground-NMOS-Based ESD Protection Circuits with Low Trigger Voltage, Low Leakage Current, and Fast Turn-On. Band 31, Nr. 6. ETRI Journal, Dezember 2009, doi:10.4218/etrij.09.1209.0045 (Online). Online (Memento des Originals vom 21. September 2017 im Internet Archive) Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis.