Terascale-Prozessor

Der Terascale-Prozessor von Intel war ein Forschungsprojekt, um einen Mikroprozessor mit hunderten Kernen zu entwickeln. Eine derartige Architektur wird – analog zu den Multicore-Architekturen – als „Manycore“ bezeichnet.

Der Terascale-Prozessor wurde in Kacheln – den sogenannten Tiles – organisiert, wobei die meisten Kacheln allgemeine Rechenaufgaben wahrnahmen. Der Terascale-Prozessor besaß etwa 100 Millionen Transistoren, wobei jede Kachel etwa 1,2 Millionen Transistoren beherbergte. Er wurde im Jahr 2007 vorgestellt.

Aufbau der Kacheln

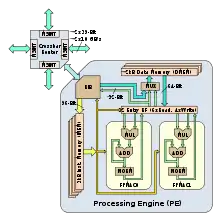

Die Kacheln besaßen je eine Processing Engine (PE) und einen Crossbar Switch. Die Processing Engine übernahm die Rechenaufgaben mit Hilfe zweier FMAC-Einheiten und einer Gleitkommaeinheit. Zudem besaß die Processing Engine 5 kB an lokalem Speicher. Der Crossbar Switch diente zur Kommunikation mit den Nachbar-Tiles.

Prinzipschaltbild der Processing Engine |

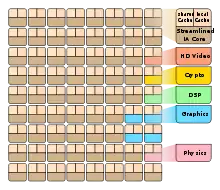

Spezialisierte Kacheln im Terascale |

Einige zusätzliche Kacheln waren auf spezielle Aufgaben wie die Verarbeitung von High Definition Video, Verschlüsselung, Digitale Signalverarbeitung, Physikbeschleunigung oder 3D-Computergrafik optimiert. Diese spezialisierten Kacheln arbeiteten im jeweiligen Aufgabenbereich effizienter – also schneller und energiesparender – als nichtspezialisierte Kacheln.[1]

Speicheraufbau

Ein Problem, das sich beim Terascale stellte, war, dass durch die hohe Anzahl von Kernen die Anbindung an den Speicher sehr schwer wurde, da einerseits die Datenanbindung geteilt und andererseits der Zugriff auf den Speicher koordiniert werden musste. Intel verwendete zu diesem Zweck einen hierarchischen Cachespeicher. Dabei bekam jeder Kern einen eigenen 16 kB bis 64 kB großen L1-Cache. Der 256 kB bis 1 MB große L2-Cache wurde von einer kleinen Gruppe von Kernen geteilt. Der L3-Cache stand allen Kern-Gruppen innerhalb des Prozessors zur Verfügung.

Zusätzlich kam im Terascale ein L4-Cache aus DRAM-Speicher zum Einsatz, der sich jedoch nicht auf demselben Prozessor-Die befand, sondern auf einem eigenen Die gefertigt wurde.

Der L4-Cache wurde anschließend in MCP-Bauweise neben oder in Stacked-Bauweise auf dem Prozessor angebracht. Zusätzlich wurden die Programme mit einer QoS-Priorisierung versehen, damit der Speicher für wichtige Anwendungen reserviert werden konnte. Wie viel Speicher eine Anwendung beanspruchen konnte, wurde dynamisch von einem Resource-Monitor bestimmt, wodurch das Betriebssystem die Anwendungen in die optimalen Cache-Einheiten verschieben konnte.

Geschwindigkeit

Der Terascale-Prozessor erreichte mit mehr als einem Teraflop je Sekunde eine Geschwindigkeit, die mit dem ASCI-Red-Supercomputer von 1996 vergleichbar ist, der aus 10.000 Pentium-Pro-Prozessoren mit 200 MHz Taktfrequenz und insgesamt 500 kW elektrischer Leistungsaufnahme aufgebaut war.

| Taktfrequenz in Gigahertz |

Kernspannung in Volt |

Leistungsaufnahme in Watt |

Datendurchsatz in Terabit/s |

Rechenleistung in Teraflops |

|---|---|---|---|---|

| 3,16 | 0,95 | 62 | 1,62 | 1,01 |

| 5,1 | 1,2 | 175 | 2,61 | 1,63 |

| 5,7 | 1,35 | 265 | 2,92 | 1,81 |

Siehe auch

Einzelnachweise

- J. Held, J. Bautista, S. Koehl (Hrsg.): From a Few Cores to Many: A Tera-scale Computing Research Overview. White Paper Research at Intel. Intel 2006 (PDF (Memento vom 19. November 2011 im Internet Archive)).