IA-32

Als IA-32, eine Abkürzung für „Intel Architecture 32-Bit,“ bezeichnet Intel die Architektur des x86-Prozessors ab dem 80386, ursprünglich als 32-Bit-Architektur. Mit der Befehlssatzerweiterung x64 ist jedoch auch die 64-Bit-x86-Architektur inkludiert.

x86 ist die generelle Bezeichnung für die Prozessorarchitektur, die mit dem 8086-Prozessor von Intel 1978 als 16-Bit-Architektur begründet wurde. Mit dem 80386 wurde 1985 von Intel eine Erweiterung des Befehlssatzes auf 32-Bit eingeführt, weshalb für 80386-kompatible Mikroprozessoren auch oft die Bezeichnung i386 verwendet wird bzw. retronym IA-32. Ab 1999 wurde von AMD an der Erweiterung des Befehlssatzes auf 64-Bit gearbeitet, anfangs unter der Bezeichnung x86-64, die 2003 als AMD64 und 2005 von Intel als Intel 64 eingeführt wurde. Auch diese nunmehr oft als x64 bezeichnete Erweiterung des Befehlssatzes zählt zur „Intel Architecture 32-Bit.“

Die x86-Befehlssatzarchitektur wird von Intel und AMD weiterentwickelt.

Itanium

Mit der Neuentwicklung des Itanium-Prozessors von Intel und Hewlett-Packard, die 2001 auf den Markt kam, wollte Intel die zu x86 bzw. IA-32 inkompatible Itanium-Architektur einführen. Diese wurde von Intel auch „Intel Architecture 64-Bit“ bezeichnet, da Intel die neue Architektur als die Nachfolge für die damals 32-Bit-x86-Architektur ansah. IA-64 (Itanium) setzte sich jedoch nicht durch, auch deshalb nicht, weil die Architektur als Neuentwicklung nicht x86-kompatibel ist und somit nicht zur IA-32-Architektur mit i386-Befehlssatz zählt, die durch viele Hersteller implementiert wurde.

Da x86 seit den 1980er Jahren die weltweit am weitesten verbreitete Prozessorarchitektur für Personal Computer war, gab es eine Vielzahl an bestehenden Programmen, die für den Itanium-Prozessor neu programmiert werden mussten – oder: hätten programmiert werden müssen.

Als AMD 2003 die 64-Bit-Erweiterung AMD64 für die bestehende x86-Architektur (IA-32) einführte, wurde diese auf Anhieb vom Markt erfolgreich angenommen, unter anderem gerade deswegen, weil bestehende x86-Programme unverändert darauf liefen. Intel musste 2005 notgedrungen nachziehen und implementierte mit Intel 64 eine zu AMD64 kompatible 64-Bit-Erweiterung für die x86-Architektur „IA-32,“ was die „Intel Architecture 32-Bit“ zu einer 64-Bit-Architektur macht. Um Verwirrung zu vermeiden wird 64-Bit-x86 auch mit x64 (in Anlehnung an x86) bezeichnet.

IA-64 hingegen steht für die Itanium-Architektur, die zwar auch eine 64-Bit-Architektur ist, die aber nicht zum x86-Befehlssatz „IA-32“ (80x86, i386, x64) kompatibel ist.

Architekturmerkmale

Die IA-32-Architektur ist eine Weiterentwicklung der 16-Bit-Architekturen von Intels 8086- und 80286-Prozessoren. Alle Register, einschließlich der Adressregister, wurden in dieser Architektur auf 32 Bits erweitert. Die Anzahl der Register blieb gleich. Die Mnemonic der erweiterten Register wurden mit einem vorangestellten E, für extended (deutsch: erweitert), gekennzeichnet, beispielsweise EAX (32-Bit) von zuvor AX (16-Bit). Um Abwärtskompatibilität zu erzielen wurden die 32-Bit-Register als Erweiterung der 16-Bit-Register der 80286-Architektur realisiert, sodass unter der Bezeichnungen für die 16-Bit-Register auf die unteren 16-Bit der 32-Bit-Register weiterhin zugegriffen werden kann: beispielsweise liefert AX auf die unteren 16-Bit des 32-Bit-EAX-Registers.

Der Adressbus ist 32 Bits breit und demzufolge ist die Adressierbarkeit auf 4 GB (physikalischer Adressraum) begrenzt. Ausnahmen sind der 80386SX, welcher nur einen 24-Bit-Adressbus besaß. Ab dem Pentium Pro wurde mittels PAE eine Adresserweiterung auf 36 Bits erzielt, bei späteren Generationen sogar mehr, z. B. 40 Bits beim AMD K8. Mit 36 Bits lassen sich 64 GiB adressieren, sodass unter einer 32-Bit-Umgebung mit Einschränkungen mehr als 4 GiB genutzt werden können, wenn vom Betriebssystem PAE umgesetzt wird. Beispielsweise nutzt Linux die PAE-Erweiterung automatisch, wenn diese vom Prozessor unterstützt wird – bei neueren Distributionen ist PAE sogar Voraussetzung, da sich damit auch das NX-Bit nutzen lässt. Unter 32-Bit-Versionen von Windows von Microsoft hingegen wurde PAE wegen Kompatibilitätsproblemen mit bestehenden Treibern nicht genutzt, sodass 32-Bit-Windows-NT auf 4 GiB Arbeitsspeicher beschränkt ist.

Mit der 64-Bit-Befehlssatzerweiterung x64 wurde IA-32 zu einer 64-Bit-Architektur weiterentwickelt, wobei auch die Anzahl der Register verdoppelt wurde. Im neuen Betriebsmodus sind sowohl 32-Bit- als auch 64-Bit-Submodi vorhanden, sodass auch 32-Bit-Software von der doppelten Anzahl an Registern profitieren kann (x32).

Nomenklatur

| Architektur | übliche Bezeichnungen |

|---|---|

| 32-Bit-x86-Architektur des 80386. | i386 – i686, IA-32 (od. IA32), x86-32 |

| 64-Bit-x86-Architektur des Opteron. | x86-64, amd64 (od. AMD64), x64 |

„Intel Architecture 32-Bit“ bzw. abgekürzt „IA-32“ bezeichnete ursprünglich nur die 32-Bit-x86-Architektur des 80386 und seiner Nachfolger, denn damals waren diese allesamt 32-Bit-Prozessoren. Problematisch wird die von Intel gewählte Bezeichnung erst mit der 64-Bit-Erweiterung x64 – denn diese zählt als Weiterentwicklung und Erweiterung zu IA-32, zu der x64 voll kompatibel ist. Retronym finden sich zur genaueren Unterscheidung daher auch die Bezeichnungen x86-32 für die 32-Bit- und x86-64 für die 64-Bit-x86-Architektur.

Die von Intel und HP entwickelte Itanium-Architektur, auch mit „Intel Architecture 64-Bit“ bzw. abgekürzt „IA-64“ bezeichnet, ist keine x86-Architektur. Es besteht jedoch die Gefahr der Verwechslung mit „x64“, der 64-Bit-x86-Architektur, die eine Erweiterung von IA-32 ist.

Zur Unterscheidung findet sich dennoch oft IA-32 (auch als „IA32“ oder „ia32“) für die 32-Bit-x86-Architektur bzw. x64 (oder amd64, „x86-64“ oder „x86_64“) für die 64-Bit-x86-Architektur. Beispiele dafür sind u. a. diverse Betriebssysteme, so unterscheidet etwa Slackware zwischen „ia32“ (32-Bit-x86) und „x64_64“ (64-Bit-x86),[1] oder auch UEFI-Bootloader auf Wechseldatenträgern (32-Bit-EFI auf x86: \EFI\Boot\BootIA32.efi, 64-Bit-EFI auf x86: \EFI\Boot\Bootx64.efi).

Betriebsarten

Neben dem Real Mode, in dem kompatibel zum 16-Bit-Intel-8086 der konventionelle Arbeitsspeicher und der obere Speicherbereich, das ist der erste, untere Megabyte des Arbeitsspeichers, ohne Beschränkung über Offset und Segment angesprochen werden kann, kennt die Intel Architecture 32-Bit zwei bzw. drei weitere Betriebsarten:

- Protected Mode, der bis zu 4 GB Speicher durchgängig (linear) adressieren kann und einen hardwareseitigen Speicherschutz garantiert (über die Virtuelle Speicherverwaltung der MMU), was Multitasking-/Multiuser-Betriebssysteme mit präemptivem Multitasking ermöglicht.

- System Management Mode (SMM), welcher für die Leistungsreduktion und Hersteller-spezifische Eigenschaften eingesetzt wird. Der SMM läuft in einem separaten Arbeitsspeicher ab, sodass laufende Prozesse und Betriebssysteme nicht beeinflusst werden.

- Bei 64-Bit-x86-Prozessoren kommt zusätzlich der Long Mode (AMD) bzw. der IA32e Mode (Intel) hinzu, der die zwei Submodi 64-Bit Mode und Compatibility Mode bereitstellt. (Siehe x64#Betriebsmodi.)

Als Option des Protected Mode (32-Bit) existiert außerdem der Virtual 8086 Mode, der ein oder mehrere Real-Mode-Programme ausführen kann – dies wurde zur Ausführung von MS-DOS-kompatiblen Programmen unter 32-Bit-Betriebssystemen benötigt und war wichtig für eine schonende Migration von DOS zu moderneren Betriebssystemen. Seit der Umstellung auf 64-Bit spielt der Virtual 8086 Mode keine sehr große Rolle mehr, da MS-DOS-kompatible Programme nur noch relativ wenig genutzt werden oder aber auf 64-Bit-Betriebssystemen ohnehin vollständig emuliert werden (müssen).

Protected Mode: Virtuelle Speicherverwaltung und Speicherschutz

Virtuelle Speicherverwaltung

Die neue Virtuelle Speicherverwaltung ist primär für den Multitasking-Betrieb ausgelegt (Protected Mode). Mittels Memory Management Unit (MMU) können mehrere Programme im Speicher konfliktfrei quasi-gleichzeitig ausgeführt werden. Hierzu wird jedes Programm in einem (virtuellen) Speicherraum ausgeführt in dem es alleine existiert und damit nicht mit anderen Programmen in Speicherzugriffskonflikte kommen kann, so dass Speicherschutz erzielt wird (z. B. "Programm A überschreibt irrtümlich bei Programm B eine Variable im Speicher" kann nicht mehr auftreten). Dies erreicht die MMU über eine Tabelle (TLB) in der für die zuletzt lokalisierten virtuellen Adresse aller Programme die echte physikalische Adresse eines Speicherblocks vermerkt ist. Bei jedem Zugriff (Speicher anfordernd, schreibend oder lesend) wird, transparent für Programme und Programmierer, auf eine eindeutige physikalische Adresse umgelenkt. Ein weiterer positiver Effekt ist, dass eine Speicherfragmentierung des physikalischen Speichers nicht mehr auftreten kann. Durch die Adressumsetzung kann die MMU fast beliebig zerstückelten physikalischen Speicher als durchgängig zugreifbaren Block virtuellen Speichers dem Programm präsentieren. Dies ist ein effektiver Mechanismus, so lange die Größe des physikalischen Speichers deutlich kleiner ist als die des virtuellen Adressraums (4 GByte). Durch die kontinuierlich fallenden RAM-Speicherpreise ist dies inzwischen nicht mehr gegeben; der virtuelle Speicherraum kann die Fragmentierung des physikalischen Speichers nicht mehr immer kaschieren, da er nun selbst zu stark fragmentiert sein kann.

Virtuelle Adressübersetzung

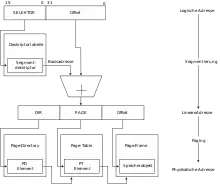

Die IA-32-Architektur verwendet eine 48 Bit breite segmentierte logische Adresse, welche zu 16 Bit aus Selektor und zu 32 Bit aus Offset besteht. Durch die Segmentierung wird die logische Adresse in eine lineare 32-Bit-Adresse übersetzt und kann anschließend durch den Paging-Mechanismus in eine physische 32-Bit-Adresse übersetzt werden. Wird Paging vom System nicht eingesetzt, so ist die lineare 32-Bit-Adresse die physische Adresse.

Schutzfunktionen durch die Virtuelle Speicherverwaltung

Die MMU enthält vier zentrale Systemregister GDTR (Global Descriptor Table Register), IDTR (Interrupt Descriptor Table Register), LDTR (Local Descriptor Table Register) und TR (Task Register). Damit werden die Schutzmechanismen realisiert.

Die IA-32 Architektur enthält für den Multitasking/Multiuser-Betrieb die folgenden fünf Schutzfunktionen:

- Typ-Check

- Limit-Check

- Zugriff auf Daten

- Kontroll-Transfer

- Instruction-Check

Diese Schutzfunktionen werden mit verschiedenen Hardware-Mechanismen realisiert.

Weitere Funktionen

In den nachfolgenden CPU-Generationen wurden weitere Funktionen hinzugefügt:

- Die Modelle des i486DX haben einen mathematischen Koprozessor bereits integriert, zusätzlich wurde ein Cache auf den Chip integriert (die Budget-Version i486 SX wurde mit deaktiviertem Koprozessor gefertigt). Außerdem wurde die Ausführungseinheit nach dem Fließbandprinzip aufgebaut, genannt Prozessor-Pipeline, was den Befehlsdurchsatz deutlich erhöht.

- Mit dem Pentium wurde eine zweite Ausführungseinheit der Architektur hinzugefügt. Diese nun parallelen Ausführungseinheiten, genannt Pipelines U und V, ermöglichen superskalare Programmausführung über Out-of-order execution des Prozessors.

- Beim Pentium MMX wurden Befehle hinzugefügt, die mehrere ganzzahlige Daten gleichzeitig bearbeiten (SIMD) – dies ist vor allem für Multimedia-Daten sinnvoll. MMX steht für “Matrix Math Extensions”, besonders vom Marketing aber auch häufig “Multi Media Extensions” tituliert.

- Mit dem Pentium III wurden die SIMD-Befehle erweitert, um auch Gleitkommazahlen bearbeiten zu können (Streaming SIMD Extensions/SSE).

- Beginnend mit den Prescott-Modellen der Xeon-/Pentium-4-Reihe erhalten die Prozessoren eine Erweiterung um einen 64-Bit-Modus (Intel 64, früher auch EM64T genannt), der weitgehend dem AMD64-Modus der Opteron- und Athlon-64-CPUs von Mitbewerber AMD entspricht.

Siehe auch

- x86-Prozessor

- x64 (auch x86-64)

- Itanium-Architektur bzw. IA-64 (Intel Architecture 64-Bit – nicht x86-kompatible 64-Bit-Architektur von Intel)

- Liste der Mikroprozessoren von Intel

- Liste von Mikroprozessoren

Weblinks

- IA-64- und IA-32-Handbücher von Intel (PDF, englisch)

Einzelnachweise

- Martin Gerhard Loschwitz: Slackware 15.0: Modellpflege nach langer Pause beim Linux-Urgestein. In: Heise online. 8. Februar 2022. Abgerufen am 16. Februar 2022.; Zitat: „Sie stehen in Varianten sowohl für die x86_64-Architektur als auch die alte Intel-Architektur IA32 zur Verfügung.“.