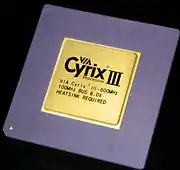

VIA Cyrix III

Der VIA Cyrix III ist ein x86-Prozessor für den Sockel 370 von VIA Technologies.

| VIA Cyrix III | |

|---|---|

| |

| Produktion: | 2000 bis 2001 |

| Produzent: | TSMC |

| Prozessortakt: | 350 MHz bis 733 MHz |

| FSB-Takt: | 100 MHz bis 133 MHz |

| L2-Cachegröße: | 0 KiB bis 256 KiB |

| Befehlssatz: | x86 |

| Mikroarchitektur: | CISC |

| Sockel: | Sockel 370 |

Namen der Prozessorkerne:

| |

Ursprünglich sollte nach dem Kauf von Cyrix durch VIA unter dem Namen VIA Cyrix III Anfang 2000 ein echter Cyrix-Prozessor erscheinen. Diese CPU war schon so lange in der Entwicklung, dass sie gleich drei unterschiedliche Codenamen bekommen hatte: Ursprünglich wurde mit der Entwicklung unter dem Namen „Cayenne“ begonnen, als Cyrix noch selbständig war. Nach der Verschmelzung mit National Semiconductor wurde der Codename in „Gobi“ geändert. Aber in den gut zwei Jahren der Zugehörigkeit zu NS konnte die CPU nicht fertiggestellt werden. Erst nach der Übernahme durch VIA wurde die CPU unter dem Codenamen „Joshua“ fertig.

Ursprünglich noch für das Performance-Segment geplant, musste er wegen der großen Verspätung zum Konkurrenten für Intels Low-Cost-CPU Celeron umgeplant und die FPU überarbeitet werden. Der Prozessor enttäuschte in ersten Vorabtests: Instabilitäten, hohe Wärmeentwicklung und zu hoch angesetzte P-Ratings führten dazu, dass VIA Technologies das Joshua-Design komplett aufgab und stattdessen den von Centaur Technology entwickelten Samuel als VIA Cyrix III verkaufte.

Dieser Samuel-Prozessor wurde Mitte 2000 auf den Markt gebracht und war im Prinzip ein auf den Sockel 370 portierter WinChip 3 mit höheren Taktraten und besserer Fertigungstechnik. Wegen des fehlenden L2-Caches (bei der WinChip-Serie war der L2-Cache wie beim Sockel 7 üblich auf dem Mainboard, was es beim Sockel 370 nicht gab) war die CPU kaum konkurrenzfähig.

Der Nachfolger Samuel 2 wurde dann unter dem Namen VIA C3 verkauft.

Modelldaten

Joshua

- Cyrix-Design

- Codename: anfangs „Cayenne“, nach Übernahme durch National Semiconductor „Gobi“, nach Übernahme durch VIA Technologies "Joshua"

- L1-Cache: 64 KiB (unified)

- L2-Cache: 256 KiB mit Prozessortakt

- MMX, 3DNow!

- Sockel 370, GTL+ mit 100 bis 133 MHz Front Side Bus

- Betriebsspannung (VCore): 2,2 V

- Erscheinungsdatum: Februar 2000

- Fertigungstechnik: 0,18 µm bei TSMC

- Die-Größe: unbekannt bei 22,0 Millionen Transistoren

- Taktraten: 350 MHz bis 450 MHz

- PR433: 350 MHz (100 MHz FSB)

- PR466: 366 MHz (122 MHz FSB)

- PR500: 400 MHz (133 MHz FSB)

- PR533: 433 MHz (124 MHz FSB)

- PR533: 450 MHz (100 MHz FSB)

Samuel

- Centaur-Design

- Codename: C5A

- L1-Cache: 64 + 64 KiB (Daten + Instruktionen)

- L2-Cache: nicht vorhanden

- MMX, 3DNow!, LongHaul!

- Sockel 370, GTL+ mit 100 und 133 MHz Front Side Bus

- Betriebsspannung (VCore): 1,90 V oder 2,00 V

- Leistungsaufnahme (TDP): ca. 7 W bis 10 W

- Erscheinungsdatum: Juni 2000

- Fertigungstechnik: 0,18 µm bei TSMC

- Die-Größe: 75 mm² bei 11,3 Millionen Transistoren

- Taktraten: 500, 550, 600, 650, 667, 700 und 733 MHz