Cyrix 6x86MX

Der Cyrix 6x86MX war ein 1997 erschienener Mikroprozessor der Firma Cyrix und ist der Nachfolger des Cyrix 6x86. Spätere Varianten (mit CPU-Takt ab 225 MHz und P-Rating ab 300) wurden ab dem 15. April 1998 unter der Bezeichnung Cyrix MII vermarktet, während IBM die Bezeichnung 6x86MX beibehielt und den MII-300 und -333 weiterhin als 6x86MX-PR300 und 6x86MX-PR333 verkaufte.

| Cyrix 6x86MX | |

|---|---|

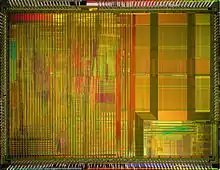

6x86MX PR200 | |

| Produktion: | 30. Mai 1997 bis 2000 |

| Produzent: | Cyrix, IBM und ST Microelectronics |

| Prozessortakt: | 133 MHz bis 300 MHz |

| FSB-Takt: | 55 MHz bis 100 MHz |

| L1-Cachegröße: | 64 KiB |

| Befehlssatz: | x86 |

| Sockel: | Sockel 7 |

| Name des Prozessorkerns: | M2 |

Technisches

Der 6x86MX ist als Reaktion auf den Intel Pentium MMX mit Intels MMX-Befehlserweiterung zu sehen. Diese MMX-Befehle waren auch im Intel Pentium II und AMD K6 integriert. Cyrix war also unter einem gewissen Zugzwang und entwickelte die voll MMX-kompatible Multimedia-Erweiterung EMMI (steht für Enhanced MultiMedia Instructions), welche in den Cyrix 6x86MX integriert wurde.

Diese CPU wurde am 30. Mai 1997 auf den Markt gebracht und basiert zum großen Teil auf dem älteren Cyrix 6x86, wurde aber mit einem viel größeren L1-Cache (64 statt 16 KiB), einer verbesserten Sprungvorhersage und natürlich besagter EMMI-Technologie ausgestattet. Außerdem wurden dem 6x86MX weitere Funktionen des Pentium Pro mitgegeben. Auch DualVoltage wurde nun von Anfang an unterstützt.

Der 6x86MX war alles in allem eine recht gute CPU, die dank der Verbesserungen im Integer-Bereich auftrumpfen konnte und wiederum eine höhere Leistung als die Konkurrenzprodukte bei gleicher Taktfrequenz erreicht. Aus diesem Grund wurde erneut ein P-Rating benutzt. Eine weitere Änderung gegenüber dem 6x86 war die Verwendung von deutlich flexibleren Multiplikatoren: x2,5 wurde möglich und erlaubte damit eine wesentlich größere Palette an Taktfrequenzen.

Nach der Übernahme von Cyrix durch VIA Technologies 1999 wurden die MII-CPUs von TSMC produziert. Dank eines Die-Shrinks auf 0,18 µm konnten in den Varianten MII-366, MII-400 und MII-433 die Taktraten leicht gesteigert werden.

Modelldaten

6x86MX

- Codename: M2

- Verkauft als: Cyrix 6x86MX, IBM 6x86MX

- L1-Cache: 64 KiB (unified)

- L2-Cache: abhängig von verwendeter Hauptplatine bzw. Chipsatz

- MMX

- Sockel 7 mit einem Front Side Bus von 55 bis 83 MHz

- Betriebsspannung (VCore): 2,9 V

- Erscheinungsdatum: Mai 1997

- Fertigungstechnik: 0,35 µm bei IBM und ST Microelectronics

- Die-Größe: 197, 156, 119 bzw. 65 mm² bei 6,5 Millionen Transistoren

- Taktraten: 133 MHz bis 250 MHz

- PR166+: 133 MHz (66 MHz FSB)

- PR166+: 137,5 MHz (55 MHz FSB)

- PR166+: 150 MHz (50 oder 60 MHz FSB)

- PR200+: 150 MHz (75 MHz FSB)

- PR200+: 165 MHz (55 MHz FSB)

- PR200+: 166 MHz (66 MHz FSB)

- PR200+: 180 MHz (60 MHz FSB)

- PR233+: 166 MHz (83 MHz FSB)

- PR233+: 187,5 MHz (75 MHz FSB)

- PR233+: 200 MHz (66 MHz FSB)

- PR266+: 207,5 MHz (83 MHz FSB)

- PR266+: 225 MHz (75 MHz FSB)

- PR266+: 233 MHz (66 MHz FSB)

MII

- Codename: M2

- Verkauft als: Cyrix MII, IBM 6x86MX (nur 6x86MX-PR300 und -PR333)

- L1-Cache: 64 KiB (unified)

- MMX

- Sockel 7 mit einem Front Side Bus von 66 bis 100 MHz

- Betriebsspannung (VCore): 2,9 V (2,0 V und 2,2 V bei 0,18 µm)

- Erscheinungsdatum: April 1998

- Fertigungstechnik: 0,25 µm bei IBM und National Semiconductor, später bei TSMC (0,18 µm)

- Die-Größe: 197, 156, 119 bzw. 65 mm² bei 6,5 Millionen Transistoren

- Taktraten: 225 MHz bis 300 MHz

- 300: 225 MHz (75 MHz FSB)

- 300: 233 MHz (66 MHz FSB)

- 333: 250 MHz (83 MHz FSB)

- 333: 263 MHz (75 MHz FSB)

- 366: 250 MHz (100 MHz FSB)

- 400: 285 MHz (95 MHz FSB)

- 433: 300 MHz (100 MHz FSB)

Siehe auch

Weblinks

- Cyrix MII Datenblatt (PDF-Datei; 1,21 MB)