Tensilica

Tensilica war ein Unternehmen mit Sitz im Silicon Valley, das IP-Cores entwickelte. 2013 wurde Tensilica aufgekauft und zu einer Abteilung von Cadence Design Systems gemacht. Die dort entwickelten Dataplane-Prozessoren (DPUs) vereinen die Stärken von Prozessoren (CPUs) und Digitalen Signalprozessoren (DSPs) durch benutzerdefinierte Logik. Dadurch sind sie für die Verarbeitung datenintensiver Aufgaben geeignet.

| Tensilica Inc. | |

|---|---|

| Rechtsform | Tochterunternehmen |

| Gründung | 1997 |

| Auflösung | 2013 |

| Auflösungsgrund | Übernahme durch Cadence |

| Sitz | San José (Kalifornien) |

| Leitung | Chris Rowen, Jack Guedj |

| Branche | Halbleitertechnologieunternehmen |

| Website | https://ip.cadence.com |

Tensilica ist bekannt für seine anpassbaren Mikroprozessorkerne wie den konfigurierbaren Prozessor Xtensa. Weitere Produkte sind: HiFi-Audio- und Sprach-DSPs mit einer Software-Bibliothek von über 225 Codecs von Cadence und über 100 Software-Partnern; Vision-DSPs, die komplexe Algorithmen in Bildgebung, Video, Computer Vision und neuronalen Netzen handhaben und die ConnX-Familie von Basisband-DSPs vom Dual-MAC-ConnX D2 bis zum 64-MAC-ConnX-BBE64EP.

Tensilica wurde 1997 von Chris Rowen und Harvey C. Jones[1] in Santa Clara (Kalifornien) gegründet, der auch einer der Gründer von MIPS Technologies war und zunächst von mehreren ehemaligen Mitarbeitern anderer Prozessorhersteller und Electronic Design Automation (EDA) Softwarehersteller aus dem Silicon Valley startete. Auch der Mitentwickler der MIPS-Architektur Earl Killian wurde dort als leitender Softwarearchitekt angestellt.[2] Am 11. März 2013 kündigte Cadence Design Systems an, Tensilica für rund 380 Millionen Dollar in bar aufzukaufen.[3] Im April 2013 akquirierte Cadence Tensilica mit Barmitteln in Höhe von rund 326 Millionen US-Dollar.[4]

Produkte

Cadence Tensilica entwickelt IP-Cores für Integrierte Schaltungen wie SoCs seiner Lizenznehmer für eingebettete Systeme, besonderes für die Anwendung in Mobilgeräten, Home Entertainment und Kommunikation. Tensilica IP-Cores werden zur einfachen Integration in Chip-Designs als synthetisierbare Register Transfer Daten (RTL-Modelle) geliefert.

Konfigurierbare Cores der Xtensa-Serie

Ein Xtensa-Prozessor kann von einem kleinen, stromsparenden Mikrocontroller ohne Cachespeicher bis zu einem Hochleistungs-16-Wege SIMD-Prozessor, dreifach VLIW-DSP-Kern oder 1-TMAC-Neuronal-Netzwerkprozessor reichen. Alle Cadence-Standard-DSPs basieren auf der Xtensa-Architektur.

IP-Core-Prozessorhersteller wie Tensilica bieten ihren Lizenznehmern typischerweise die Wahl zwischen vielen Implementierungsdetails des IP-Kerns: Cache-Größe, Prozessor-Busbreite, Daten- und Befehls-RAM, Speicherverwaltung und Interrupt-Steuerung. Die Xtensa-Architektur von Cadence bietet als wesentliche Funktion den vom Benutzer anpassbaren Befehlssatz.

Mithilfe der mitgelieferten Anpassungstools können Kunden den Xtensa-Basisbefehlssatz selbst erweitern, indem sie neue benutzerdefinierte Befehle definieren. Erweiterungen können SIMD Anweisungen, neue Registerdateien und zusätzliche Datenübertragungsschnittstellen für Multiprozessorkommunikation beinhalten. Nachdem die endgültige Prozessorkonfiguration erstellt und übergeben wurde, erstellt der Tensilica-Prozessorgenerator den so konfigurierten Xtensa-IP-Core, das Prozessor-Design-Kit und das Softwareentwicklungs-Kit. Dieser Prozess ist hochgradig automatisiert, so dass Konstrukteure schnell mit den verschiedenen selbst erstellten Befehlen experimentieren können, um sowohl Leistungs-Verbesserungen und -Einbußen unter den möglichen Alternativen auszutesten.

Das Prozessor-Kit enthält die notwendigen Elemente, um den konfigurierten IP-Core in die Chipdesign-Entwicklungsumgebung beim Kunden zu integrieren: die Hardware-Beschreibung des Kerns (in synthetisierbarer Registertransfersprache (RTL) oder physischer Post-Layout-Form), Timing- und I/O-Einschränkungen, Anforderungen für technologiespezifische RAMs/Caches/FIFOs. Das Software-Kit baut auf einer Eclipse (IDE) basierenden integrierten Entwicklungsumgebung auf und verwendet die von der GNU Compiler Collection abgeleitete Toolchain: C/C++-Compiler, Assembler, Linker, Debugger. Ein Befehlssatzsimulator ermöglicht es Kunden, mit der Anwendungsentwicklung zu beginnen, bevor die tatsächliche Hardware verfügbar ist.

Der Befehlssatz des Xtensa

Der Xtensa-Befehlssatz wurde entwickelt, um den verschiedenen Anforderungen der Dataplane-Verarbeitung gerecht zu werden. Diese 32-Bit-Architektur bietet einen kompakten 16- und 24-Bit-Befehlssatz mit nicht modalem Umschalten für maximale Leistungseffizienz und Leistung. Der Basisbefehlssatz hat 80 RISC-Befehle und eine 32-Bit-ALU mit bis zu 64 Universal-32-Bit-Registern und sechs Spezialregistern.

HiFi-Audio und Voice-DSP IP

- HiFi Mini Audio DSP – Der kleinste DSP-Kern mit der niedrigsten Stromaufnahme für Sprachausgabe und Spracherkennung

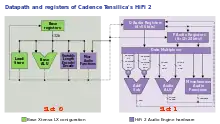

- HiFi 2 Audio DSP – Dieser hocheffiziente DSP-Core bietet die leistungsstärkste MP3-Verarbeitung.

- HiFi EP Audio DSP – Oberklasse-HiFi-2 mit erweiterten Optimierungen für DTS Master Audio, verbesserter Vor- und Nachbearbeitung der Stimme und verbessertem Cachespeicher-Subsystem

- HiFi 3 Audio DSP – Volle 32-Bit-Verarbeitung macht diesen DSP für viele der Audio-Verbesserungsalgorithmen, Breitband-Sprachcodecs und Mehrkanal-Audio äußerst effizient.

- HiFi 3z Audio DSP – energieeffizienter DSP für objektbasiertes Audio, Super-Breitband-Sprachcodecs und automatische Spracherkennung mit neuronalem Netzwerk

- HiFi 4 DSP – 2 × HiFi 3-Leistung für DSP-intensive Anwendungen einschließlich neuer objektbasierter Mehrkanal-Audiostandards

Vision-DSPs

- Vision P5 DSP mit 4- bis 100-facher Leistung eines herkömmlichen mobilen CPU+GPU-Systems zu einem Bruchteil des Verhältnisses Energie zu Leistung[5]

- Vision P6 DSP mit vierfacher Leistung des Vision-P5-DSPs für anspruchsvolle Bild- und Computer-Video-Anwendungen.[6]

- Vision C5 DSP, mit 1 TMAC pro Sekunde Rechenleistung, um Rechenaufgaben eines neuronalen Netzwerks ohne zusätzliche festverdrahtete Beschleuniger ausführen zu können.[7]

Adoption

AMD TrueAudio, ein Audio-DSP, der u. a. in der Playstation 4, in den AMD-APUs des „Kaveri“-Desktops sowie in einigen AMD-dGPUs verbaut ist, basiert auf dem Cadence Tensilica HiFi-EP-Audio-DSP.[8]

Microsoft HoloLens verwendet einen speziell gefertigten TSMC-28-nm-Coprozessor mit 24 Tensilica-DSP-Kernen mit rund 65 Millionen Logikgattern, 8 MiB SRAM und eine zusätzliche Schicht von 1 GB Low-Power-DDR3-RAM.[9]

Espressif ESP8266 Wi-Fi IoT-SoC integriert den Tensilica Diamond auf einem Standard 106-Micro-32-Bit-Controller-Prozessorkern, den Espressif L106 nennt.

Spreadtrum lizenzierte sich einen HiFi-DSP für Smartphones.[10]

VIA Technologies verwendet einen HiFi-DSP im SoC für Set-Top-Boxen, Tablets und mobile Geräte.[11]

Realtek hat Chips für Mobilgeräte und PC-Produkte auf Plattform des HiFi-Audio-DSP aufgebaut.[12]

Über 80 führende Halbleiterhersteller und OEM-Systemkunden von Tensilica verwenden HiFi-Audio-DSPs in ihren Chipdesigns.

Geschichte

- 1997 wurde Tensilica von Chris Rowen gegründet.

- 2002 veröffentlichte Tensilica die Unterstützung für flexible Befehlskodierungenlängen, bekannt als FLIX.

- 2013 wurde Tensilica von Cadence Design Systems übernommen.

Name der Firma

Der Markenname Tensilica ist eine Kombination der Wörter Tensile (=dehnbar, erweiterungsfähig) und Silica (=Silizium), das Element aus dem integrierte Schaltkreise hergestellt werden.

Einzelnachweise

- Harvey Jones, Tensilica Inc: Profile & Biography. Abgerufen am 12. Mai 2018 (englisch).

- Technical Advisory Board, Stretch. 26. November 2010. „Earl … He is the former Chief Architect of Tensilica and Silicon Graphics MIPS division, …“

- SEMbyotic - sembyotic.com: Cadence to Acquire Tensilica | Cadence IP. Abgerufen am 12. Mai 2018 (englisch).

- SEMbyotic - sembyotic.com: Cadence Reports First Quarter 2013 Financial Results and Completes Acquisition of Tensilica | Cadence IP. Abgerufen am 12. Mai 2018 (englisch).

- New Cadence Tensilica Vision P5 DSP Enables 4K Mobile Imaging with 13X Performance Boost and 5X Lower Energy. Abgerufen am 12. Mai 2018 (englisch).

- Cadence Announces New Tensilica Vision P6 DSP Targeting Embedded Neural Network Applications. Abgerufen am 12. Mai 2018 (englisch).

- Cadence Unveils Industry’s First Neural Network DSP IP for Automotive, Surveillance, Drone and Mobile Markets. Abgerufen am 12. Mai 2018 (englisch).

- Everything You Wanted to Know About AMD TrueAudio. In: Maximum PC. 8. Oktober 2013. Archiviert vom Original am 11. Juli 2014. Abgerufen am 6. Juli 2014.

- Microsoft's HoloLens secret sauce: A 28nm customized 24-core DSP engine built by TSMC. (theregister.co.uk [abgerufen am 12. Mai 2018]).

- Spreadtrum Licenses Tensilica HiFi Audio/Voice DSP. Abgerufen am 12. Mai 2018 (englisch).

- Customer Spotlight: VIA Technologies Licenses Cadence Tensilica HiFi Audio/Voice DSP. Abgerufen am 12. Mai 2018 (englisch).

- Realtek Licenses Cadence's Tensilica HiFi Audio/Voice DSP IP Core. Abgerufen am 12. Mai 2018 (englisch).