Polysiliziumverarmung

Die Polysiliziumverarmung ist ein physikalisches Phänomen, das in der Halbleitertechnik bei Feldeffekttransistoren, welche aus dem Gate-Material Polysilizium bestehen, auftreten kann. Der Effekt kann und zu unerwünschten Schwankungen der Schwellenspannung einzelner Feldeffekttransistoren sowie einem unvorhersehbaren Verhalten der gesamten elektronischen Schaltung führen.[1]

Polysilizium als Gate-Material

In der Halbleitertechnik wird polykristallines Silizium, auch als Polysilizium bezeichnet und ein Material, das aus kleinen Siliziumkristallen besteht, für verschiedene Anwendungen eingesetzt. Eine der wichtigsten Anwendungen ist der Einsatz als Material für die Gate-Elektrode eines Feldeffekttransistors, beispielsweise in der Planartechnik. Hier verdrängte Polysilizium in den 1980er Jahren Gate-Elektroden aus Metall (z. B. Aluminium), da sein Einsatz im Schichtstapel mit dem Gate-Dielektrikum aus Siliciumdioxid und Silicium als Kanalmaterial Vorteile auswies, unter anderem auch für die Fertigung (Hochtemperaturfähigkeit, selbjustierdende Source-/Drain-Gebiete etc.).

Die Leitfähigkeit der Polysiliziumschicht ist sehr gering, und aufgrund dieser geringen elektrischen Leitfähigkeit ist die Ladungsakkumulation gering, was zu einer Verzögerung der Kanalbildung und damit zu unerwünschten (zeitlichen) Verzögerungen in den Schaltungen führt. Aus diesem Grund wird das Polysilizium in der Regel mit stark n- oder p-Störstellen dotiert, womit sich die elektrische Leitfähigkeit deutlich erhöht und ähnlich wie ein Metall als (in erster Näherung) idealer Leiter betrachtet werden kann. Infolge dessen verringern sich auch die angesprochenen Schaltverzögerungen.

Nachteile von dotiertem Polysilizium als Gate-Material

Vgs = Gate-Spannung

Vth = Schwellenspannung

n+ = stark n-dotierter Bereich

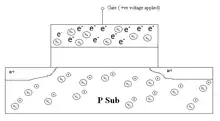

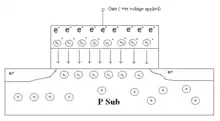

In Abbildung 1(a) ist zu sehen, dass die freien Majoritätsladungsträger aufgrund des Fehlens eines externen elektrischen Feldes über die gesamte Struktur verstreut sind. Wenn ein positives Feld an das Gate angelegt wird (Gate-Bulk/Source-Spannung), ordnen sich die verstreuten Ladungsträger wie in Abbildung 1(b) an, die Elektronen nähern sich dem Gate-Anschluss, aber aufgrund der offenen Schaltung können sie nicht fließen. Infolge der Ladungstrennung bildet sich an der Polysilizium-Oxid-Grenzfläche eine Verarmungszone, die sich direkt auf die Kanalbildung in MOSFETs auswirkt.[2] Dabei bildet die Verarmungsschicht im Polyzilizium eine zusätzliche elektrische Kapazität, die mit der Kapazität des Gate-Dielektrikums in Reihe geschaltet ist. Diese ist umso größer je geringer die Dotierung des Polysiliziums ist. Dadurch erhöht sich die effektive Dicke des Gate-Dielektrikums und die Transsistoreigenschaften (wie Transkonduktanz, Schwellenspannung, Einschaltstrom usw.) verschlechtern sich, das heißt, der Transistor schaltet langsamer.

In einem NMOS mit n+-Polysilizium-Gate unterstützt der Polysilizumverarmungseffekt die Kanalbildung durch die kombinierte Wirkung des (+)ve-Feldes der Donorionen (ND) und des extern angelegten (+)ve-Feldes am Gate-Anschluss. Grundsätzlich verstärkt die Akkumulation der (+)ve geladenen Donorionen (ND) auf dem Polysilizium die Bildung des Inversionskanals, und wenn Vgs > Vth ist, bildet sich eine Inversionsschicht, wie in Abbildung 1(b) zu sehen ist, wo der Inversionskanal aus Akzeptorionen (NA) (Minoritätsträger) gebildet wird.[3] Die Polysiliziumverarmung kann je nach Herstellungsprozess seitlich über einen Transistor variieren, was bei bestimmten Transistorabmessungen zu erheblichen Transistorschwankungen führen kann.

Wiedereinführung von Gate-Elektroden aus Metall

Wie oben beschrieben wurde lange Zeit dotiertes Polysilizium als Gate-Material in MOS-Bauelementen bevorzugt. Es wurde verwendet, da seine Arbeitsfunktion mit dem Si-Substrat übereinstimmte (was zu der niedrigen Schwellenspannung des MOSFET führt). Optimierte metallische Gate-Elektroden wurden wieder eingeführt, als SiO2-Dielektrika durch High-k-Dielektrika wie Hafnium(IV)-oxid als Gate-Oxid in der gängigen CMOS-Technologie ersetzt wurden (32- und 28-nm-Technologieknoten).[4] Die folgende Technologie ist als High-k+Metal-Gate-Technik (HKMG-Technik) bekannt.[5] Neben dem großerwerdenenden Einfluss der Polysiliziumverarmung bei dünner werdenden Gate-Dielektrika, ist hier auch die Bildung einer SiOx-Schicht an der Grenzfläche vom Gate-Dielektrikum zum Polysilizium als Grund zu nennen. Des Weiteren besteht eine hohe Wahrscheinlichkeit für das Auftreten von Fermi-Level-Pinning.[6]

Der Effekt der Polysiliziumverarmung ist eine unerwünschte Verringerung der Schwellenspannung, die bei der Schaltungssimulation nicht berücksichtigt wurde. Um diese Art von Schwankung der Schwellenspannung des MOSFETs zu vermeiden, wird mit den gestiegenen Anforderungen an die geringe Variation der elektrischen Parameter bei modernen Schaltkreisen ein Metall-Gate gegenüber Polysilizium bevorzugt.

Einzelnachweise

- R. Rios, N.D. Arora: An analytic polysilicon depletion effect model for MOSFETs. In: IEEE Electron Device Letters. 15, Nr. 4, 1994, S. 129–131. doi:10.1109/55.285407.

- R. Rios, N.D. Arora: Modeling the polysilicon depletion effect and its impact on submicrometer CMOS circuit performance. In: IEEE Transactions on Electron Devices. 42, Nr. 5, 1994, S. 935–943. doi:10.1109/16.381991.

- K.F. Schuegraf, C.C. King, C. Hu: Impact of polysilicon depletion in thin oxide MOS technology. In: 1993 International Symposium on VLSI Technology, Systems, and Applications Proceedings of Technical Papers. 1993, S. 86–90, doi:10.1109/VTSA.1993.263633.

- 32/28nm High-k Metal Gate. (Nicht mehr online verfügbar.) GlobalFoundries, archiviert vom Original am 9. Mai 2013; abgerufen am 7. November 2021.[ ]

- From Sand to Silicon: The Making of Chip. Intel Technology. 11. November 2011. Abgerufen am 8. Juni 2013.

- C.C. Hobbs u. a.: Fermi-level pinning at the polysilicon/metal oxide interface-Part I. In: IEEE Transactions on Electron Devices. Band 51, Nr. 6, Juni 2004, S. 971–977, doi:10.1109/TED.2004.829513.