Schieberegister

Ein Schieberegister ist ein logisches Schaltwerk. Mehrere in Reihe geschaltete Flipflops schieben ihren Speicherinhalt (je 1 Bit) bei jedem Arbeitstakt um ein Flipflop weiter – anschaulich gesehen ähnlich einer Eimerkette. Die Anzahl der im Register vorhandenen Speicherplätze ist konstant.

.svg.png.webp)

Schieberegister arbeiten nach dem FIFO-Prinzip. Das zuerst eingespeicherte Bit verlässt den Speicher zuerst. Das Herein- und Herausschieben, das Ein- und das Auslesen geschehen dabei synchron, ein Schieberegister kann nur bedingt als Warteschlange genutzt werden.

Oft erweitert man Schieberegister mit zusätzlicher Logik (bestehend aus mehreren Logikgattern). Diese kann dafür sorgen,

- dass das höchste Bit in das niedrigste Bit geschoben wird (es findet also eine Rotation statt, man spricht auch von einem Rundschiebe-Register),

- dass man es bidirektional betreiben kann, die Richtung der Verschiebung also variabel ist,

- dass festgelegt werden kann, ob das freiwerdende Bit gesetzt oder gelöscht werden soll, und/oder

- dass man das Register parallel beschreiben oder auslesen kann.

Aufbau

.

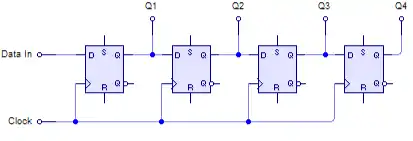

Das in dieser Abbildung gezeigte 4-Bit-Schieberegister basiert im Wesentlichen auf dem eigentlichen Schieberegister bestehend aus den Flip-Flops D00, D10, D20 und D30. Die Anschlüsse sind wie folgt definiert:

- Über die Anschlüsse d0 bis d3 kann ein Wert parallel eingelesen werden.

- Über die Anschlüsse Q0 bis Q3 kann der im Schieberegister gespeicherte Wert parallel ausgelesen werden.

- Über den Data-In-Anschluss (DI) kann ein Wert seriell eingelesen werden und über den Data-Out-Anschluss (DO) seriell ausgelesen werden.

- Zur Ansteuerung werden die Anschlüsse Clock (CLK), Load (LD) und Enable (EN) verwendet.

Data-In und Data-Out

Die Data-In- und Data-Out-Anschlüsse können je nach Beschaltung verschiedene Funktionen erfüllen:

- Serielles Lesen am Data-In-Anschluss und serielles Ausgeben von Daten am Data-Out-Anschluss.

- Aufbau eines Ringregisters durch Verbinden des Data-Out- mit dem Data-In-Anschluss.

- Serielle Erweiterung des Schieberegisters um weitere Schieberegister um größere Wortbreiten verarbeiten zu können. Dazu wird der Data-Out-Anschluss mit dem Data-In-Anschluss des nachfolgenden Schieberegisters verbunden.

Clock

Bei einer positiven Flanke am Clock-Eingang wird das in den jeweiligen Flip-Flops gespeicherte Bit am Ausgang ausgegeben, dadurch an das nachfolgende Eingabe-Gatter (D00→D11; D10→D21; etc.) weitergegeben und so lange gehalten, bis erneut eine positive Flanke am Clock-Eingang auftritt.

Load

Ist der Load-Eingang auf High gesetzt, so werden die an den Eingabe-Gattern (D01, D11, D21 und D31) angelegten Bits der vorgeschalteten Flip-Flops (bzw. des DI-Eingangs) eingelesen. Ist der Load-Eingang hingegen auf Low, so wird das Bit des vorgeschalteten Flip-Flops (bzw. DI-Eingangs) ignoriert und stattdessen das Bit am zugehörigen parallelen Eingang eingelesen. Das eingelesene Bit wird dabei an das nachfolgende Flip-Flop (bzw. DO-Ausgang) weitergegeben.

Ist ein paralleles Einlesen nicht erforderlich, so können die Gatter D01, D11, D21 und D31, sowie die Eingänge d0 bis d3 weggelassen werden und die Ausgänge der Flip-Flops (bzw. Data-Out) direkt mit den Eingängen der nachfolgenden Flip-Flops (bzw. Data-In) verbunden werden.

Enable

Der Enable-Eingang steuert den Ausgangspuffer, bestehend aus den Gattern D02, D12, D22 und D32, an. Bei einer positiven Flanke wird das im Schieberegister gespeicherte Bitmuster vom Ausgangspuffer übernommen und am parallelen Ausgang mit den Anschlüssen Q0 bis Q3 ausgegeben. Der Wert wird so lange gehalten, bis eine erneute positive Flanke am Enable-Eingang anliegt.

Wird kein Ausgangspuffer gefordert, so können der Enable-Eingang und die Gatter D02, D12, D22 und D32 weggelassen werden. Die Ausgänge Q0 bis Q3 werden in diesem Fall direkt am Ausgang der zugehörigen Schieberegister-Flip-Flops angeschlossen.

Aufbau eines bidirektionalen Schieberegisters

Um ein bidirektionales Schieberegister zu realisieren, werden entweder zwei Schieberegister benötigt, oder Tristate-Gatter, die die internen Verbindungen des Registers dynamisch umschalten können.

Bei der Realisierung mit Hilfe von zwei Schieberegistern wird der parallele Eingang des einen Registers in gekreuzter Weise mit dem parallelen Eingang des anderen Registers verbunden und umgekehrt. Dadurch kann der Wert aus dem nach links schiebenden Register in das nach rechts schiebende Register kopiert werden und umgekehrt.

Verwendung

Serialisierung und Parallelisierung von Bitmustern

Schieberegister sind Bestandteil von Wandlern zwischen seriellen und parallelen Daten. Mittels Schieberegistern lässt sich also eine Serialisierung oder Parallelisierung von Bitmustern realisieren. Bei einer Serialisierung muss es dabei möglich sein, das jeweilige Bitmuster parallel in das Schieberegister zu laden, d. h. jedes Flipflop benötigt einen Lade-Eingang. Ansonsten läge ja bereits eine serielle Repräsentation vor. Bei einer Parallelisierung muss entsprechend jedes Flipflop über einen lesbaren Ausgang verfügen, damit zu einem bestimmten Zeitpunkt die Werte des gesamten Schieberegisters parallel ausgelesen werden können. Bei dem von den meisten µ-Controllern befindlichen Schnittstelle SPI handelt es sich um ein Schieberegister-basierenden Bussystem, mit welchem direkt SR-Logikbausteine als parallele Ausgänge (Ports) genutzt werden können.

Bitverschiebung in Maschinensprachen

Die meisten Maschinensprachen verfügen über einen Shift-Befehl auf den Registern. Damit kann man in Maschinensprache durch Schieben und Addieren oft sogar schneller multiplizieren als über den generischen Multiplikationsbefehl/Multiplikationsalgorithmus. So multipliziert man zum Beispiel schneller mit 320, indem man erst das Register kopiert, dann das eine Register um 8 bits schiebt (Multiplikation mit 256) und das andere Register um 6 bits schiebt (Multiplikation mit 64) und dann die beiden Register addiert. Des Weiteren fällt beim Schieben das herausgefallene Bit dabei nicht weg, sondern meist in ein Flag des Flag-Registers und kann dann weiterverarbeitet werden. Man unterscheidet beim Schieben das logische und das arithmetische Schieben. Beim arithmetischen Schieben bleiben dabei positive Zahlen positiv und negative Zahlen negativ. Dazu wird das höchstwertige Bit nicht verändert.

Multiplikation von Binärzahlen

Die Multiplikation zweier Binärzahlen erfolgt durch Verschieben und Addieren (z. B. durch den Booth-Algorithmus). In Mikroprozessoren wird dies durch Schieberegister erreicht. Es wird also ein Datensignal weitergeschoben. Ist z. B. ein Signalzustand „high“ vorhanden, so wird dieser an das nächste Bit weitergeschoben.

Verwendung als Puffer

Zur Filterung von digitalisierten Signalen puffert ein Signalprozessor eine feste Zahl von Werten. Dies kann in Schieberegistern erfolgen.

Erzeugung von Pseudozufallszahlen

Zur Erzeugung von Pseudozufallszahlen können linear rückgekoppelte Schieberegister verwendet werden.

Zyklische Redundanzprüfung

Die zyklische Redundanzprüfung (englisch cyclic redundancy check, CRC) kann mit einem durch Exklusiv-Oder-Gatter rückgekoppelten Schieberegister in Hardware ausgeführt werden.

Bausteine

In der folgenden Tabelle sind beispielhaft einige handelsübliche Schieberegister aufgelistet:

| Wortbreite | Logikfamilie | Beschreibung | ||

|---|---|---|---|---|

| TTL | ECL | CMOS | ||

| 4 Bit | 74LS194A | 10141 | 40194 | in/out serial/parallel |

| 8 Bit | 74LS164 74LS299 | 74HC595 4014 | serial in parallel out parallel in serial out | |

| 16 Bit | 74LS673 | 4006 | ||

| 8×1…16 Bit | Am29525 | |||

Siehe auch

Literatur

- Ulrich Tietze, Christoph Schenk: Halbleiter-Schaltungstechnik. 12. Auflage. Springer, Heidelberg 2002, ISBN 3-540-42849-6.