Emittergekoppelte Logik

Emittergekoppelte Logik (englisch emitter coupled logic, ECL) bezeichnet elektrische Schaltungen für Logikgatter in der Digitaltechnik. Als aktives Bauelement wird in diesen Schaltungen, wie bei der Transistor-Transistor-Logik, der Bipolartransistor verwendet. Allerdings ist die ECL-Technik wesentlich schneller, d. h., sie weist kürzere Gatterlaufzeiten auf. Nachteilig ist die hohe Verlustleistung und die Notwendigkeit einer positiven sowie negativen Versorgungsspannung. Eine Erweiterung, mit geringerer Verlustleistung und welche nur mit einer positiven Versorgungsspannung auskommt ist die Positive emitter-coupled logic (PECL). Eine leistungsarme Variante der PECL mit niedriger Versorgungsspannung im Bereich unter 3,3 V stellt LVPECL (Low Voltage Positive Emitter Coupled Logic) dar.[1]

Aufbau

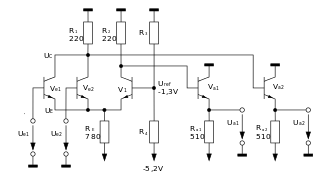

ECL-Gatter werden üblicherweise mit negativer Betriebsspannung betrieben. Das Grundelement einer ECL-Schaltung ist ein Differenzverstärker. Mehrere Transistoren sind über den Emitteranschluss miteinander verbunden und gemeinsam über eine Konstantstromquelle geführt. In der Abbildung wird der Differenzverstärker aus den Eingangstransistoren Ve1 und Ve2 und dem Transistor V1 gebildet. Die Anzahl der Transistoren für die Eingänge ist schaltungsabhängig und kann bei Bedarf erweitert werden. An der Basis von V1 wird über einen Spannungsteiler – bestehend aus den Widerständen R3 und R4 – eine konstante Spannung (Uref) angelegt. Wenn die Eingangsspannungen Ue1 und Ue2 einen Low-Pegel aufweisen, sperren die Transistoren Ve1 und Ve2. Dadurch fließt der Emitterstrom über den Transistor V1 und bewirkt somit einen Spannungsabfall an dem Widerstand R2, wodurch der Transistor Va1 angesteuert wird. Dadurch geht Ua1 auf den Low-Pegel und Ua2 auf den High-Pegel. Somit ist in positiver Logik der Ausgang mit Ua1 der Ausgang einer Oder-Verknüpfung und der Ausgang mit Ua2 der Ausgang einer NOR-Verknüpfung.

Die Verstärkung pro Differenzstufe liegt im, für Digitalschaltungen üblichen, Bereich von 30-fach, und ist durch die Höhe der Betriebsspannung begrenzt. Dadurch kann es bei langsamen Eingangsflanken, da die Logik ja immer im linearen Bereich bleibt, zu parasitären Schwingungen kommen. Es sind dafür aber auch Hochfrequenzverstärker, Oszillatoren (> 1 GHz), Leitungsempfänger und Komparatorschaltungen mit extremen Datenraten möglich.

Die ECL-Familie gehört zu den schnellsten erhältlichen Logikfamilien. Dies wird erreicht, da (anders als zum Beispiel bei der Transistor-Transistor-Logik) im normalen Betriebszustand kein Transistor in Sättigung geht. Mit ECL-Schaltungen können Verzögerungszeiten von < 200 ps erreicht werden, womit ECL-Schaltungen schneller sind als Schottky-TTL-Schaltungen, die ebenfalls nicht in Sättigung gehen. Der Unterschied ist dadurch begründet, dass die Kollektor-Emitter-Spannung an den leitenden Transistoren mit > 0,6 V höher ist, wodurch sich nicht nur ein größerer Abstand zur Sättigung, sondern auch eine Reduzierung der Kollektor-Basis-Sperrschichtkapazität ergibt. Eine weitere Geschwindigkeitssteigerung ergibt sich durch die kleinen Signal-Amplituden beim Umschalten von nur 0,8 V. Dadurch werden die Sperrschichtkapazitäten schnell umgeladen. Der niedrige Ausgangswiderstand ra der Emitterfolger beschleunigt ebenfalls die Geschwindigkeit. Der Ausgangswiderstand ergibt sich aus dem Zusammenhang der Kollektorschaltung:

Zudem fließt ein nahezu konstanter Strom durch die Schaltung. Es treten keine starken Stromspitzen wie bei anderen Logikfamilien auf.

Verglichen mit anderen Logikschaltungen ist die Leistungsaufnahme sehr groß wenn das Gatter nicht schaltet. CMOS hat aber den Vorteil, dass sie sich billig integrieren lässt und die fortschreitende Miniaturisierung leichter realisieren lässt.

Dimensionierung

Für den Fall, dass der Transistor V1 sperrt, tritt am Widerstand R2 ein Spannungsabfall von etwa 0,2 V auf, welcher durch den Strom an der Basis über den Transistor Va1 verursacht wird. Für die Spannung Ua2 am Emitter des Transistors Va2 ergibt sich über die Gleichungen des Differenzverstärkers ein elektrisches Potential von etwa −0,9 V, was den High-Pegel darstellt. Wird dieser High-Pegel an einem der Eingänge angelegt, ergibt sich für das elektrische Potential UE:

Damit die Transistoren am Eingang nicht in Sättigung kommen, soll die Kollektor-Emitter-Spannung nicht unter 0,6 V kommen. Daraus folgt das minimale Kollektorpotential:

Deshalb wird der Low-Pegel mit −1,7 V gewählt. Nun muss die Referenzspannung Uref so gewählt werden, dass die Eingangstransistoren bei einer High-Eingangsspannung von −0,9 V leitend werden und bei einer Low-Eingangsspannung von −1,7 V sperren. Dies wird erreicht, indem man Uref auf einen Wert genau zwischen diesen Werten legt:

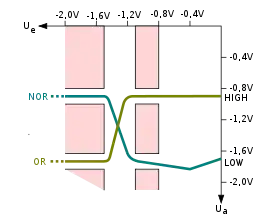

Bei dem höchstzulässigen Eingangs-Low-Pegel von ULow,max = −1,5 V muss am NOR-Ausgang ein High-Pegel von mindestens Ua2 = −1,0 V anliegen. Beim am niedrigsten zulässigen Eingangs-High-Pegel von UHigh,min = −1,1 V darf der Low-Pegel am Ausgang maximal −1,6 V aufweisen.

Im Gegensatz zu den anderen Logikfamilien ist die Eingangsspannung im High-Zugang nach oben hin stark begrenzt und darf −0,8 V nicht überschreiten, damit der Eingangstransistor nicht in Sättigung kommt. In der Übertragungskennlinie macht sich dies als Knick bei etwa −0,4 V am NOR-Ausgang bemerkbar. Bei weiterer Spannungserhöhung am Eingang sinkt aufgrund der Sättigung des Eingangstransistors das Potential an dessen Kollektor und Emitter (UC und UE), wodurch die Spannung Ua2 am Ausgang steigt.

Aus der Kennlinie ist ersichtlich, dass die logischen Pegel näher am Nullpotential liegen als an der negativen Betriebsspannung. Zudem ist die Größe der Betriebsspannung für die Logikpegel nicht weiter relevant, da diese nur über die Basis-Emitter-Spannung der Emitterfolger festgelegt wird. Würde man den negativen Pegel als Bezugspotential festlegen, würde sie die Pegel überlagern, was aufgrund der niedrigen Pegel keinen zuverlässigen Betrieb erlauben würde.

Die Verlustleistung eines einzelnen Gatters des Typs MC10xxx beträgt 25 mW. Zusätzlich tritt eine Verlustleistung an den Emitterwiderständen auf, welche bei einer mittleren Ausgangsspannung von −1,3 V und 510 Ω nochmals je 30 mW ausmacht. Dieses ist mehr als das komplette Gatter verbraucht. Emitterwiderstände werden daher nur bei verwendeten Gattern angeschlossen, weshalb diese nicht im IC-Gehäuse untergebracht werden. Die Verlustleistung an den Emitterwiderständen lässt sich auf etwa 10 mW reduzieren, wenn die Betriebsspannung auf −2 V reduziert wird und die Widerstände nur 50 Ω groß sind. Allerdings muss die Spannung in der Stromversorgung effizient (d. h. mit hohem Wirkungsgrad) erzeugt werden, da sich sonst die Verlustleistung lediglich von der Schaltung in die Versorgung verlagert. Die −2 V werden daher nicht mit einem Längsregler aus den −5,2 V erzeugt. Der zusätzlich notwendige Aufwand in der Versorgung ist jedoch nur bei vielen ECL-Gattern sinnvoll.

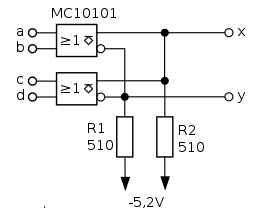

Wired-OR

Durch die Parallelschaltung von ECL-Ausgängen kann man, aufgrund der Open-Emitter-Ausgänge, vergleichbar dem Wired-AND bei Open-Collector-Ausgängen an einer TTL-Schaltung, eine logische ODER-Verknüpfung erreichen. Der Vorteil dieser Verknüpfung ist, dass man sich neben bzw. aufgrund der Einsparung des Gatters Verlustleistung und Latenzzeit einspart.

Den Aufbau der Schaltung zeigt die nebenstehende Abbildung. Durch die Verdrahtung der OR- und NOR-Ausgänge ergibt sich der Zusammenhang:

Anwendung

Aufgrund ihrer hohen Leistungsaufnahme sind ECL-Gatter nicht für VLSI-Schaltungen, also extrem hohe Integration geeignet. Sie werden jedoch gezielt dort eingesetzt, wo es auf extrem kurze Schaltzeiten und/oder konstante Stromaufnahme bei häufigen Gatterwechseln ankommt, also beispielsweise in einer besonders schnellen ALU eines Mikroprozessors. Allerdings wird die ECL-Technik in einigen Bereichen zunehmend von der immer besser werdenden CMOS-Technik abgelöst.

Ein weiteres Anwendungsgebiet für ECL-Technik sind Bustreiber für extrem schnelle differentielle Signalübertragung (vgl. Symmetrische Signalübertragung und LVDS).

Siehe auch

- Diode-Transistor-Logik (DTL)

- Widerstands-Transistor-Logik (RTL)

- Langsame störsichere Logik (LSL)

Einzelnachweise

- Introduction to LVDS, PECL, and CML (HFAN-1.0). (PDF) Maxim Integrated Circuits, April 2008, abgerufen am 4. November 2020.