Open-Collector-Ausgang

Der Open-Collector-Ausgang (OC) (zu deutsch „offener Kollektor“, auch „unbeschalteter Kollektor“) ist ein Ausgang einer integrierten Schaltung.

Je nach Schaltzustand ist der OC entweder hochohmig, oder er ist niederohmig mit Masse verbunden.

Ein OC wird mit einem Bipolartransistor mit freiem Kollektor-Ausgang realisiert und dient meist dazu, den Anschluss an ein höheres Spannungsniveau zu erlauben oder die logischen Verknüpfungen UND (engl. AND) und ODER (eng. OR) als sogenannte Wired-AND- und Wired-OR-Verknüpfung in Bus-Systemen wie dem I²C-Bus oder von mehreren Chips gemeinsam benutzte Signalleitungen (z. B. Interrupt) zu ermöglichen.

Da in integrierten Schaltungen zunehmend Feldeffekttransistoren eingesetzt werden, die statt eines Kollektor-Anschlusses einen sogenannten Drain-Anschluss aufweisen, wird dieser Ausgang auch als Open-Drain-Ausgang bezeichnet.

Erklärung

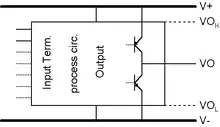

Man kann das Innenleben eines analogen oder digitalen ICs im Allgemeinen in Eingangsanschlüsse, Schaltlogik und Ausgangsanschluss (Ausgangsanschlüsse) aufteilen. In den allermeisten Fällen wird am Ausgang ein Spannungsniveau zwischen VOL und VOH eingestellt. Bei analogen ICs sind auch beliebige Zwischenwerte erlaubt, bei digitalen ICs wird durch die interne Schaltlogik erzwungen, dass am Ausgang ein „Low,0“ (VOL) oder „High,1“ (VOH) anliegt. Zum Verständnis ist wichtig, dass bei der gezeigten Ausgangsbeschaltung (die durch Emitterfolger, Kurzschlusssicherungen und andere Variationen vom gezeigten Prinzip abweichen kann) das Ausgangsspannungsniveau immer zwischen VOL und VOH liegt und nicht tiefer oder höher sein kann. Je nach Schaltung kann VOL gleich V- und VOH gleich V+ sein, so dass, vereinfachend gesagt, die Ausgangsspannung VO zwischen V- und V+ liegt. Werden beide Grenzen erreicht, dann wird von Rail-to-Rail-Technik gesprochen, weil im Schaltplan V- und V+ wie die Schienen eines Eisenbahngleises aussehen.

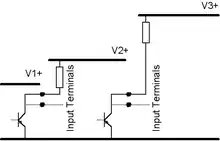

Es kommt nun vor, dass in einer elektronischen Schaltung mit gemeinsamer Masse und unterschiedlichen V+-Niveaus gearbeitet werden muss. Ein typisches Beispiel ist die Vermengung von analogen Signalaufbereitungen mit einem beliebigen V+-Niveau und Verarbeitung der Signale auf Mikrocontrollern, bei denen V+ fest auf +5 V liegen muss. Oder Ausgänge von digitalen Verarbeitungen müssen auf Spannungsniveaus größer oder kleiner als +5 V gebracht werden. Diese sind durch die oben liegenden unterschiedlichen V+-Linien im nebenstehenden Bild angedeutet. Während ein Weiterreichen von analogen Spannungsniveaus von links nach rechts noch unproblematisch sein kann (+3,635 V sind immer +3,635 V), so sieht es mit der digitalen Information „0“ und „1“ schon viel kritischer aus, weil in der Mitte „1“ z. B. bei +4,8 V liegt, was im rechten Teil, mit einer V+-Spannung von z. B. 20 V als „0“ interpretiert wird, da +4,8 V deutlich unter 0,5 · 20 V = +10 V liegt.

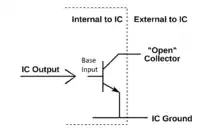

Das Bindeglied zwischen den Komponenten eines Niveaus zum anderen sind Open-Collector-Ausgänge, bei denen, wie gezeigt, der Kollektor eines Transistors ohne weitere innere Beschaltung (engl.: open = offen) nach außen an einen IC-Anschluss geführt ist. Er verhält sich deshalb nach außen wie ein Auf-Zu-Schalter (wobei nicht definiert ist, welchen logischen Zuständen Auf und Zu zugeordnet sind). Im gezeigten Beispiel werden Widerstände, die an das V+-Niveau der „Empfangskomponente“ angeschlossen sind, vom Open-Collector-Transistor im eingeschalteten Zustand gegen Masse geschaltet, d. h. der Eingang der Empfangskomponente sieht eine binäre „0“. Wird der Open-Collector-Transistor nicht angesteuert, d. h. er ist nicht leitend, wird das Niveau auf V+ der Eingangskomponente gezogen (vorausgesetzt, dieser Widerstand ist klein gegenüber dem Eingangswiderstand). Der Eingang sieht also eine binäre „1“. Deshalb heißen diese Widerstände auch Pull-up-Widerstände. Diese sind bei den meisten Standard-ICs nicht implementiert, sie müssen also extern bereitgestellt werden; es gibt aber Mikrocontroller, bei denen sich einzelne Ports als Eingänge mit integriertem Pull-up-Widerstand konfigurieren lassen.

Open-Collector-Anschlüsse können auch Eigenschaften aufweisen, die den restlichen Transistoren eines ICs fehlen. Ein klassisches Beispiel sind Treibertransistoren für Ziffernanzeigen, die z. B. mit bis zu 30 V beaufschlagt werden können, obwohl die ICs als Mitglieder der 74er-Reihe der digitalen Standard-ICs nur für V+ = 5 V zugelassen sind. Der „Discharge“ (=Entladungs)-Anschluss des berühmten Timer-ICs NE555 ist ein Open-Collector-Anschluss mit einer recht hohen Strombelastbarkeit.

Digitale ICs und Verwendung des OCs

Der Open-Collector-Ausgang ist einer von fünf möglichen Ausgangstypen (außerdem Totem-Pole, Tri-state, Komplementär-Ausgang und Open-Emitter-Ausgang) für digitale integrierte Schaltungen. Dabei wird der Kollektorwiderstand der Ausgangsendstufe weggelassen, so dass man mehrere Ausgänge zu einem Bus zusammensetzen kann.

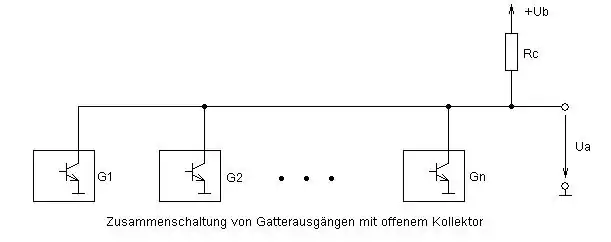

Es können durchaus Aufgabenstellungen auftreten, bei denen viele Gatter ausgangsseitig miteinander verknüpft werden müssen. Wenn z. B. 25 Gatterausgänge durch ein ODER-Gatter zusammenzufassen sind, so müsste man 25 Leitungen zu einem ODER-Gatter mit 25 Eingängen führen. Das ist nicht nur sehr aufwändig, solche Gatter sind am Markt auch nicht verfügbar. Man könnte dieses Problem durch kaskadierte ODER-Gatter lösen, bekäme dann jedoch auch unterschiedliche Signallaufzeiten.

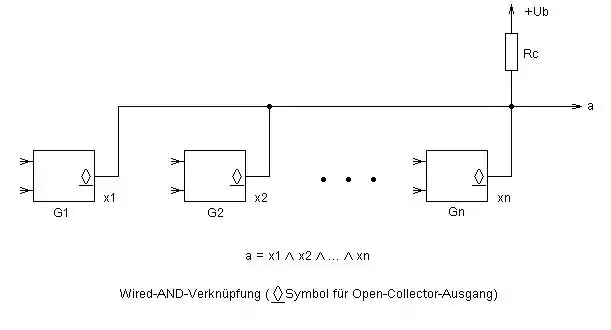

Besser verwendet man hier Gatter mit offenem Kollektorausgang. Diese besitzen einen Bipolartransistor am Ausgang, wobei der Emitter an Masse (engl. ground) liegt und der Kollektorausgang unbeschaltet an den Ausgang herausgeführt ist. Solche Ausgänge kann man nun ohne weiteres parallel schalten und mit einem gemeinsamen Kollektorwiderstand an V+ beschalten.

Die Ausgangsspannung Ua befindet sich bei positiver Logik nur dann im HIGH-Zustand, wenn alle angeschlossenen Gatterausgänge ebenfalls High sind, d. h., alle Ausgangsstufen sperren. Andererseits erkennt man, dass die Ausgangsspannung in den LOW-Zustand geht, wenn auch nur ein Ausgang sich im LOW-Zustand befindet. Damit ergibt sich für positive Logik eine UND-Verknüpfung der Ausgänge.

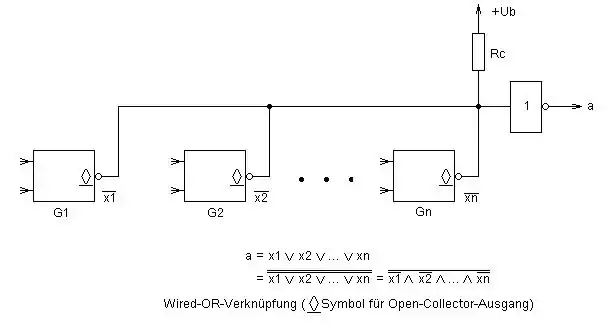

Mit dieser Open-Collector-Schaltungstechnik lässt sich auch eine ODER-Verknüpfung realisieren, indem man die negierten Ausgänge der Gatter genauso mit ihren offenen Kollektoren zusammenschaltet und anschließend negiert. Nach de Morgan gilt:

Eine entsprechende Schaltung zeigt:

Man erkennt, dass die UND-Verknüpfung der negierten Gatterausgänge mit nachfolgender Negation eine ODER-Verknüpfung liefert. WIRED-AND- und WIRED-OR-Strukturen werden z. B. bei der Implementierung von „programmable logic arrays“ (PLA) eingesetzt.

Symbole nach IEC-Norm

Die Raute beschreibt den hochohmigen Ausgang und der Strich die niederohmige Verbindung vom Pegel zum Ausgang. Deren Anordnung oben bzw. unten zeigt welcher Zustand an welchem Pegel liegt. Ist nun also die Raute über dem waagrechten Strich, so ist der H-Pegel hochohmig (keine Spannung liegt an) bzw. der L-Pegel (Masse) direkt mit dem Ausgang verbunden.

| Symbol | Beschreibung |

|---|---|

| Allgemeines Zeichen für einen „offenen Ausgang“, z. B. den Open-Collector-Ausgang |

| Offener Ausgang H-Typ mit niederohmigem H-Pegel und hochohmigem L-Pegel Mit diesen Ausgängen sind Wired-OR-Verknüpfungen möglich. An die Wired-OR-Verknüpfung muss zusätzlich noch ein externer „Pull-down“-Widerstand geschaltet sein. |

| Offener Ausgang L-Typ mit hochohmigem H-Pegel und niederohmigem L-Pegel Mit diesen Ausgängen sind Wired-AND-Verknüpfungen möglich. An die Wired-AND-Verknüpfung muss zusätzlich noch ein externer „Pull-up“-Widerstand geschaltet sein. |

Literatur

- Gerhard H. Schildt: Einführung in die Technische Informatik. Springer, Wien; New York 2003, ISBN 3-211-83853-8.