Wired-OR-Verknüpfung

Eine Wired-OR-Verknüpfung (englisch für verdrahtetes ODER), selten auch Phantom-OR-Verknüpfung genannt, kommt in der digitalen Schaltungstechnik vor, wenn zwei oder mehrere Ausgänge so miteinander verbunden werden, dass die Schaltung wie ein Oder-Gatter wirkt. Für diese Verknüpfung ist neben den eigentlichen Logikbauelementen bis auf einen Widerstand keine zusätzliche Elektronik nötig. Beim Transistor in der Ausgangsstufe in CMOS-Technologie sind Open-Drain-Ausgänge erforderlich. Bei Transistoren in Bipolar-Technologie sind dann Open-Collector-Ausgänge erforderlich.

Allgemein wird diese Art der Logikverknüpfung auch als verdrahtete Logik (oder engl. als wired logic) bezeichnet. Direkt mit diesem Schaltungsaufbau ist die Wired-AND-Technologie verwandt.

Digitale Bauelemente in Standard-Technologie

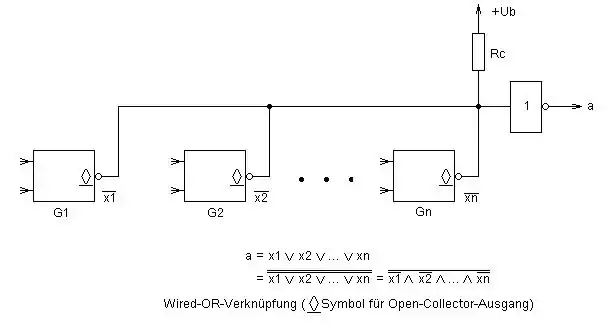

Eine Wired-OR-Verknüpfung lässt sich in positiver Logik aus einer Wired-AND-Verknüpfung mittels der Umformungsregeln nach den de Morganschen Gesetzen realisieren, wie in nebenstehender Abbildung skizziert. Dabei werden alle Eingänge und der Ausgang invertiert. Die am Widerstand zusammen geschalteten invertierten Eingangssignale stellen dann eine logische UND-Verknüpfung dar.

Aus technischer Sicht gesehen hat die Wired-OR-Verknüpfung gegenüber Logikbauelementen mit Standard-Ausgangsstufen einige Nachteile. Mit diesem Schaltungsaufbau ist die maximal zu erreichbare Taktfrequenz deutlich geringer als bei der von Standard-Logikbauelementen. Der Ausgangstransistor im Gatter muss je nach Logikzustand entweder komplett leitfähig sein (damit ein sauberer L-Pegel erreicht werden kann) oder muss komplett gesperrt werden (damit ein sauberer H-Pegel erreicht werden kann). Hierzu müssen die Transistoren stark übersteuert werden, was bei Umschaltvorgängen die maximal erreichbare Taktrate herabsetzt.

Weiterhin ist die Steilheit der Signalflanken bei dieser Schaltungsart begrenzt. Bei Umschaltungen von den H-Pegel in den L-Pegel kann der Schalttransistor im Gatter relativ schnell schalten, da der On-Widerstand des leitenden Transistors relativ gering ist und somit die parasitären Kondensatoren des Schaltungsaufbaus relativ schnell umladen kann. Anders verhält es sich beim Umschalten von den L-Pegel in den H-Pegel. In diesem Fall sind die Schalttransistoren gesperrt. Die Umladung der parasitären Kondensatoren muss in diesem Fall durch den Widerstand erfolgen. Dieser ist aber im Vergleich zum On-Widerstand der Transistoren deutlich größer und bewirkt daher, dass der Flankenanstieg des Ausgangssignals beim Umschalten von L nach H im Vergleich zum Umschaltvorgang von H nach L deutlich langsamer ist. Aufgrund der unterschiedlichen Flankenanstiegsgeschwindigkeit des Ausgangssignals ist dringend zu empfehlen, dass ein Bauelement mit einem Schmitt-Triggereingang nachgeschaltet wird. Zusätzliche Bauelemente haben aber den weiteren Nachteil, dass zusätzliche Signallaufzeiten entstehen.

Alle Transistoren haben selbst im gesperrten Zustand eine minimale Leitfähigkeit in Form von Kollektor-Emitter-Restströmen. Je größer die Anzahl von parallel geschalteten Transistoren ist, desto größer ist die Summe der Restströme. Diese Restströme fließen durch den Widerstand und können bei einem H-Pegel zu einer Verzerrung des Logikpegels führen. Aufgrund dieses Sachverhalts muss der Widerstand verhältnismäßig niederohmig sein muss, damit sich trotz der Parallelschaltung der Ausgänge von mehreren Gattern saubere Logikpegel einstellen können. Ein niederohmiger Widerstand hat aber einen höheren Stromverbrauch und somit eine höhere Verlustleistung der Schaltung zur Folge.

In der ingenieuersmäßigen Schaltungsentwicklung in Standardlogik findet die Wired-OR-Verknüpfung bei Neuentwicklungen praktisch kaum mehr Verwendung.

Digitale Bauelemente in ECL-Technologie

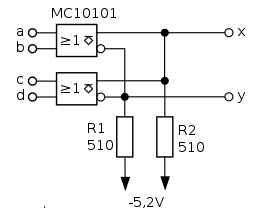

Eine andere Schaltungsvariante in der emittergekoppelten Logik (ECL) nutzt die direkte Möglichkeit durch Zusammenschalten von Open-Emitter-Ausgängen eine Wired-OR-Verknüpfung zu realisieren. Der Vorteil der direkten Verknüpfung ist, dass man sich Inverterstufen und die damit verbundenen zusätzlichen Durchlaufzeiten erspart. Aufgrund der differenziellen Signale bei der ECL-Technologie sind zwei Widerstände erforderlich. In der klassischen Transistor-Transistor-Logik sind für die direkte Realisierung einer Wired-OR-Verknüpfung zumindest zwei zusätzliche Dioden nach den Ausgangstreibern zusätzlich zu dem Widerstand nötig.

Bei der ECL-Technologie sind die beiden Arbeitswiderstände ein Teil des Schaltungsaufbaus. Die ECL-Technologie allgemein ist nur noch Spezialanwendungen vorbehalten.

Analoge Komparatoren mit digitalen Schaltausgängen

Bei analogen Komparatoren handelt es sich um Bauelemente, die entweder einen Spannungswert mit einer Referenzspannung oder zwei Spannungswerte miteinander vergleichen. Hierbei ist ein Vergleich auf größer, kleiner, innerhalb eines definierten Spannungsfensters oder außerhalb eines definierten Spannungsfensters möglich. Diese Komparatoren haben häufig digitale Ausgänge, die je nach Bauart auch als Open-Drain-oder Open-Collector-Ausgänge ausgeführt sein können. Wenn mehrere Komparatoren in dieser Technologie miteinander logisch verknüpft werden müssen, kann dies ebenfalls in der Wired-OR-Technologie erfolgen. Bei reinen Analogschaltungen kann durch Wired-OR-Verknüpfungen je nach Schaltungsaufbau komplett auf digitale Logikbauelemente verzichtet werden.

Literatur

- Ulrich Tietze, Christoph Schenk: Halbleiter-Schaltungstechnik. 12. Auflage. Springer, 2002, ISBN 3-540-42849-6.

- Klaus Beuth: Digitaltechnik. 10. Auflage. Vogel, 1998, ISBN 3-8023-1755-6.

- Manfred Seifart, HelmutBeikirch: Digitale Schaltungen. 5. Auflage. Technik, 1998, ISBN 3-341-01198-6.