Volladdierer

Ein Volladdierer (englisch full adder) ist ein Schaltnetz, das üblicherweise als digitale Schaltung realisiert wird. Es besteht aus drei Eingängen (, und ) und zwei Ausgängen ( und ). Mit einem Volladdierer kann man drei einstellige Binärzahlen addieren. Dabei liefert der Ausgang (engl. sum – Summe) die niederwertige Stelle des Ergebnisses, der Ausgang (engl. carry (output) – Übertrag (Ausgang)) die höherwertige. Die Bezeichner und legen hierbei eine Möglichkeit zur Übertragsbehandlung in Addiernetzen nahe.

Die folgende Wahrheitstabelle zeigt die Funktionsweise eines Volladdierers:

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Daraus ergeben sich folgende Gleichungen, indem man zunächst die disjunktive Normalform aus den Wahrheitswerten der Tabelle bildet und dann vereinfacht:

und

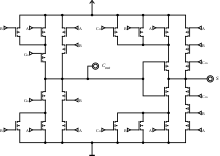

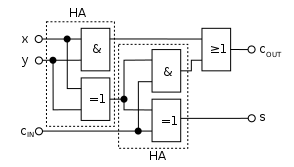

Die linke Abbildung zeigt den Aufbau eines Volladdierers mittels Halbaddierern und einem Oder-Gatter.

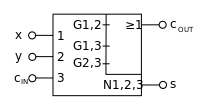

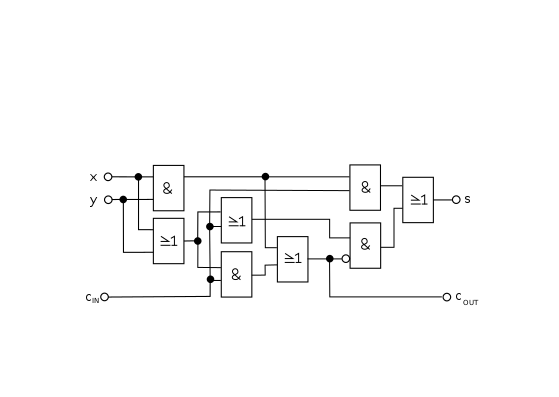

Aufbau eines Volladdierers mittels zweier Halbaddierer und eines Oder-Gatters nach DIN 40900 |

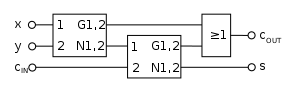

Aufbau eines Volladdierers mit zwei UND-, zwei XOR- und einem ODER-Gatter nach DIN 40900 |

Die rechte Abbildung zeigt ebenfalls den Aufbau eines Volladdierers, wobei die Halbaddierer jeweils in ein Und-Gatter und ein Exklusiv-Oder-Gatter aufgetrennt wurden. Hierbei ist zu beachten, dass in beiden Abbildungen die Summenausgänge jeweils unten und die Übertragsausgänge der Halbaddierer jeweils oben dargestellt sind.

- Optimiert man den Ausdruck für den Volladdierer weiter, ohne den Carry-Pfad zu verlangsamen ergeben sich weitere Vereinfachungen:

Der Volladdierer wird zum Aufbau von Addierwerken und Multiplizierern verwendet, oft mit einem Halbaddierer am Anfang der Übertragkette.

Bei der Invertierung aller Eingänge eines Volladdierers invertieren sich alle Ausgänge, dies kann zur Laufzeitoptimierung von Addierwerken verwendet werden, indem auf die Invertierung von verzichtet wird.[1]

Literatur

- Ulrich Tietze, Christoph Schenk: Halbleiter-Schaltungstechnik. 12. Auflage. Springer, 2002, ISBN 3-540-42849-6.

Einzelnachweise

- P. Fischer: Einfache Schaltungsblöcke. Universität Heidelberg. Abgerufen am 5. September 2021.