High Bandwidth Memory

High Bandwidth Memory (engl. kurz: HBM, deutsch Speicher mit hoher Bandbreite) ist eine von AMD zusammen mit SK Hynix entwickelte Speicherschnittstelle, um in einem Computer den Arbeitsspeicher mit hoher Übertragungsrate an einen Grafik- oder Hauptprozessor anzubinden.

Technik

| Typ | Release | Takt (GHz) | Stack | pro Stack (1024 bit) | |

|---|---|---|---|---|---|

| Kapazität (230 Byte) | Datenrate (GByte/s) | ||||

| HBM 1 | Okt. 2013 | 0,5 | 8×128 bit | 4 | 128 |

| HBM 2 | Jan. 2016 | 1,0…1,2 | 8 | 256…307 | |

| HBM 2E | Aug. 2019 | 1,8 | 16 | 461 | |

| HBM 3 | Okt. 2021 | 3,2 | 16×64 bit | 24 | 819 |

HBM 1

HBM 1 wurde im Oktober 2013 von der JEDEC als US-Industrie-Standard angenommen.[1]

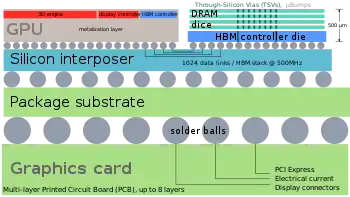

HBM ist eine Speichertechnologie, die es ermöglicht, mehrere Dies übereinander zu stapeln und parallel anzubinden (vgl. 3D-Integration). Die Schnittstelle wird zwischen Speicher und CPUs, GPUs und FPGAs verwendet.[2][3]

In der ersten Anwendung wurden 4 DRAM-Module zu je 1 GB gestapelt. Dieser Stapel stellt durch einen sogenannten „Interposer“ eine schnellere Verbindung zur CPU oder GPU her, als der bisher als Standard verbaute GDDR5-Speicher. Die Busbreite ist hierbei 1024 Datenleitungen pro Stapel. Der Speicher ist mit 500 MHz getaktet, Daten werden bei steigender und fallender Flanke übertragen (DDR). Bis zu vier dieser HBM-Stapel werden zusammen mit einer CPU oder GPU auf den Interposer gebumpt und diese Gesamt-Einheit mit einer Platine verbunden. Aufgrund der großen Busbreite erreicht der Gesamt-Datendurchsatz ein halbes Terabyte pro Sekunde.[4]

Obwohl diese HBM-Stapel nicht physisch in die CPU oder GPU integriert sind, sind sie dort über den Interposer mit extrem kurzen Leitungswegen schnell angebunden, so dass sich die Eigenschaften des HBM kaum von auf dem Chip integriertem RAM unterscheiden.

HBM-Speicher weist zudem eine geringere Leistungsaufnahme als GDDR5 auf. AMD gibt an, dass HBM mehr als die dreifache Speicherbandbreite pro Watt bietet.

HBM benötigt deutlich weniger Platinenfläche als GDDR5, was vorteilhaft für den Bau von Notebooks oder Tablets mit hoher Grafikleistung sein kann.[5] Die sehr enge Positionierung am Grafikprozessor erlaubt ferner, Grafikchip und RAM mit einem einzigen, relativ kleinen Kühlkörper zu überdecken. Jedoch können vor allem die untenliegenden Dies auch nur eingeschränkt Wärme ableiten.

HBM 2

Am 12. Januar 2016 wurde HBM 2 als JESD235a von der JEDEC angenommen.[6]

HBM 2 erlaubt es, bis zu 8 Dies aufeinander zu stapeln, und verdoppelt den Speicherdurchsatz auf bis zu 100 GB/s pro Die-Stapel. Die Größe der Stapelspeicher kann zwischen 1 und 8 GiB liegen, womit ein maximaler Ausbau auf 32 GiB möglich wird. Sowohl SK Hynix als auch Samsung haben 4GiB-Stapel auf den Markt gebracht.

Verwendung findet HBM2 seit 2016 in Nvidia Tesla- und seit 2017 in Nvidia-Quadro-Grafikkarten, seit Mitte 2017 in der AMD-Radeon-Vega-Serie.

HBM 2E

Vorgestellt am 13. August 2019 verdoppelt sich die max. Kapazität pro Stapel, die Datenrate erhöht sich um 50 Prozent.[7] Die Speicherhersteller Samsung, SK Hynix und Micron hatten HBM 2E als Zwischenschritt eingeschoben, um die Kapazität zu verdoppeln und die Übertragungsrate ausgehend von 256 GByte/s bei HBM2 zu erhöhen, ohne auf HBM3 warten zu müssen.[8]

HBM 3

HBM3 setzt genauso wie HBM, HBM2 und HBM2e auf 1024 Datenverbindungen pro Stack. Die zusätzliche Geschwindigkeit entsteht durch höhere Taktfrequenzen von 6,4 Gbit/s pro Pin. Die schnellsten HBM-2E-Stapel kamen noch auf 3,6 Gbit/s pro Pin beziehungsweise 461 GByte/s je Stack. Die HBM3-Spezifikation ermöglicht jetzt, 12 statt wie bisher maximal 8 SDRAM-Chips zu stapeln; Ein Stack überträgt jetzt 819 GByte/s und fasst bis zu 24 GByte. Im Oktober 2021 kündigte SK Hynix den ersten HBM-3-Speicher an.[8]

Geschichte

Die Entwicklung von HBM begann im Jahr 2008 bei AMD. Version 1 wurde offiziell im Jahr 2013 von der JEDEC verabschiedet, Version 2 im Jahr 2016.

Erstmals verbaut wurde HBM 1 auf den Grafikkarten Radeon R9 Fury, Radeon R9 Fury X[9] und der Radeon R9 Fury Nano der AMD-Radeon-R300-Serie.

Einzelnachweise

- JESD235: High Bandwidth Memory. 12. Oktober 2015.

- Wissolik, Zacher, Torza, Day: Alternatives to the DDR4 DIMM. (PDF) In: www.xilinx.com. Xilinx, 15. Juli 2019, abgerufen am 15. Juli 2020 (englisch).

- https://www.cs.utah.edu/thememoryforum/mike.pdf

- Christof Windeck: AMD Radeon R9 Fury × dank HBM-Speicher mit 512 GByte/s. In: Heise online. 16. Juni 2015. Abgerufen am 14. Januar 2016.

- First Radeon with High Bandwidth Memory will launch at E3 on June 16th. In: Digital Trends. 2. Juni 2015 (digitaltrends.com [abgerufen am 23. August 2017]).

- JESD235a: High Bandwidth Memory 2. 12. Januar 2016.

- Mark Mantel: HBM2E-Stapelspeicher: Hohe Transferraten und Kapazität für GPUs und FPGAs. In: Heise online. 13. August 2019. Abgerufen am 14. August 2019. Mark Mantel: HBM2E-Stapelspeicher: Hohe Transferraten und Kapazität für GPUs und FPGAs. In: heise online. 13. August 2019, abgerufen am 14. August 2019.

- Mark Mantel: Stapelspeicher HBM3: Schnellstes DRAM für Grafikkarten und Beschleuniger. In: Heise online. 20. Oktober 2021. Abgerufen am 22. Oktober 2021.

- http://www.grafikkarten-bewertung.de/produkt/sapphire-r9-fury-4gb-hbm-4096-bit-pci-e-hdmi-tripl/. Abgerufen am 5. November 2016.