Direct Digital Synthesis

Die Direct Digital Synthesis oder direkte digitale Synthese (kurz DDS) ist ein Verfahren in der digitalen Signalverarbeitung zur Erzeugung periodischer, bandbegrenzter Signale mit praktisch beliebig feiner Frequenzauflösung. Das Verfahren stellt heute neben der rational gebrochenen Phasenregelschleife die dominierende Methode zur Generierung von Signalen fein einstellbarer Frequenz dar und hat weite Verbreitung in der Nachrichten- und Messtechnik gefunden.

Der Begriff DDS bezeichnet in der technischen Umgangssprache auch integrierte Schaltkreise (IC), die die komplette Hardware eines Synthesizers nach dem DDS-Verfahren realisieren. Die weite Verbreitung solcher ICs hat wesentlich zum Erfolg des Verfahrens beigetragen.

Funktion

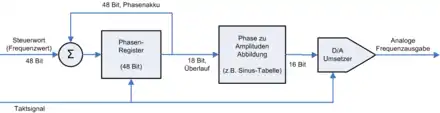

Die direkte digitale Synthese basiert auf einem digitalen Addierwerk, kombiniert mit einem Register samt Rückkopplung, das einen Speicher für die Phasenlage darstellt und in nebenstehender Abbildung dargestellt ist. Die angegebenen Bitbreiten in der Abbildung sind beispielhaft und verdeutlichen die in den einzelnen Stufen unterschiedlichen Wortbreiten.

Dieser sogenannte Phasenakkumulator addiert zyklisch, pro Taktschritt, den links zugeführten Eingabewert, der proportional zur ausgegebenen Frequenz ist. Der momentane Zählerstand entspricht dann einem Phasenwinkel, und ein Überlaufen des Phasenakkumulators (automatischer Rücksprung auf Null) entspricht dabei einem vollen Umlauf des Phasenzeigers von 2·π.

Der zu einem bestimmten Phasenwert gehörende Signalwert wird durch eine weitere Funktion gebildet, die einem Phasenwert einen Signalwert zuordnet. Ist beispielsweise ein sinusförmiger (harmonischer) Signalverlauf gewünscht, stellt dieser Block die Sinusfunktion dar. Die Abbildung kann bei kleinen Bitbreiten in der digitalen Schaltung in Form einer bereits im Voraus berechneten ROM-Tabelle erfolgen. Alternativ können die Ausgabewerte für einen sinusförmigen Signalverlauf auch zur Laufzeit mit Algorithmen wie dem CORDIC-Algorithmus in der Schaltung berechnet werden. Wird lediglich eine Sägezahnschwingung benötigt (beispielsweise für einen Synthesizer), so kann der Phasenwert direkt als Signalwert ausgegeben werden, da die Phase innerhalb jeder Periode linear ansteigt und dann auf Null zurückspringt. Eine Dreieckschwingung, die für einige Anwendungen einen Sinus ersetzen kann, lässt sich erzeugen, indem man den Phasenwert als vorzeichenbehaftete Binärzahl (Zweierkomplement) interpretiert und deren Absolutwert berechnet.

Das digitale Signal kann dann weiteren Stufen zur Verarbeitung zugeführt werden, beispielsweise für eine analoge Ausgabe dem in der Abbildung rechts außen dargestellten Digital-Analog-Umsetzer.

Die mit dem Verfahren erreichbare Frequenzauflösung hängt ausschließlich von der Wortbreite des Phasenakkumulators ab. Eine typische Wortbreite ist 32 bit, damit beträgt die Frequenzauflösung bei 100 MHz Systemtakt etwa 0,023 Hz bei einer maximalen Ausgangsfrequenz von theoretisch der halben Taktfrequenz (50 MHz).

Die Qualität des Ausgangssignals hängt im Wesentlichen von der Qualität des Taktgenerators, dessen möglichst geringem Jitter und der Genauigkeit des Digital-Analog-Umsetzers ab. Je höher die Frequenz (= kleinerer Teiler), desto gröber wird die Abtastung der Tabelle und desto wichtiger werden dem DA-Umsetzer nachgeschaltete Filter. In der Praxis ist ein Kompromiss zwischen der Bandbreite und der Genauigkeit zu schließen. Im Frequenzbereich unter 100 MHz lassen sich, mit Stand 2008, Sinussignale mit Nebenwellenabständen von ca. 80 dB realisieren. DDS-Schaltkreise mit integriertem D/A-Umsetzer sind heute mit Taktfrequenzen bis ca. 1000 MHz verfügbar (zum Beispiel AD9912).

Die Implementierung des DDS (ohne analogen Wandler) kann sowohl in einem FPGA, DSP oder auch ASIC erfolgen. Durch entsprechende funktionale Erweiterungen der DDS ist auch eine Winkelmodulation (Phasenrauschen) oder Amplitudenmodulation des Ausgangssignals realisierbar.

Literatur

- Bar-Giora Goldberg: Digital Frequency Synthesis Demystified – DDS and Fractional-N PLLs. LLH Technology Publishing, Eagle Rock VA 1999, ISBN 1-878707-47-7.

- Analog Devices: A Technical Tutorial on Digital Signal Synthesis. 1999 (analog.com [PDF; 902 kB] Firmenschrift).

- Michael Gaedtke: Messen mit der Soundkarte: Funktionsgenerator in DDS-Technik. 2006 (online – Tutorial).

Siehe auch

Weblinks

- AD9833 Datenblatt (PDF; 465 kB), engl. Eine DDS mit einer Bandbreite von 0 MHz bis 12,5 MHz und der Möglichkeit wahlweise Sinus-, Dreieck- oder Rechteckschwingungen ausgeben zu können.

- Direkte Digitale Synthese, Artikel zur Funktion und Realisierung einer DDS mit Mikrocontrollern und FPGAs.