Taktversatz

Der Taktversatz (engl. clock skew) ist ein Phänomen synchroner Schaltkreise und synchronen Datenübertragungsverfahren. Er beschreibt die Zeitdifferenz zwischen dem Eintreffen einer Taktflanke am ersten zu betrachtenden Element (z. B. einem Flipflop) und dem Zeitpunkt des Eintreffens an einem zweiten Element.

Je nach Auswahl kann dabei der Taktversatz positive oder negative Werte annehmen, die betragsmäßig größte Differenz beschreibt eine Grenze für die obere Taktfrequenz. Im Idealfall ist der Taktversatz null, was physikalisch nicht machbar ist. Bei realen synchronen Schaltkreisen liegt der Betrag des Taktversatz je nach Technologie im Bereich einiger 10 ns und kann durch besondere Maßnahmen bis auf einige Pikosekunden reduziert werden. Zur Minimierung wird das Taktsignal in synchronen Digitalschaltungen in eigenen Taktverteilungsnetz verteilt, die in der Struktur wie ein H-Baum aufgebaut sein können.[1] Weitere Möglichkeiten stellen Delay-Locked Loops dar, welche eine gezielte Phasenverschiebung im Taktsignal für bestimmte Schaltungsbereiche erlauben.[2]

Vorkommen in realen Schaltungen

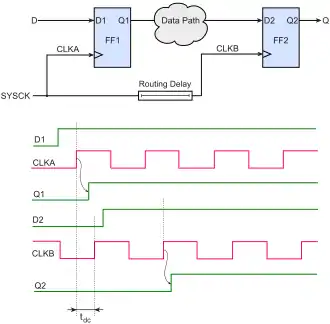

Zur Beschreibung dient nebenstehende einfachste synchrone Schaltung, die aus zwei hintereinander geschalteten D-Flipflops als Speicherelemente besteht. Jedes D-Flipflop übernimmt mit steigender Flanke den Zustand an seinem Eingang D und gibt diesen Wert an seinen Ausgang Q aus. Bei einer idealen Schaltung ohne Laufzeiten übernimmt das erste Flipflop den Zustand der Eingangsleitung D, mit der zweiten Taktflanke das zweite Flipflop.

Bei einer realen Schaltung treten zusätzliche Laufzeiten, sowohl durch die Flipflops als auch entlang der unterschiedlich langen Zuleitungen auf: Das Taktsignal ist am Punkt CLKB bei zweiten Flipflop gegenüber dem Taktsignal am Punkt CLKA durch die räumliche Ausdehnung zeitlich verschoben – diese Zeitdifferenz wird als Taktversatz tdc bezeichnet. Gemeinsam mit den Laufzeiten durch die Flipflops, im Zeitdiagramm als Pfeil eingezeichnet, und der Laufzeit entlang des Data Path, dieser stellt ein Schaltnetz dar, kann dies dazu führen, dass sich das Datensignal Q am Ausgang erst eine Taktperiode später ändert, als wenn die Laufzeit am Datenpfad entsprechend kürzer wäre. Dadurch entstehen folgende zu beachtende Zeitprobleme von synchronen Schaltungen, die beim Schaltungsentwurf durch die Wahl der Topologie bzw. Taktfrequenz vermieden werden müssen:

- Die Änderung des Datensignals am Eingang D2 kann durch entsprechende Zeiten in den Bereich der steigenden Taktflanke fallen. In diesem Fall werden die sogenannten Setup- und Hold-Zeiten des zweiten Flipflop verletzt. Die Setup- und Hold-Zeit beschreibt einen Sperrbereich kurz vor bzw. nach einer Taktflanke, in der der Eingang sich im Wert nicht ändern darf. Passiert dies trotzdem, können metastabile Zustände im Flipflop die Folge sein.

- Durch die Laufzeiten kann es, wie in der Abbildung dargestellt, zu einer zusätzlichen zeitlichen Verschiebung um eine Taktperiode kommen, was unter anderem in Schaltwerken, also Schaltungen mit Rückkopplungen, zu Folgeproblemen führen kann, da beispielsweise ungültige Zustände im Zustandsautomaten für eine Taktperiode auftreten.

Zur Vermeidung dieser zeitlichen Fehler werden bei der Entwicklung von synchronen Schaltkreisen spezielle Werkzeuge zur Timinganalyse eingesetzt, welche mittels der bekannten Technologieparameter des Halbleiterchips die Laufzeiten bestimmen und in dem konkreten Schaltungsdesign in der Netzliste mögliche dynamische Zustandsfehler erkennen können.

Einzelnachweise

- E. G. Friedman: Clock Distribution Networks in Synchronous Digital Integrated Circuits. Band 89, Nr. 5. Proceedings of the IEEE, 2001, S. 665–692, doi:10.1109/5.929649.

- S. Tam, D.L. Limaye und U.N. Desai: Clock Generation and Distribution for the 130-nm Itanium 2 Processor with 6-MB On-Die L3 Cache. In: IEEE Journal of Solid-State Circuits. Band 39, Nr. 4, 2004, S. 636–642, doi:10.1109/JSSC.2004.825121.