Metastabilität (digitale Schaltung)

Metastabilität ist eine meist unerwünschte Eigenschaft in der Digitaltechnik, bei deren Auftreten in digitalen Schaltungsteilen wie Flipflops diese für eine gewisse Zeit in undefinierten Zwischenzuständen zwischen den stabilen Zuständen verharren. Bei der üblichen binären Digitaltechnik sind metastabile Zustände durch Spannungszustände zwischen den beiden stabilen Spannungsniveaus für logisch-0 und logisch-1 gekennzeichnet. Diese Zwischenzustände können bei Nichtbeachtung der Metastabilitat zu unvorhergesehenen Fehlern und Ausfällen führen.

Beschreibung

Die einfachste Form einer digitalen Schaltung ist das RS-Flipflop. Diese rückgekoppelte Schaltung hat zwei stabile Zustände, logisch-0 (Reset-Zustand) und logisch-1 (Set-Zustand). Diese beiden stabilen Zustände werden durch zwei Spannungen nahe der unteren und nahe der oberen Betriebsspannung ausgedrückt. Bei einer kleinen Störung dieser stabilen Spannungsniveaus kehrt die Schaltung in den jeweiligen stabilen Zustand zurück – das macht den speichernden Effekt der Schaltung aus. Zusätzlich gibt es einen metastabilen Betriebsbereich. Dieser liegt in etwa in der Mitte der Betriebsspannung, wo das Betriebsverhalten nicht bestimmt ist.

Idealisiert könnte das RS-Flipflop in diesem metastabilen Bereich beliebig lange verharren. Durch kleine physikalische Störeffekte wie Rauschen wird dieser metastabile Zustand in Praxis in der überwiegenden Mehrzahl der Fälle meist innerhalb sehr kurzer Zeiten im Bereich weniger Nanosekunden, in einen der beiden stabilen Zustände kippen. Es lässt sich aber nur statistisch vorhersagen, nach welcher Zeit dieser Übergang zufällig in einen der beiden stabilen Zustände erfolgen wird.

Metastabilität bei Abtastung

Typische Problemfälle sind die Abtastung eines sich beliebig ändernden, also zeitlich nicht synchronisierten Signals mit einem taktflankengesteuerten D-Flipflop. D-Flipflops stellen in vielen digitalen Schaltungen wie FPGAs und ASICs die elementaren Speicherelemente dar: Mit aktiver Flanke des Taktsignals tastet das D-Flipflop den Zustand an seinen Eingang D ab, speichert diesen Zustand und gibt ihn bis zur nächsten aktiven Taktflanke an seinen Ausgang Q aus. Zur korrekten Funktion und Vermeidung von Metastabilität müssen dabei bestimmte Zeiten eingehalten werden: So darf sich das Eingangssignal D eine bestimmte kurze Zeitspanne vor und nach der aktiven Taktflanke nicht ändern, d. h. das Eingangssignal muss in diesem Zeitintervall der Abtastung konstant auf logisch-0 oder logisch-1 sein. In der englischsprachigen Fachliteratur werden diese Sperrzeiten als setup and hold time bezeichnet.

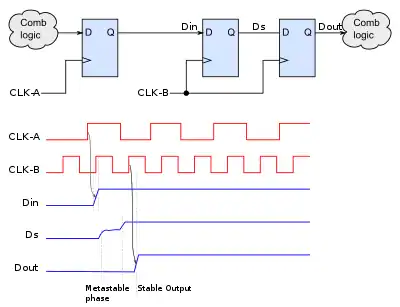

Bei externen zum Takt nicht synchronisierten Signalen, die dem D-Flipflop an seinem Eingang D zugeführt werden, ist diese Bedingung grundsätzlich nicht immer erfüllbar: Es kann zur Verletzung der Sperrzeit (Setup- und Hold-Zeit) kommen, gleichbedeutend mit einem unerlaubten Spannungsniveau zum Abtastzeitpunkt, womit das D-Flipflop in einen metastabilen Zustand fallen kann. Dieses Problem tritt auch auf, wenn ein digitales Signal zwischen zwei zueinander nicht synchronen Taktdomänen übertragen werden soll, wie in nebenstehender Abbildung mit dazugehörigen Zeitverläufen dargestellt: Das linke D-Flipflop wird mit dem Takt A (CLK-A) gesteuert, die anderen beiden Flipflops durch ein dazu asynchrones Taktsignal B (CLK-B).

Bei dem ersten D-Flipflop in der Taktdomäne B kann es zu bestimmten Zeiten, wenn die Signaländerung Din gerade zufällig zu einem Abtastzeitpunkt mit Taktsignal B zusammenfällt, zu einem metastabilen Zustand am Signal Ds kommen, im Zeitdiagramm als ungleichmäßiger Verlauf dargestellt. Dieser metastabile Zustand ist in vielen Fällen nach kurzer Zeit beendet, das Eingangsflipflop kippt dann zufällig in einen der beiden stabilen Zustände. Ändert sich das Eingangssignal nicht, ist spätestens nach einer Taktperiode der metastabile Zustand durch eine erneute und in diesem Fall stabile Abtastung beendet. Damit nachfolgende digitale Schaltungsteile durch den undefinierten Spannungsverlauf nicht in der Funktion beeinträchtigt werden, wird ein weiteres D-Flipflop nachgeschaltet, das vom selben Takt B gesteuert wird und einen stabilen Übergang am finalen Ausgang Dout ergibt. Dadurch kommt es durch die nacheinander geschaltete Doppelabtastung zu einer zusätzlichen Latenz von einer Taktperiode.

Wesentlich ist, dass sich die metastabile Situation durch keine wie auch immer geartete Maßnahme gänzlich vermeiden lässt. Jeder „Lösungsvorschlag“ zur absoluten Vermeidung beruht stets auf einem Denkfehler, der das Auftreten der Metastabilität an irgendeiner Stelle ignoriert. Durch das Hintereinanderschalten von mehreren Abtaststufen wie Flipflops kann lediglich die Auftrittswahrscheinlichkeit des metastabilen Zustandes beliebig stark reduziert werden. Beim oben gegebenen Beispiel mit dem zweiten D-Flipflop kann das Einhalten der Setup- und Hold-Zeiten des zweiten Flipflops genau dann nicht garantiert werden, wenn das erste Flipflop im metastabilen Zustand ist. Bei in den Jahren um 2010 marktüblichen Logikschaltungen wie in FPGAs liegt die Verweildauer im metastabilen Zustand mit einer Wahrscheinlichkeit von 99,9 % der Schaltvorgänge bei unter 1 ns. Damit ist es möglich, die Gesamtwahrscheinlichkeit für eine Fehlfunktion durch eine Abtastung von z. B. 10 ns auf irrelevante kleine Werte zu senken.

Literatur

- Steve Kilts: Advanced FPGA Design – Architecture, Implementation, and Optimization. Wiley-Interscience, 2007, ISBN 978-0-470-05437-6, Kapitel 6: Clock Domains.

- Randy H. Katz: Contemporary Logic Design. The Benjamin/Cummings Publishing Company, 1994, ISBN 0-8053-2703-7, 6.4: Metastability and Asynchronous Inputs.