Delay-Locked Loop

Bei einer Delay-Locked Loop (DLL) handelt es sich um eine elektronische Schaltung, die ähnlich wie eine Phasenregelschleife (PLL) aufgebaut ist. Der Hauptunterschied zur PLL ist das Fehlen des spannungsgesteuerten Oszillators, es wird nur das am Eingang anliegende Taktsignal zeitverzögert als Ausgangssignal verwendet. Zu diesem Zweck ist eine einstellbare Verzögerungskette vorgesehen, wovon sich auch der Name dieser Schaltung ableitet. Der Vorteil dieser Schleife gegenüber einer Phasenregelschleife liegt in dem geringeren schaltungstechnischen Aufwand.

Funktion

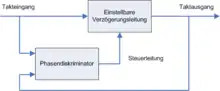

Von außen betrachtet kann die DLL aufgrund ihrer Schleife (Rückkopplung) wie eine zeitlich negative Verzögerung angesehen werden. Wesentlicher Bestandteil einer DLL ist eine variable Verzögerungskette, die über eine Kette von einzelnen elementaren Verzögerungsgliedern mit fixer Verzögerungszeit gebildet wird. Die Momentanverzögerung der gesamten Kette hängt von der Phasenlage zwischen Eingangs- und Ausgangssignal ab und wird über ein Steuersignal dynamisch im Betrieb eingestellt. Je nach Typ und Anwendung kann der dazu eingesetzte Phasendiskriminator auf minimalen Fehler vergleichen oder auf einen konfigurierbaren, von Null verschiedenen Phasenwinkel.

Analoge DLLs arbeiten mit folgenden zwei Typen als Verzögerungskette:

- Current-Starved Inverter

- Shunt-Capacitor Delay Stage (auch Capacitor-Loaded Inverter Delay Line)

In digitalen DLLs wirkt das vom Phasendiskriminator gebildete Steuersignal auf einen Multiplexer, welcher in diskreten Schritten den Phasenfehler minimiert. Am Ausgang dieses Multiplexers liegt dann das Ausgangssignal der DLL an. In praktisch realisierten DLLs werden zwischen Phasendiskriminator und Verzögerungskette zusätzliche Schleifenfilter eingesetzt, welche das dynamische Verhalten der Regelschleife beeinflussen.

Anwendungsbereiche

Eine DLL wird primär zur Einstellung der Phasenlage eines frei laufenden Taktsignals im Bereich von synchronen, digitalen Schaltungen verwendet, um damit frequenzunabhängige Phasenverschiebungen zu erzielen. Eingesetzt werden DLLs beispielsweise in FPGAs des Herstellers Xilinx zur Aufbereitung zugeführter externer Taktsignale und zur Kompensation von Gatterlaufzeiten. DLLs werden auch in den meisten DDR-SDRAMs verwendet, um das Timing der Ausgänge gegenüber dem Taktsignal zu regeln (Ausnahme: in GDDR5-Bausteinen wird eine PLL verwendet).

Auch in GPS-Empfängern werden diese Schaltungen eingesetzt, um jeweils einem Satellitensignal zu folgen. Eine Erweiterung zur DLL ist die VDLL Vector-Delay-Lock-Loop, die ein Tracking unter noch widrigeren Umständen verspricht, allerdings derzeit noch Gegenstand von Forschungsarbeiten ist.

Literatur

- Donald R. Stephens: Phase-Locked Loops for Wireless Communications - Digital, Analog and Optical Implementations. 2. Auflage. Kluwer Academic Publishers, 2002, ISBN 0-7923-7602-1, S. 186–194.

Weblinks

- Using Delay-Locked Loops in Spartan-II FPGAs Applikationsschrift von Xilinx (engl.; PDF-Datei; 229 kB)