Power-Architektur

Die Power-Architektur (ein Backronym für Performance optimized with enhanced RISC) ist eine Familie von Prozessoren der OpenPower Foundation. Sie wurde ursprünglich von IBM als Nachfolger der Großrechner- und Midrange-Prozessoren in Bipolar und CMOS-Bauweise entwickelt.

IBM wechselte mit dieser Prozessorarchitektur von 31- bzw. 32-Bit-Prozessoren auf 64-Bit-Adressierung. Diese Prozessoren wurden und werden in den IBM-Serverbaureihen AS/400, RS/6000, später iSeries, pSeries und Z Systems eingesetzt. iSeries und pSeries wurden durch die POWER-Prozessoren in der Hardware vereinheitlicht.

Z Systems besitzen einen CISC-Befehlssatz, der auf Power-Prozessoren durch Microcode aus dem Power-Befehlssatz (eigentlich ein RISC, Reduced Instruction Set Computer) nachgebildet wird. Dieses Vorgehen ist bei CPU-Herstellern nicht unüblich, auch x86-CISC-Prozessoren arbeiten intern RISC-artigen Microcode ab. Die Hardware-Basis für die Prozessoren in den Z Systems und IBM-Power-Prozessoren ist damit identisch.

Auch der Zweig der PowerPC-Prozessoren für Workstations wurde von der POWER-Plattform abgewandelt. Ab Generation POWER8 werden auch sogenannte Linux basierte OpenPOWER-Serversysteme gebaut, die jene Prozessoren enthalten.

Im Jahre 2019 wurde die Befehlssatzarchitektur, englisch Instruction Set Architecture (ISA), offengelegt. Sie beschreibt im Detail die vollständige RISC-Architektur der Power-ISA, sodass Unternehmen Power-Prozessoren entwickeln können, ohne dafür Lizenzen erwerben zu müssen.[1] Seit Februar 2020 sind Prozessoren der Power-Architektur generell frei von Lizenzkosten, auch bei Produktion und Verkauf von Prozessoren. Dieser Schritt wird als Reaktion auf die ebenfalls Lizenzkosten-freie RISC-V-Architektur angesehen.[2]

Mit der Power Architecture Platform Reference (PAPR) ist eine offene Hardwareplattform für die Power- und die PowerPC-Architektur definiert.

POWER

Aus der ursprünglichen Power-Familie wurde zunächst der Ein-Chip-Prozessor PowerPC 601 abgewandelt, welcher aus dem Zusammenschluss von Apple, IBM und Motorola hervorging (AIM-Allianz). Die Power-Architektur fand schnell in den Bereichen der Workstation-Computer (Apple), in eingebetteten Systemen sowie in der Raumfahrt Verwendung.

POWER2

Aus dem 1993er Acht-Chip-Prozessor POWER2 wurde 1996 der POWER2 SC, der erste Power-Prozessor aus einem Chip, abgeleitet, und noch bis 1999 verkauft.

POWER3

1998 erschienen der POWER3 und der POWER3-II mit 64-Bit-CMOS6S2-Technologie, und 225 mm² (POWER3) bzw. 170 mm² (POWER3-II) Die-Fläche.

POWER4

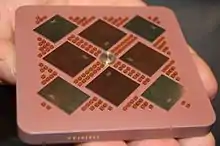

Die IBM p690, genannt Regatta, realisierte erstmals auf einem Chip zwei CPU-Kerne (zunächst ab 2001 POWER4, 180 nm, 1,1–1,3 GHz), einen gemeinsamen L2-Cache und eine sehr schnelle Switch-Schnittstelle. Aber auch die Verbindungsschnittstellen dieser Chips waren neuartig. So wurden vier dieser Prozessorkerne auf einem gemeinsamen Multi-Chip-Modul (MCM) verbunden; IBM erreichte damit die extrem hohe Packungsdichte von acht CPUs auf einer Fläche von 90 cm². Die Regatta erreichte mit 32 POWER4+-CPUs (ab 2002: 130 nm, 1,2–1,9 GHz, 267 mm², 185 Mio. Transistoren) im März 2004 eine Spitzenleistung von über 1 Mio. Punkten im Datenbank-Benchmark tpm-C.

Aus dem POWER4 ging der von IBM entwickelte PowerPC 970 hervor, der von Apple als G5 bezeichnet wurde. Er gilt als Nachfolger des PowerPC G4, der von Motorola stammte.

Power5

Power5 130 nm 1,5; 1,65; 1,9 GHz Dual-Core-Prozessor, 389 mm², 276 Mio. Transistoren, mit Simultaneous Multithreading (SMT) und integriertem Speichercontroller. Cache: 64k2w-lru (Instruktionen) und 32k4w-lru (Daten). L2-Cache 1.92m10w-lru. in partitionierbaren pSeries und iSeries SMP-Servern von 1 bis 64 CPUs, 1 GB–2 TB Hauptspeicher und 5 – 240 PCI-X-Slots. Ein Multi-Chip-Module mit vier CPU-Chips (also acht Kernen) und vier 36 MB L3-Cache-Chips besteht aus 89 Metalllagen mit insgesamt 5370 I/O-Pins, von denen 2313 Signalpins sind und 3057 für die Energiezufuhr benötigt werden.

Power5 von 2004 ist die Weiterentwicklung von POWER4. Zusätzlich zur POWER4-Architektur befindet sich auf dem Chip das L3-Directory und der Memory-Controller, dazu kommt eine höhere Taktung. Power5 ist bis zu dreimal leistungsfähiger als POWER4. IBM behauptete, dass dieses für die damals beste Skalierbarkeit (linear bis 64 Wege) aller am Markt angebotenen Server sorgte. Als weitere einzigartige Funktionalität bietet die Power5-Architektur mit der Advanced Power Virtualization (APV) unter anderem die Möglichkeit, die physikalischen CPUs in virtuelle CPUs aufzuteilen, die dann wieder zwischen den verschiedenen logischen Partitionen (LPARs) im laufenden Betrieb dynamisch und automatisch verteilt werden. APV wird seit dem 21. Dezember 2008 unter dem Namen PowerVM verkauft.

Am 4. Oktober 2005 kündigte IBM den Power5+ 90 nm Dual-Core-Prozessor mit 1,5 oder 1,9 GHz an.[3] Ab Mitte 2006 gab es Single- und Dual-Core-Power5+-Prozessoren mit bis zu 2,3 GHz.[4]

Power6

Der Power6-Prozessor wurde ab 2007 im 65-nm-Verfahren gefertigt und hat eine Die-Fläche von 341 mm². Auf dieser Fläche sind über 790 Millionen Transistoren[5]. Das meiste der Fläche wird vom 8 MiB fassenden L2-Cache belegt, wovon jedem Core die Hälfte, also 4 MiB, zugeteilt werden. Die Größe des L1-Caches ist 128 KiB, aufgeteilt in 64 KiB Daten- und 64 KiB Instruktionscache. Der externe L3-Cache in der Größe von 32 MiB ist mit einer Bandbreite von 80 GiB/s ansprechbar. Die Power6-Prozessoren sind mit 4,2; 4,7 und 5,0 GHz Taktfrequenz erhältlich.

IBM sieht diesen Prozessor im Bereich von Unternehmensdatenbanken (z. B. IBM System p und IBM System i) sowie Hochleistungsrechnern, wie sie im Flugzeugbau und bei Unfallsimulationen im Automobilbau benötigt werden.

Power7

Der Power7 ist 2010 auf den Markt gekommen und besteht aus bis zu acht Kernen, wovon jeder Kern parallel bis zu vier Threads ausführen kann. Die CPU wird in 45 nm gefertigt und die maximale Taktfrequenz liegt bei 4,1 GHz.[6][7]

Aktuell ist die Power7+-CPU welche in 32 nm gefertigt wird und nun einen Maximaltakt von 4,42 GHz erreicht.[8]

Mit der POWER7-Familie wird die POWER ISA v2.0 Erweiterung des Befehlssatzes realisiert.[9]

OpenPOWER Foundation

IBM gründet 2013 die OpenPOWER Foundation,[10] um den Verkauf der POWER-Prozessoren an andere Systemhersteller zu ermöglichen. Entsprechende Dokumentationen sind bei IBM erhältlich.[9] Während POWER-Maschinen bisher unter den IBM-Betriebssystemen AIX und OS/400 liefen, unterstützt IBM auf den OpenPOWER-Maschinen Linux als Betriebssystem. Entsprechende Distributionen werden von SUSE, Red Hat, Debian und Ubuntu herausgegeben, Herstellerunabhängigkeit ist damit auch bei dem Betriebssystem und den Anwendungen gegeben.

Die Foundation legt die Spezifikationen für Prozessoren und OpenPOWER-Systeme offen. IBM hat angekündigt, dass in Zukunft POWER-Prozessoren zunächst in einer OpenPOWER-Variante für Linux-Betriebssysteme erscheinen, bevor IBM entsprechende Prozessoren für die eigenen System i und AIX-System p Baureihen herausbringt. Dies unterstreicht die Bedeutung des OpenPOWER-Ansatzes für IBM:

„Dieser Schritt muss als Versuch gesehen werden, POWER-Prozessoren als herstellerunabhängige Konkurrenz zu x86-Produkten zu etablieren, IBM muss auf höhere verkaufte Stückzahlen kommen, um die zukünftige Prozessorentwicklung zu finanzieren. Der angepeilte Zielmarkt ist High Performance Computing, weswegen NVLink-Verbindungen integriert werden, die die Integration von Rechenbeschleunigern ermöglichen.“

POWER8

Auf der Hot-Chips-25-Konferenz im Jahr 2013 hat IBM die Power8-CPU mit 12 Kernen vorgestellt. Jeder der 12 Kerne, welche auf je 512 KB L2-Cache und gesamt auf 96 MB L3-Cache und 128 MB L4-Cache zugreifen können, ist in der Lage mittels Simultaneous Multithreading bis zu 8 Threads gleichzeitig auszuführen. Power8 wird im 22-nm-Verfahren hergestellt, die 12-Kern-Version hat eine Die-Fläche von 650 mm² und über 4,2 Milliarden Transistoren. Über einen mit 32 Kanälen angebundenen Speicherkontroller können bis zu 1 TByte DDR3-1600-RAM angebunden werden. Die CPU-Takfrequenz reicht, je nach Konfiguration, von 3,02 bis 4,15 GHz.[11]

Die Power8-CPU's sind mit mehreren Hochleistungsverbindungen ausgerüstet:[12]

- NVLink 1.0: hier können bis zu 4 Rechenbeschleunigermodule Nvidia Tesla – Pascal P100 integriert werden

- CAPI 1.0

- PCI Express 3.0

OpenPOWER8-Systeme

- IBM:

- Andere Hersteller (Auszug):

POWER8 Systeme i/p von IBM

- Power Systems E850 – 2×, 3× or 4× POWER8 DCM (8, 10 or 12 Kerne), 4U

- Power Systems E870 – 1× or 2× 5U Nodes, jeder mit 4 Sockel und 8- or 10-core POWER8 Modulen, bis zu 80 Kerne insgesamt

- Power Systems E880 – 1x, 2x, 3x or 4x 5U Nodes, jeder mit 4 Sockel und 8- or 12-core POWER8 Modulen, bis zu 192 Kerne insgesamt[17]

POWER9

Die Power9-Familie von IBM besteht aus mehreren Prozessormodulen hergestellt in einem 14 nm FinFET-Prozess von Globalfoundries mit 8 Mrd. Transistoren auf 695 mm² Fläche. Sie wurden auf der Hot-Chips-Konferenz im August 2016 angekündigt, die ersten Systeme wurden im Dezember 2017 für die im Aufbau befindlichen Supercomputer Summit am Oak Ridge National Laboratory und Sierra am Lawrence Livermore National Laboratory (LLNL) geliefert.[18], im Juni 2018 ist auch ein Cluster mit IBM AC922-Systemen innerhalb des MareNostrum 4 Systems in Barcelona in Betrieb[19].

In den POWER9-Prozessoren wird die Erweiterung des Befehlssatzes POWER ISA v3.0 realisiert:

- 128-bit Quad-Precision-Floating-Point und -Integer Operationen

- 16-bit Floating-Point Konvertierungen

- AltiVec-3 SIMD-Instruktionen

Chipvarianten für 1–2-Prozessoren-Systeme (genannt "Scale-Out", Codename Nimbus) sowie NUMA-Maschinen ("Scale-Up", Codename Centaur) gibt es entweder mit bis zu 12 Kernen / 8-fachem Simultaneous Multithreading (SMT) oder bis zu 24 Kernen / 4-fachem SMT.[20] Die Varianten mit 8-fach-Multithreading sollen den IBM-eigenen Power-VM-Plattformen (System i und p) vorbehalten bleiben.

Nimbus und Centaur unterscheiden sich in Hauptspeicherausbau und Anbindung:

- Scale-Out: 8 Kanäle mit jeweils bis zu 2 Modulen (16 Module, 4 TB/Sockel), zusammen 120 GByte/s Bandbreite

- Scale-Up: 8 Kanäle mit jeweils bis zu 4 Modulen (32 Module, 8 TB/Sockel), zusammen 230 GByte/s Bandbreite

Jeder Kern verfügt über je 32 KByte Daten- u. Instruktions-1st-Level-Cache, 512 KByte 2nd-Level Cache und 120 MB für alle Kerne gemeinsamen 3rd-Level-Cache. Die Taktfrequenzen sind zunächst mit 2,0 bis 2,6 GHz ausgewiesen und fallen damit deutlich geringer aus als bei der POWER8-Generation.[21]

| Merkmal | Scale-Out Linux | Scale-Out Power-VM | Scale-Up Linux | Scale-Up Power-VM |

|---|---|---|---|---|

| Anzahl Sockel | 1–2 | 1–2 | 4–16 | 4–16 |

| max. Anzahl Kerne | 24 | 12 | 24 | 12 |

| Anzahl Threads je Kern / Prozessor | 4 | 8 | 4 | 8 |

| DDR4-Kanäle/Module | 8/16 | 8/16 | 8/32 | 8/32 |

Power9-Prozessoren unterstützen mehrere Hochleistungsverbindungen:

- auf dem Chip ist ein Hochleistungsswitch mit 7 TB/sec Bandbreite integriert, der Kerne, L3-Cache und Peripherie verbindet

- PCI-Express 4.0 mit 48 Lanes und 192 GB/sec Bandbreite. Version 4.0 ist erstmals in der POWER9-CPU realisiert

- CAPI 2.0 über PCIe 4.0

- bis zu 48 optische Verbindungen (XBus) mit 25 GB/sec Bandbreite, in Summe 300 GB/sec

- NVLink 2.0 über 25 G/s für den Anschluss von Nvidia-Rechenbeschleuniger.

- OpenCAPI 3.0 über 25 G/s, gedacht für die Anbindung weiterer Beschleuniger-Chips

- Beschleuniger für GZIP, AES und Zufallszahlen sind auf dem Chip verbaut und in der POWER ISA 3.0 enthalten.

- Über die integrierten NVLink 2.0-Schnittstellen können bis zu 4 (IBM AC922) oder 6 (IBM S922LC) Nvidia Tesla – Rechenbeschleuniger (Volta Generation – V100) in ein 2-Sockelsystem integriert werden.[23]

OpenPOWER9-Systeme

Drei IBM-Prozessor-Packages sind in 01/2018 erhältlich:

- Sforza: 50 mm × 50 mm, FC-PLGA, 4 DDR4, 48 PCIe Lanes and 1 XBus 4B

- Monza: 68,5 mm × 68,5 mm, FC-PLGA, 8 DDR4, 34 PCIe Lanes and 1 XBus 4B, 48 OpenCAPI lanes

- LaGrange: 68,5 mm × 68,5 mm, FC-PLGA, 8 DDR4, 42 PCIe Lanes and 2 XBus 4B, 16 OpenCAPI lanes[24]

Folgende Hersteller hatten zum Zeitpunkt des Produktstarts von POWER9 OpenPOWER-9 Systeme im Angebot:

IBM Scale Out-POWER9-Systeme

Mitte Februar 2018 stellt IBM die ersten 6 Systeme vor, die neben Linux auch die hauseigenen Betriebssysteme AIX und System i bzw. OS/400 nutzen können.[27] Es handelt sich dabei um 1–2-Sockel-Systeme der Scale-Out-Varianten mit einem Hauptspeicherausbau von bis zu 2 TB je Sockel. Die Gehäuse sind mit 2- oder 4-Höheneinheiten lieferbar, die 4U-Gehäuse werden mit bis-zu-12-Kern-CPU's geliefert, die 2U mit bis-zu-10-Kern CPU's. 2 Varianten sind für SAP-HANA-Anwendungen zertifiziert: [28]

| Modell | Kerne | Höhe / Sockel | Betriebssysteme | RAM | IO |

|---|---|---|---|---|---|

| L922 | 8/10/12 | 2U / 1–2S | Linux | 4TB | 5 × PCIe G4 (4 CAPI 2.0), 4 × PCIe G3 |

| S914 | 4/6/8 | 4U / 1S | AIX, IBM i, Linux | 1TB | 2 × PCIe G4 (4 CAPI 2.0), 6 × PCIe G3 |

| S922 | 4/8/10 | 2U / 1–2S | AIX, IBM i, Linux | 4TB | 5 × PCIe G4 (4 CAPI 2.0), 4 × PCIe G3 |

| S924 | 8/10/12 | 4U / 2S | AIX, IBM i, Linux | 4TB | 5 × PCIe G4 (4 CAPI 2.0), 6 × PCIe G3 |

| H922 | 4/8/10 | 2U / 1–2S | HANA, AIX, IBM i | 4TB | 5 × PCIe G4 (4 CAPI 2.0), 6 × PCIe G3 |

| H924 | 8/10/12 | 4U / 2 S | HANA, AIX, IBM i | 4TB | 5 × PCIe G4 (4 CAPI 2.0), 6 × PCIe G3 |

| E950 | 8/10/11/12 | 4U / 2-4S | AIX, IBM i, Linux | 16TB / 4x16 DDR4-DIMMs | 8x16 + 2x8 PCIe G4, (4 CAPI 2.0, 4 NVLink), 1x8 PCIe G3, 4 NVMe |

| E980 | 8/10/11/12 | 4 "Nodes" mit 5U, 1 SCU 2U / 4-16S | AIX, IBM i, Linux | 64TB / 16x8 CDIMMs (TFF oder SFF) | 4x8x16 PCIe G4, 4x4 NVMe, 32 Accelerator-Links (CAPI 2.0 oder NVLink oder OpenCAPI) |

POWER10

Auf der Hot-Chips-Konferenz HC32 2020 kündigte IBM Systeme mit Power10 für das zweite Halbjahr 2021 an. Die Prozessoren sollen in 7-nm-Strukturen hergestellt werden und der Power ISA v3.1 entsprechen, die im Rahmen von OpenPOWER offengelegt wird.[29]

Einzelnachweise

- Hugh Blemings: The Next Step in the OpenPOWER Foundation Journey, 20. August 2019.

- Mark Mantel: Prozessor-ISA Power: OpenPower Foundation stellt offenes Lizenzmodell vor. In: Heise online. 17. Februar 2020. Abgerufen am 18. Februar 2020.; Zitat: „Chiphersteller können künftig Power-Prozessoren entwickeln und verkaufen, ohne Lizenzabgaben an die OpenPower Foundation zahlen zu müssen.“.

- The Register: IBM pumps Unix line full of Power5+ (englisch) vom 4. Oktober 2005

- The Register: IBM begins third phase of Power5+ journey (englisch) vom 11. Juli 2006

- Power6 Fact Sheet, 21. Mai 2007.

- Heise online: Technische Details zu IBMs POWER7-Prozessoren und -Servern

- IBM: Power-Hardware

- Heise online: IBM erweitert Server-Linie mit Power7+-Prozessor

- IBM Portal for OpenPOWER. Abgerufen am 10. Januar 2018.

- Home - OpenPOWER. Abgerufen am 10. Januar 2018.

- IBM Power Systems S814 and S824 Technical Overview and Introduction. Abgerufen am 10. Januar 2018.

- POWER8 - Microarchitectures - IBM. Abgerufen am 10. Januar 2018.

- IBM Power System S822LC for High Performance Computing Introduction and Technical Overview. Abgerufen am 10. Januar 2018.

- IBM Power Systems S814 and S824 Technical Overview and Introduction. Abgerufen am 10. Januar 2018.

- Magna OpenPOWER Server. Abgerufen am 10. Januar 2018.

- TYAN’s OpenPOWER Customer Reference System Now Available. Abgerufen am 10. Januar 2018.

- http://www.redbooks.ibm.com/redpapers/pdfs/redp5137.pdf

- https://www.heise.de/ix/meldung/IBM-POWER9-Server-zu-Weihnachten-3910888.html

- https://www.nextplatform.com/2018/06/13/bsc-fires-up-power9-v100-hybrid-compute-on-marenostrum-4/

- https://www.extremetech.com/extreme/234413-ibm-details-next-gen-power-9-will-take-the-fight-to-intels-data-center-strongholds

- https://cdn2.hubspot.net/hubfs/652102/Documents/POWER9-Features-and-Specifications.pdf

- https://en.wikichip.org/wiki/ibm/microarchitectures/power9

- https://openpowerfoundation.org/wp-content/uploads/2016/11/Jeff-Stuecheli-POWER9-chip-technology.pdf

- siehe auch https://www.extremetech.com/computing/237734-google-puts-intel-on-notice-looks-forward-to-using-non-intel-chips-within-its-cloud

- https://www.ibm.com/de-de/marketplace/power-systems-ac922/details

- https://www.raptorcs.com/

- https://www.heise.de/ix/meldung/IBM-Server-mit-POWER9-3966886.html

- http://www.theregister.co.uk/2018/02/14/ibm_power9_servers/

- Christof Windeck: IBM POWER10 für Server mit bis zu 960 Threads und Cluster mit 2 PByte RAM. In: Heise online. 17. August 2020. Abgerufen am 19. August 2020.

Weblinks

- Timo Schöler: Nahaufnahme: IBM Power. (PDF, 404 KByte), Entwicklungen von IBMs Power-CPUs der letzten Jahre im Überblick, detaillierte Darstellung der in der Power5(+)-CPU genutzten Technologien (2005)