Paritätsgenerator

Ein Paritätsgenerator ist eine logische Schaltung im Bereich der Digitaltechnik, die für ein Datenwort ein zusätzliches Kontrollbit (=Paritätsbit oder engl. Parity-Bit) erzeugt. Bei serieller Übertragung wird das Paritätsbit direkt nach den Datenbits eines Bytes (oder Worts) angefügt.

Gerade und ungerade Parität

Beim Paritätsgenerator wird zwischen der geraden und der ungeraden Parität unterschieden:

| Wert des Parity-Bits | Parität | ||

| gerade (even) |

ungerade (odd) | ||

| Anzahl von Einsen im Datenwort |

gerade | 0 | 1 |

| ungerade | 1 | 0 | |

Realisierung

In Hardware

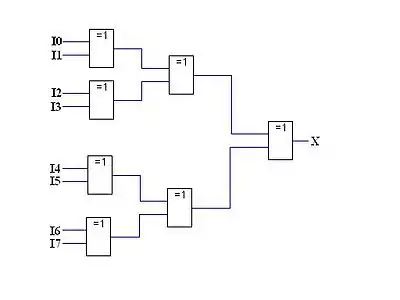

Die nachfolgende Schaltung eines 8-Bit-Paritätsgenerators stellt einen Paritätsgenerator mit gerader Parität dar. Eine solche Schaltung dient der Daten- bzw. Übertragungssicherheit: Den eigentlichen Datenbits wird ein Prüfbit (hier: Paritätsbit) hinzugefügt, das von allen Eingangsbits abhängt, d. h. es ändert sich, wenn sich nur eines der Eingangsbits ändert. Wenn dieses Prüfbit zusammen mit den Datenbits in eine Übertragungsstrecke eingespeist wird, kann an deren Ende eine identische Schaltung ein Prüfbit erzeugen, welches wiederum mit dem empfangenen Prüfbit verglichen wird.

Zur schaltungstechnischen Realisierung eines Parity-Generators mit Logikbauelementen können Exklusiv-Oder-Gatter verwendet werden. Durch einen nachgeschalteten Inverter am Ausgang X kann die abgebildete Schaltung des 8-Bit-Paritätsgenerators von der geraden Parität auf die ungerade Parität umgestellt werden.

8-Bit-Paritätsgenerator |

In Software

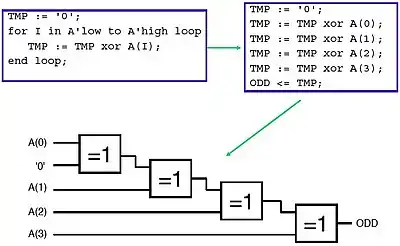

In der Datenverarbeitung werden solche Prüfbits manchmal auch direkt per Software erzeugt, (siehe Programmcode in der Abbildung).

Paritätsgenerator |

Verfahren mit erweiterter Sicherheit

Da sich das Prüfbit beim Parity-Generator nicht ändert, wenn sich eine gerade Anzahl an Eingangsbits ändert, bietet dieses Verfahren nur einen beschränkten Sicherheitsgewinn. Für höhere Sicherheit gibt es beispielsweise Codes und Verfahren, die entweder mehr als ein Prüfbit pro Datenwort besitzen (Hamming-Code) oder beispielsweise eine CRC-Checksumme verwenden.