Leiterplattenentflechtung

Die Leiterplattenentflechtung ist ein Arbeitsschritt beim Layoutentwurf (kurz: layouten) von elektronischen Leiterplatten. Dabei wird der entworfene elektrische Schaltplan nach dem manuellen oder automatischen Platzieren der Bauelemente auf der Leiterplatte in ein Leiterbahnnetzwerk umgesetzt. Sie wird heute fast ausnahmslos am Computer per Hand oder automatisiert mithilfe eines sogenannten Autorouters durchgeführt.

CAD-Software zum Leiterplattenentwurf umfasst neben dem Schaltplanentwurf und dessen Simulation oft auch Auto-Platzierer und Autorouter. Damit ein Autorouter sinnvolle Ergebnisse liefern kann, müssen ihm zuvor Designregeln vorgegeben werden. Macht man das nicht, stoßen diese automatischen Funktionen an Grenzen, so dass Leiterbahnen zumindest teilweise manuell verlegt werden müssen.

Vorgehen bei der Leiterplattenentflechtung

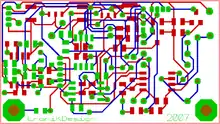

Die Entflechtung erfolgt nach der Erstellung eines elektrischen Schaltplans, der auch in Form einer Netzliste vorliegen kann, und der Platzierung der Bauteile am Bildschirm. Nach diesen Schritten liegt ein sogenanntes „Rattennest“ (englisch rats nest) vor, bei dem alle elektrischen Verbindungen durcheinander auf den kürzesten Wegen dargestellt sind.

Bei der Entflechtung müssen u. a. Leiterplattentechnologie, Bauteilgeometrien, Lage der Bauteile, Signallaufzeiten, Stromstärken sowie Lage der äußeren Anschlüsse (Steckverbinder) berücksichtigt werden.Insbesondere durch Bauteile-Datenbanken und die Überprüfungen von Designregeln erleichtern Layout-Programme die Arbeit bei der Leiterbahnentflechtung. Ausgegeben werden die CAD-Daten für Platinenherstellungen, Bestückungen und Einkauf typischerweise im Gerber-Format sowie als Stückliste (englisch: Bill of Materials, BOM).

- Anlegen von Bauteilbeschreibungen in der zum Layout-Programm gehörigen Bauteilbibliothek.

- Eingabe des Schaltplanes mit dem entsprechenden Software-Modul.

- Eingabe der Leiterplattengeometrie (manuell oder Import der Daten aus einem Mechanik-CAD-Programm).

- Eingabe der Leiterplattentechnologie (Lagenaufbau, verwendete Via-Technologie, Regeln für Leiterbahnbreiten, Abstandsregeln)

- Platzieren der Bauteile auf der Leiterplatte (zuerst diejenigen Bauteile, die an bestimmten Stellen sein müssen, z. B. Potentiometer, die durch die Frontplatte ragen)

Die weitere Platzierung wird so durchgeführt, dass:

- die Leitungsverbindungen möglichst kurz sind

- die vorgegebenen Regeln für die Verbindungen der Bauteile eingehalten werden

- ausreichend Platz für das Verlegen der Leitungen besteht

- Vorgaben aus der Leiterplattenfertigung berücksichtigt werden

Die Designregeln können unter Umständen sehr umfangreich sein. Sie ermöglichen es aber dem Layouter, die Entflechtung mit weniger aufwendigen Iterationen und Fehlerkontrollen durchzuführen.

Die Platzierung erfolgt in der Regel interaktiv. Dabei werden die zu erzeugenden Verbindungen als „Gummibänder“ zwischen den Anschlüssen dargestellt, um eine vorteilhafte Platzierung zu ermöglichen. Zur Platzierung unkritischer Bauteile am Ende des Platzierens eignen sich heute in weniger dichten Designs durchaus auch automatische Platzierhelfer wie zum Beispiel Autoplacer.

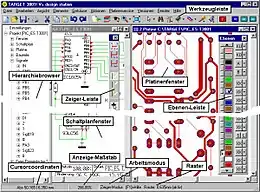

Software

Die Arbeit wird durch Layout-Programme unterstützt, das sind z. B.:

- Pulsonix

- EDWinXP

- OrCAD

- Eagle

- TARGET 3001!

- Cadence Allegro

- Siemens AG VCAD

- Altium Designer (vormals Protel)

- Expedition PCB

- KiCad (Open-Source)

- gEDA (Open-Source)

siehe auch: EDA: Programme für den Entwurf von Leiterplatten

Entflechtung mit Autorouter

Moderne mehrlagige Designs mit BGAs werden in der Regel mit Entflechtungsprogrammen (Autorouter) automatisiert bearbeitet, dazu müssen vorher Randbedingungen (Regeln) in das Layout-Tool eingegeben werden. Damit ein Autorouter brauchbare Ergebnisse liefert, können die Routing-Strategien vorgegeben werden. Ob es sinnvoller ist, einen Autorouter zu verwenden, oder von Hand zu routen, ist stark von der Art des Designs abhängig. Sollen mehrere ähnliche, digitale Designs bearbeitet werden, so kann es sinnvoll sein, Regeln und Routingstrategien zu optimieren und wiederzuverwenden. Bei kleinen Projekten oder speziellen Anforderungen, z. B. HF, nimmt die Regel-Eingabe mehr Zeit in Anspruch als die manuelle Leiterplattenentflechtung durch einen erfahrenen Layouter. Mitunter ist ein iteratives Layouten notwendig, wenn der Autorouter keine (vollständige) Lösung für das Entflechtungsproblem findet.

Oft müssen auch Regeln beachtet werden, die in einigen Routern nicht vorgegeben werden können, z. B. Sternpunkterdung, Bezugspunkte für Analogspannungen, Eigenschaften beim Löten, Wärmemanagement bzw. thermal vias. Hier können eventuell nur Teile des Designs mit dem Autorouter entflochten werden.

Manuelle Entflechtung (Handverlegung)

Bei manueller Entflechtung werden zuerst kritische Leitungen wie Hochfrequenzleitungen oder Busse verlegt. Oft wählt man die Vorzugsrichtung der Leiterbahnen auf der Oberseite senkrecht zu derjenigen auf der Unterseite. Bei jeder Richtungsänderung kann nun mittels einer Durchkontaktierung die Ebene gewechselt werden.

Bei der Verlegung bietet die Layout-Software Unterstützung durch die Anzeige eines Saumes um den Leiterzug, der die Einhaltung der Designregeln erleichtert. Während der Entflechtung ist es oft nötig, einzelne Bauteile noch einmal zu verschieben. Bei hochwertigen EDA-Programmen gibt es daher meist die Möglichkeit, einzelne Signale halbautomatisch zu entflechten und per „push aside“ oder „push and shove“ bereits verlegte Leiterbahnen und Bauteile aus dem Korridor für die gerade per Hand bearbeitete Leiterbahn schieben zu lassen.

Nach dem Layout kann die Software mittels automatischem Designregeltest (englisch Design Rule Check, DRC) prüfen, ob alle festgelegten Designregeln eingehalten werden und keine logischen Fehler vorliegen, z. B. nicht angeschlossene Bauteile oder Leiterbahnkreuzungen.

Grenzen der Entflechtung

Bei sehr dicht belegten Leiterplatten können unter Umständen auch per Hand nicht alle Leiterbahnen verlegt werden, weil für die Verbindung einiger Bauteilanschlusspunkte keine freien „Gassen“ mehr existieren. Diese fehlenden Verbindungen müssen dann bei der Bestückung durch Drahtbrücken gebildet werden oder von Hand als Drähte verlegt werden. Das ist aus Kostengründen, aber auch aufgrund der technischen Anforderungen (Hochfrequenz, Signallaufzeiten, Zuverlässigkeit) nur bei wenigen Produkten vertretbar. Hinzu kommt, dass bei Leiterbahnbreiten und -abständen von 75 bis 150 µm Lötaugen zum Anschluss von Drähten kaum noch Platz finden. Als Alternative zu Drahtbrücken gibt es Lötbrücken (Jumper) und „Null-Ohm-Widerstände“. Gegebenenfalls kann man auch die Anzahl der Lagen erhöhen oder bei Mehrlagenleiterplatten mit Durchkontaktierungen arbeiten, die sich nicht auf allen Lagen befinden (sogenannte blind vias und buried vias, siehe Durchkontaktierung).

Designregeln für die Leiterplattenentflechtung

Bei der Leiterplattenentflechtung sind meist weitere Vorgaben zu beachten, z. B.:

- Beschränkungen der verwendeten Herstellungstechnologie wie minimale Leiterbahnbreiten, minimale Bohrdurchmesser, Abstand von Kupferflächen zum Rand etc.;

- Einhaltung der Wellenimpedanz spezieller Leitungen (z. B. bei Hochfrequenz, Ethernet, USB);

- Einhaltung der Leitungslängen bei Signalen mit Bezug zueinander (Datenbusse, symmetrische Signale) durch Mäanderleitungen;

- Übersprechen von Leitungen (z. B. bei kompakten Geräten wie Mobiltelefonen);

- Vorgaben der Signallaufzeit (z. B. Leitungslängen bei PCI, PCI Express);

- Berücksichtigung der elektromagnetischen Verträglichkeit (EMV);

- Einhaltung von Isolationsabständen ab ca. 50 V nach Norm (z. B. nach VDE: Abstände für Luftstrecken, Kriechstrecken).

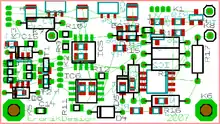

Ergebnis der Leiterplattenentflechtung (output)

Das Resultat ist ein vollständig entflochtenes Design, welches keine Luftlinien mehr enthält und das alle Informationen in sich trägt, um eine Leiterplatte herstellen zu können. Es besteht aus mehreren Schichten virtueller Kupferlagen und Verbindungen zwischen ihnen, sowie den Bauteildimensionen und Platzierungskoordinaten. Aus diesen Daten werden i. d. R. Produktionsdaten (Gerberdaten) für die Belichtung und Ätzung beim Hersteller gewonnen. Ferner kann das sogenannte "drill file", eine Datei mit Informationen über die Anordnung und Größen der benötigten Bohrungen, erzeugt werden, mit dessen Hilfe ein CNC-Bohrwerkzeug die Platine bearbeiten kann. Auch Informationen für den boundary-scan-Test und flying-probe-Test können aus dem Platinenfile gezogen werden.

Literatur

- J. Händschke: Leiterplattendesign – Ein Handbuch nicht nur für Praktiker. Eugen G. Leuze Verlag, Bad Saulgau 2006, ISBN 3-87480-219-1.

- K. Mitzner, B. Doe, A. Akulin, A. Suponin, D. Müller: Complete PCB Design Using OrCAD Capture and PCB Editor, Elsevier / Academic Press 2019, ISBN 9780128176849