Intel 8237

Der Intel 8237 ist ein programmierbarer DMA-Steuerungsbaustein aus der Familie der Peripheriebausteine der 8-Bit-Mikroprozessoren Intel 8080/8085. Er wurde auch in 16-Bit-Systemen mit den Prozessoren Intel 8086/8088 und seinen Nachfolgern und in den ersten IBM-PC eingesetzt.

Allgemeines

Er wurde u. a. an NEC lizenziert.

Aufbau und Funktion

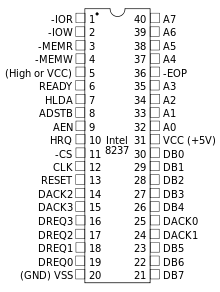

Der 8237 ist eine Weiterentwicklung des 8257 und wird, wie dieser, im 40-Pin-DIL-Gehäuse geliefert. Mit Hilfe des DMA-Controllers können größere Datenmengen ohne weiteren Eingriff der CPU per schnellem Speicherdirektzugriff in den Systemspeicher übertragen oder ausgelesen werden. Dabei werden Datenraten von bis zu 1,6 MByte/s erreicht. Der 8237 unterstützt vier DMA-Kanäle zur Übertragung von Daten von externen Bauteilen oder Speichern, wobei die Anzahl von Kanälen mit weiteren Bausteinen beliebig erweitert werden kann. Als Peripheriebaustein einer 8-Bit-Mikrocontroller-Familie verfügt der 8237 über 8-Bit Daten- und 16-Bit Adressleitungen, jeder Kanal kann also 64 KByte Speicherbereiche adressieren und mit einem Steuerbefehl bis zu 64 KByte Daten übertragen.

Wenn ein DMA-Kanal einen Datentransfer durchführen möchte, muss der DMA-Controller von dem entsprechenden Kanal über ein Signal DREQ (DMA Request) unterrichtet werden. Daraufhin zeigt der Controller der CPU über ein Signal HRQ (Hold Request) an, dass er auf den Speicher zugreifen möchte. Wenn die CPU den Datenbus freigeben kann, bestätigt sie dieses an den DMA-Controller durch das Signal HLDA (Hold Acknowledge). Dann kann der DMA-Kanal des 8237 den Datentransfer in vier unterschiedliche Betriebsarten durchführen:[1]

- Single Mode

Abwechselnd mit der CPU kann die DMA-Einheit jeweils für einen Speicherzyklus auf den Speicher zugreifen, wobei jeweils Adresszeiger und Wortzähler verringert werden.

- Block Mode

Ein kompletter Block von Daten wird übertragen bis entweder die vollständige Übertragung abgeschlossen worden ist, oder der DMA-Kanal durch ein Signal EOP (End of Process) zum vorzeitigen Beenden aufgefordert wird.

- Demand Mode

Die Datenübertragung wird solange fortgesetzt, bis die Übertragungsanforderung durch Wegfall des Signals DRQ angezeigt wird oder eine der anderen Bedingungen wie im Block Mode den Transfer beendet.

- Cascade Mode

Bei der Kaskadierung von mehreren 8237-Bausteinen werden die entsprechenden DMA-Steuersignale der einzelnen Bausteine zu einer Prioritätskette verknüpft.

Verwendung

Er wird seit den ersten PCs (IBM-PC und IBM-PC XT) eingesetzt.[2] Im IBM PC AT werden zwei Exemplare verwendet und in kaskadierter Form geschaltet.[3]

Literatur und Datenblätter

- Andreas Stiller: PC-Bausteine. Direkter Zugriff auf den Speicher, c't, 1988, Heft 9, S. 178–189.

- NEC Electronics (Europe) GmbH, 1982 Catalog, S. 607–617 (µPD8237A High Performance Programmable DMA Controller).

Weblinks

- FreeBSD Developers' Handbook: Kapitel 15 DMA (dargestellt am Beispiel des 8237).

Einzelnachweise

- 8237/8237-2 High Performance Programmable DMA Controller. In: Datenblatt. Intel, abgerufen am 17. Juni 2016.

- Technische Universität Chemnitz: Der Aufbau des Original-IBM-PC-Motherboards (Memento des Originals vom 8. Dezember 2011 im Internet Archive) Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis..

- Technische Universität Chemnitz: Das Motherboard des AT (Memento des Originals vom 6. Januar 2012 im Internet Archive) Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis..