Delta-Sigma-Modulation

Die Delta-Sigma-(ΔΣ)-Modulation ist eine Form der Analog-Digital-Umsetzung oder Digital-Analog-Umsetzung, welche sich von der Deltamodulation ableitet. Trotz der Entwicklung der ΔΣ-Technik in den frühen 1930er Jahren lässt sich diese Technik erst seit den 1970er Jahren mit den Fortschritten in der CMOS-Technologie preiswert fertigen. Delta-Sigma-Modulatoren werden von vielen großen Halbleiterherstellern als fertige integrierte Schaltung angeboten.

Prinzip

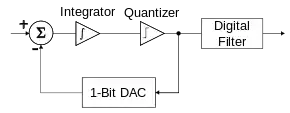

Das Prinzip der Delta-Sigma-Modulation beruht auf einer zunächst groben Messung des Signals (Quantisierer, im Bild engl. „Quantizer“). Der dabei entstehende Messfehler wird integriert (im Bild engl. „Integrator“) und über eine Gegenkopplung schrittweise kompensiert. Die besagten Schritte werden sehr häufig durchgeführt, beispielsweise mit der 128-fachen[1] Rate (Überabtastung) der Abtastrate der PCM-Daten, mit denen üblicherweise auf der digitalen Seite gearbeitet wird.

Das Bild stellt die Situation für einen Analog-Digital-Umsetzer dar: Das Ausgangssignal der Rückkopplungsschleife (1-Bit-Signal) wird von einem Digitalfilter verarbeitet, welches durch seinen Aufbau die Wortbreite und durch die Dezimierung (im Bild nicht dargestellt) die Abtastrate der PCM-Daten vorgibt. Das 1-Bit-Signal hingegen wird für den analogen Vergleich (hierbei ist der Quantisierer ein Komparator) am Eingang in ein Analogsignal umgewandelt. (Wobei umwandeln etwas hochtrabend klingt – es wird ja durch den 1-Bit-DAC lediglich zwischen zwei Spannungen umgeschaltet.) Am zugrundeliegenden Prinzip ändert sich nichts, wenn statt des Digitalfilters ein Analogfilter benutzt wird und am Eingang digitale PCM-Signale durch einen digitalen Vergleich verarbeitet werden – obwohl nun ein Digital-Analog-Umsetzer vorliegt. Entsprechend sind alle vier Kombinationen von Analog- und Digital-Eingang und -Ausgang denkbar. Die Kombinationen aus Analog- und Digitalteil bilden die schon beschriebenen Analog-Digital- und Digital-Analog-Umsetzer. Die Kombination Analog und Analog – mit digitaler Speicherung des 1-Bit-Signals (Direct Stream Digital) auf dem Datenträger – findet im Prinzip bei der SACD statt. Eine Digital-Digital-Umsetzung ist ggf. zur Abtastratenkonvertierung denkbar.

Das mittlere Ausgangssignal gibt das Eingangssignal wieder. Dabei hat die Delta-Sigma-Modulation die Eigenschaft, dass die spektrale Leistungsdichte das unerwünschte Quantisierungsrauschen bei niedrigen Frequenzen verkleinert und bei hohen Frequenzen (die außerhalb des zu erfassenden Frequenzbandes liegen) erhöht wird – anschaulich gesagt wird die Rauschleistung zu höheren Frequenzen verschoben; diese Tatsache wird als „Rauschformung“ oder engl. „Noise Shaping“ bezeichnet. Damit können die niederfrequenten Signalanteile mit hohem Rauschabstand erfasst werden.

Höhere Frequenzen werden aufgrund des ungünstigen Signal-Rauschverhältnisses nicht genutzt, und durch ein Filter (ein digitales Filter für einen Digitalausgang (ADC) bzw. ein analoges Filter für einen Analogausgang (DAC); im Bild engl. „Digital Filter“) entfernt. Wie oben schon angedeutet, führt dieses Filter im Falle eines digitalen Ausgangs gleichzeitig eine Dezimierung auf die gewünschte Ausgangsbandbreite durch und erweitert die Wortbreite des Quantisierers für einen passenden Dynamikumfang.

Die Anzahl der Integratoren bzw. die Anzahl der Gegenkopplungsschleifen charakterisieren die Ordnung des ΔΣ-Modulators. Je höher die Ordnung ist, umso stärker wird die Verschiebung des Rauschens, umso höhere Frequenzen können genutzt werden. Nachteilig ist bei höheren Ordnungen das prinzipiell mögliche Auftreten von Schwingungen und Instabilitäten in der Modulatorschaltung.

Das Verhältnis der Abtastratenkonvertierung (englisch Oversampling Ratio, OSR) und die Ordnung N bestimmen den möglichen Dynamikumfang eines Delta-Sigma-Konverters. Der Dynamikumfang, das Verhältnis zwischen der Leistung eines gerade noch unverzerrt digitalisierbaren Sinustones und der Rauschleistung, ergibt sich zu:

Je höher die Überabtastung und je größer die Ordnung ist, umso größer ist der Dynamikumfang des Umsetzers.

Vorteilhaft gegenüber anderen AD-Umsetzungsprinzipien ist die hohe Abtastrate des Analogsignals im Vergleich zur Bandbreite des Nutzsignals. Durch diese Überabtastung benötigt ein analoges Bandbegrenzungsfilter, welches zum Einhalten des Nyquist-Shannon-Abtasttheorems erforderlich ist, nur eine geringe Flankensteilheit und kann entsprechend einfach aufgebaut sein. Siehe auch Abschnitt Ordnung im Artikel Filter. Bedingt durch das Wandlungsprinzip mit Integrierer, Rückkopplung und Ausgangsfilter ergibt sich eine vergleichsweise große Signalverzögerungszeit (z. B. das 25-fache[1] des Abtastintervalls der PCM-Daten), die sich mitunter – je nach Anwendung – nachteilig auswirken kann.

Anwendung

Aufgrund seiner Eigenschaften findet er in einer Reihe von Applikationen vorteilhaft Anwendung:

- Im Bereich der Audiosignalverarbeitung hat er andere Umsetzertechniken nahezu vollständig verdrängt. Ausführungen mit einer Signalbandbreite von 100 kHz und einem Signal-Rauschabstand von 120 dB sind seit 2005 kommerziell verfügbar. Der Sigma-Delta-Modulator bildet insbesondere die Grundlage des in der Super Audio Compact Disc verwendeten Direct Stream Digital genannten Kodierungsverfahrens. Dabei wird im Prinzip eine „verteilte“ Analog-Analog-Modulation durchgeführt, wobei bei der Aufnahme das aus dem Quantisierer kommende 1-Bit-Signal (vor dem Filter) auf die SACD aufgezeichnet wird. Erst bei der Wiedergabe wird der Datenstrom von einem analogen Filter zum Ausgangssignal verarbeitet.

- Bei der niederfrequenten Messdatenerfassung kommen spezielle Ausführungen mit Bandbreiten von weniger als 50 Hz in Seismometern, elektronischen Waagen und ähnlichen Geräten zum Einsatz. Diese Umsetzer verfügen meist auch über ein spezielles digitales Filter, welches die Stromnetzfrequenzen von 50 Hz und 60 Hz und deren Oberschwingungen unterdrückt.

- In PLL-Schaltungen zur gebrochen-rationalen Takterzeugung (fractional-N-PLLs) können Sigma-Delta-Modulatoren im Rückkopplungszweig verwendet werden, um zwischen den in fractional-N-PLLs alternierend verwendeten Teilerverhältnissen umzuschalten (sog. MASH). Vorteil von fractional-N-PLLs ist das geringere Phasenrauschen und die für eine gleichbleibende Ausgangsfrequenz höhere maximale Schleifenbandbreite, da ein höherer Referenztakt verwendet werden kann als bei gewöhnlichen PLLs.[2] Die fortlaufende Umschaltung des Teilerverhältnisses bedeutet jedoch eine zusätzliche Quelle für Rauschen. Durch die Steuerung der Umschaltung des Teilerverhältnisses mittels eines Sigma-Delta-Modulators kann jedoch die Eigenschaft des Noise-Shapings benutzt werden, um das zusätzliche Phasenrauschen weg von der Ausgangsfrequenz der fractional-N-PLL zu verschieben, wo es durch die Tiefpasswirkung der PLL gefiltert werden kann.

- Aufgrund der Signalverzögerungszeit eignet sich die Delta-Sigma-Modulation nicht für bestimmte Anwendungen im Bereich der Regelungstechnik.

Siehe auch

Literatur

- System and Circuit Approaches for the Design of Multi-mode Sigma-Delta Modulators with Application for Multi-standard Wireless Receivers. (PDF; 2,3 MB) Dissertation, die u. a. auch die Grundlagen ausführlich darstellt

- Pervez M. Aziz, Henrik V. Sorensen, Jan van der Spiegel: An Overview of Sigma-Delta Converters – How a 1-bit ADC achieves more than 16-bit resolution. (PDF; 2,6 MB) In: IEEE Signal Processing Magazine, Januar 1996, S. 61

Weblinks

- Applet von Analog Devices; Simulation des Verfahrens

- Uwe Beis: Einführung in Delta-Sigma-Modulation.

Einzelnachweise

- Datenblatt CS4390 – 24-Bit, Stereo D/A Converter for Digital Audio (PDF), unter “Delta-Sigma Modulator” (S. 7) sowie “Group Delay” (bei analog characteristics, S. 2)

- Technical Brief SWRA029 - Fractional/Integer-N PLL Basics (PDF; 6,9 MB) Texas Instruments.