Chip-On-Board-Technologie

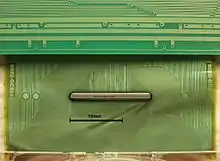

Die Chip-on-Board-Technologie (Abk.: COB, deutsch Nacktchipmontage) ist ein Verfahren zur Direktmontage von ungehäusten Halbleiter-Chips auf Leiterplatten zu einer elektronischen Baugruppe.[1] Heute verwendet man den Begriff COB für alle Baugruppen, die den nackten Halbleiter beinhalten, während man darunter ursprünglich ausschließlich Baugruppen mit Chip-and-Wire-Technik (s. u.) verstand.

Montagevarianten

Bei der Montage von ungehäusten Halbleiter-Chips werden zwei Varianten unterschieden:

- Direct Chip Attach – der Chip wird direkt auf dem Substrat befestigt;

- Tape-Automated Bonding – der Chip wird auf einen Zwischenträger vormontiert, der bei der fertig zusammengefügten Baugruppe die Verbindung zum Substrat herstellt.

Die erste Montagevariante Direct Chip Attach, also die direkte Montage des ungehäusten Halbleiter-Chips auf den Verdrahtungsträger, kann mithilfe folgender Techniken erfolgen:

- Chip-and-Wire-Technik: der Chip wird direkt auf die Leiterplatte geklebt und mittels Drahtbonden (Brücken aus feinem Draht) mit der Leiterplatte elektrisch verbunden. Dabei befinden sich die Kontaktflächen des Chips von der Leiterplatte abgewandt.

- Flip-Chip-Montage: vorher auf die Kontaktflächen des Chips aufgebrachte Lotkugeln oder leitfähige Kunststoffhügel helfen, den Chip mit dem Verdrahtungsträger elektrisch und mechanisch zu verbinden. Die Kontakte des Chips sind dabei der Leiterplatte zugewandt.[1]

Arbeitsschritte bei der Direktmontage mittels Chip-and-Wire-Technik:

- Chipbonden: Bezeichnet das Bestücken und Kleben solcher Bauteile auf den Träger.

- Drahtbonden: Das Herstellen der Drahtverbindungen (aus Gold, Aluminium, seltener Palladium, Kupfer) vom Chip zum Träger (z. B. starre oder flexible Leiterplatte, Keramik- oder Glassubstrat).

- optional das Vergießen der kontaktierten Chips (engl. glob top), um ihn und die Bonddrähte zu schützen.

Bei der zweiten Variante, Tape Automated Bonding, wird der Chip auf einem Zwischenverdrahtungsträger vormontiert und mit diesem zusammen auf der Leiterplatte montiert.[1]

Vor- und Nachteile

Der Hauptvorteil dieses Verfahrens sind die geringeren Kosten bei der Massenproduktion. Eine höhere Taktfrequenz aufgrund von kürzeren Wegen zwischen Chip und Leiterplatte kann möglich sein. Weiterhin kommt es zu einer besseren thermischen Anbindung zwischen dem Chip und der Leiterplatte, hierbei trägt das Vergussmaterial ebenfalls zur Wärmeableitung auf die Leiterplatte bei. Im Vergleich zu Chips im Gehäuse wird weniger Platz benötigt, damit geht eine höhere Bauteildichte auf der Leiterplatte und deren preiswertere Herstellung einher. Bei Scanner-Sensoren wird das Verfahren angewendet, weil nur so die langgestreckten CCD-Fotoempfänger-Chips bündig aneinandergereiht werden können.

Nachteil ist die fehlende Möglichkeit einer Reparatur, d. h., defekte Chips können nicht ohne erheblichen Aufwand getauscht werden. Der Verdrahtungsträger muss zum Drahtbonden geeignete Oberflächen besitzen; oft ist das eine Vergoldung. Weiterhin ist das Verfahren schlecht mit den konventionellen Lötverfahren kombinierbar, bzw. es erfordert einen weiteren, ganz anders ausgerüsteten Montage-Arbeitsgang.

Anwendung

Anwendung findet die Chip-on-Board-Technologie in Großserien (z. B. Uhren, Taschenrechner, LED-Leuchtmittel wie LED-Leuchtfaden).

Der Anteil der mithilfe der Chip-on-Board-Technologie gefertigten elektronischen Baugruppen an allen weltweit gefertigten Baugruppen betrug im Jahr 1995 etwa 0,1 %.[2] Es gab 1996 Prognosen, im Jahr 2000 würden 15 % aller hergestellten integrierten Schaltkreise mittels der Chip-on-Board-Technik montiert.[3]

Weblinks

Einzelnachweise

- Wolfgang Scheel (Hrsg.): Baugruppentechnologie der Elektronik – Montage. 2. Auflage. Verlag Technik, Berlin 1999, ISBN 3-341-01234-6, S. 13.

- „The National Technology Roadmap For Electronic Interconnections. PC 1995“ zitiert In: Wolfgang Scheel (Hrsg.): Baugruppentechnologie der Elektronik – Montage. 2. Auflage. Verlag Technik, Berlin 1999, ISBN 3-341-01234-6, S. 12/13.

- E. Meusel und B. Lauterwakd: Nacktchipverarbeitung durch Löten – Trends und technologische Probleme. In: DVS-Berichte Band 182: Weichlöten in Forschung und Praxis 1996. 1996, S. 1